系列文章目录

第一章 计算系统概论

第二章 运算方法和运算器

第三章 多层次的存储器

第四章 指令系统

第五章 中央处理器

第六章 总线系统

第七章 外围设备

第八章 输入输出系统

文章目录

前言

【 第二章 运算方法和运算器 】

2.1 数据与文字的表示

- 计算机中使用的数据可分成两大类:

- 符号数据:非数字符号的表示(ASCII、汉字、图形等)

- 数值数据:数字数据的表示方式(定点、浮点)

- 计算机数字和字符的表示方法应有利于数据的存储、加工(处理)、传送;

- 编码:用少量、简单的基本符号,选择合适的规则表示尽量多的信息,同时利于信息处理(速度、方便)

2.1.1数据格式

一、定点表示法

- 所有数据的小数点位置固定不变

- 理论上位置可以任意,但实际上将数据表示有两种方法: 纯小数、纯整数

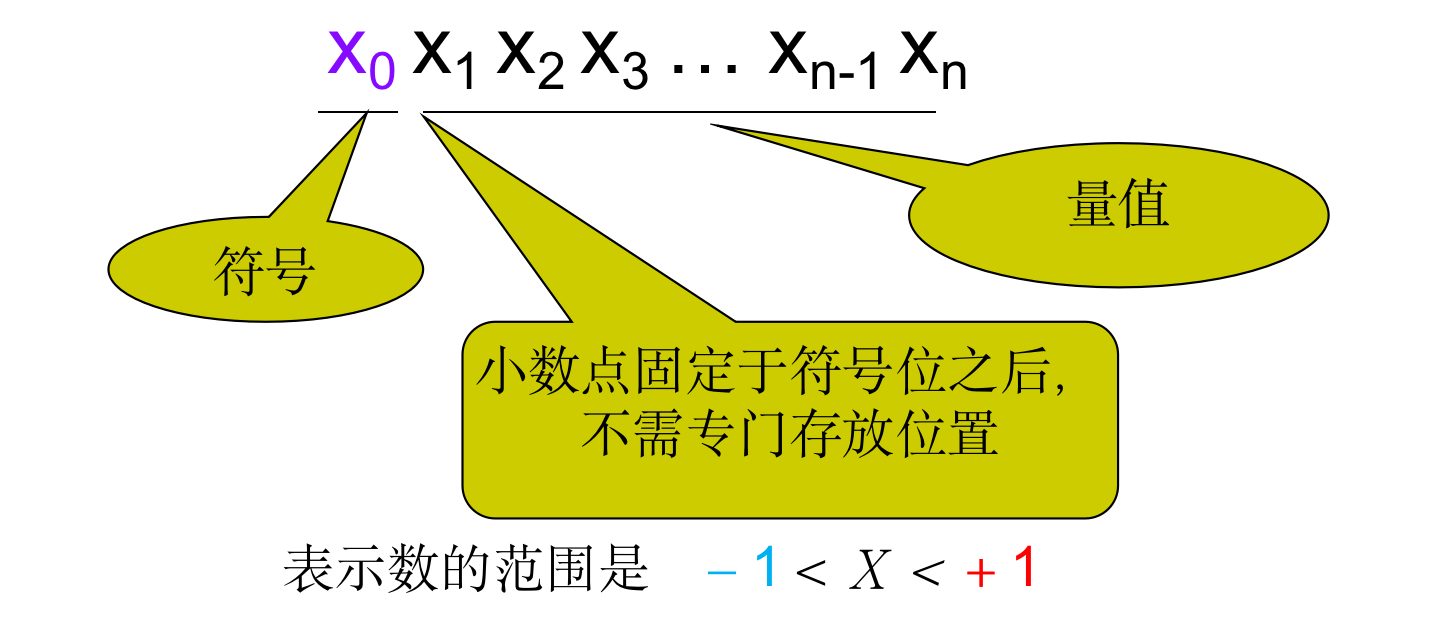

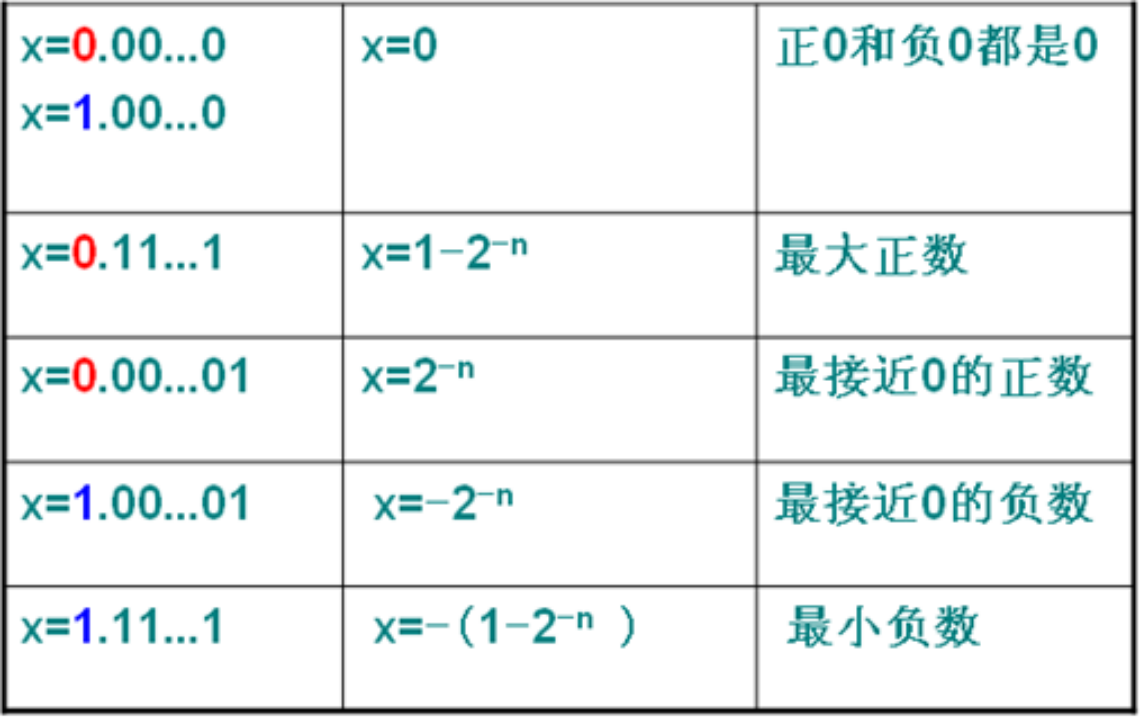

- 定点纯小数:

- 纯小数表示范围

- 纯小数表示范围

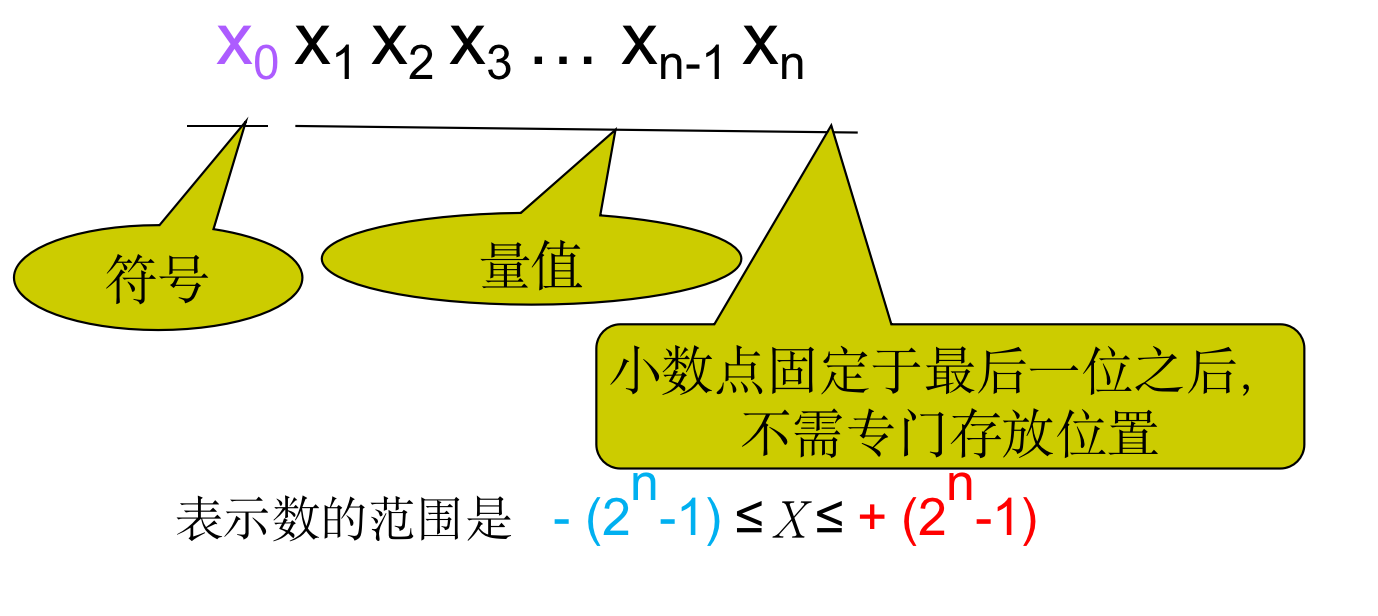

- 定点纯整数:

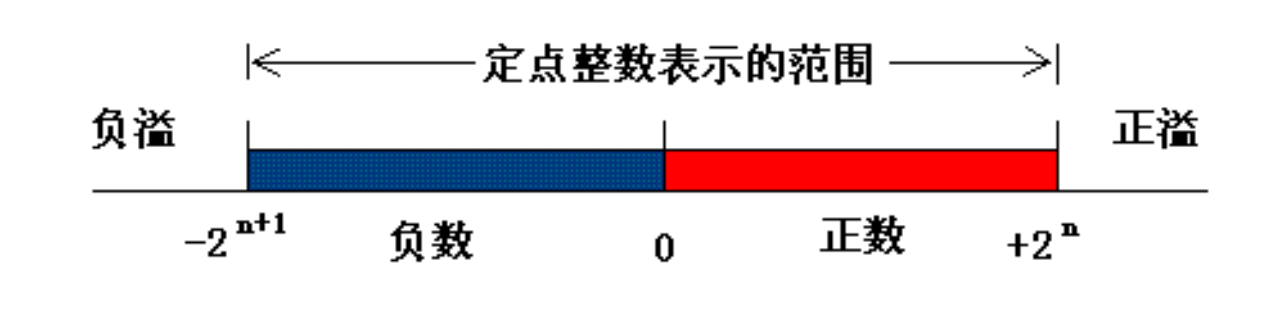

- 定点表示法的特点

- 定点数表示数的范围受字长限制,表示数的范围有限;

- 定点表示的精度有限

- 机器中,常用定点纯整数表示;

2、浮点表示法:数点位置随阶码不同而浮动

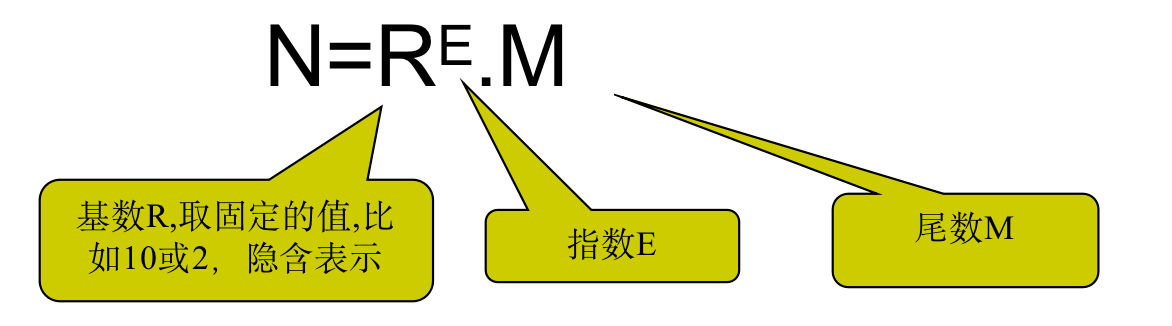

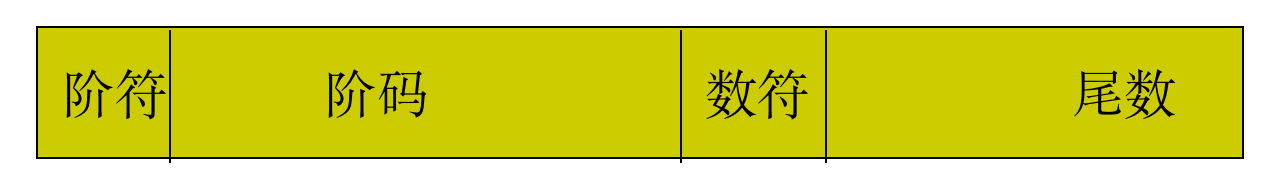

- 格式:N=RE.M

- 机器中表示

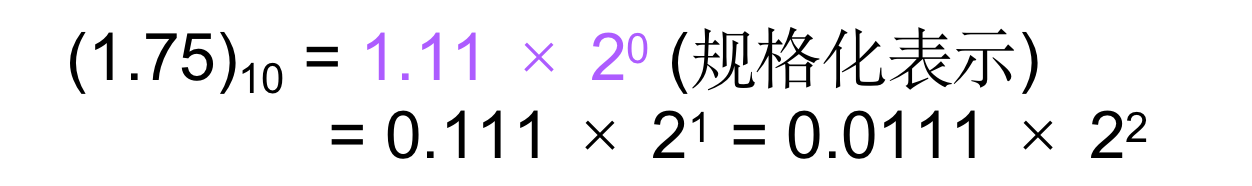

- 浮点数规格化表示:

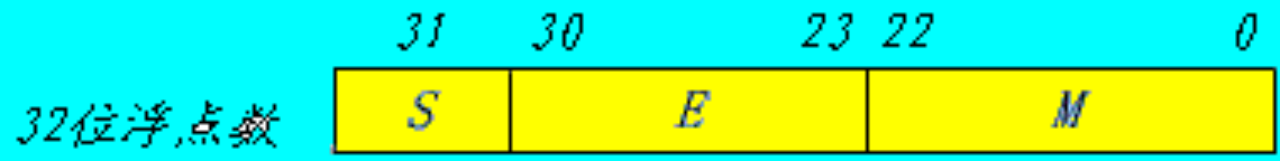

3、IEEE754标准(规定了浮点数的表示格式,运算规则等)

- 规则规定了单精度(32)和双精度(64)的基本格式.

- 规则中,尾数用原码,指数用移码(便于对阶和比较)

- IEEE754标准

- 基数R=2,基数固定,采用隐含方式来表示它。

- 32位的浮点数:

- S数的符号位,1位,在最高位,“0”表示正数,“1”表示负数。

- M是尾数, 23位,在低位部分,采用纯小数表示

- E是阶码,8位,采用移码表示。移码比较大小方便。

- 规格化: 若不对浮点数的表示作出明确规定,同一个浮点数的表示就不是惟一的。

- 尾数域最左位(最高有效位)总是1, 故这一位经常不予存储,而认为隐藏在小数点的左边。

- 采用这种方式时,将浮点数的指数真值e变成阶码E时,应将指数e加上一个固定的偏移值127(01111111),即E=e+127。

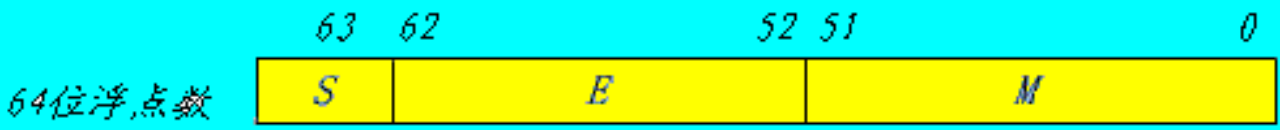

- 64位的浮点数中符号位1位,阶码域11位,尾数域52位,指数偏移值是1023。因此规格化的64位浮点数x的真值为:

- x=(-1)S×(1.M)×2E-1023

- e=E-1023

- 一个规格化的32位浮点数x的真值表示为

- x=(-1)S×(1.M)×2E-127

- e=E-127

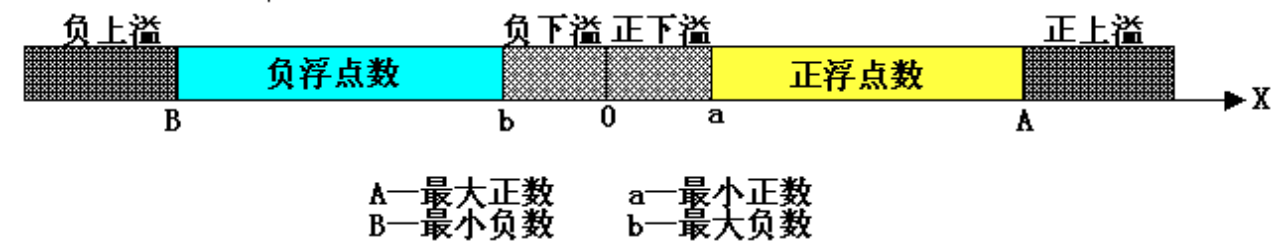

- 真值x为零表示:当阶码E为全0且尾数M也为全0时的值,结合符号位S为0或1,有正零和负零之分。

- 真值x为无穷大表示:当阶码E为全1且尾数M为全0时,结合符号位S为0或1,也有+∞和-∞之分。

- 这样在32位浮点数表示中,要除去E用全0和全1(25510)表示零和无穷大的特殊情况,指数的偏移值不选128(10000000),而选127(01111111)。对于规格化浮点数,E的范围变为1到254,真正的指数值e则为-126到+127。因此32位浮点数表示的绝对值的范围是10-38~1038(以10的幂表示)。

- 浮点数所表示的范围远比定点数大。一台计算机中究竟采用定点表示还是浮点表示,要根据计算机的使用条件来确定。一般在高档微机以上的计算机中同时采用定点、浮点表示,由使用者进行选择。而单片机中多采用定点表示。

- 浮点数表示范围:

2.1.2数的机器码表示

- 真值:一般书写的数

- 机器码:为了处理符号位如何表示、是否同数值一起计算等问题,将符号位与数值位一起编码来表示相应的数。

- 原码、反码、补码、移码

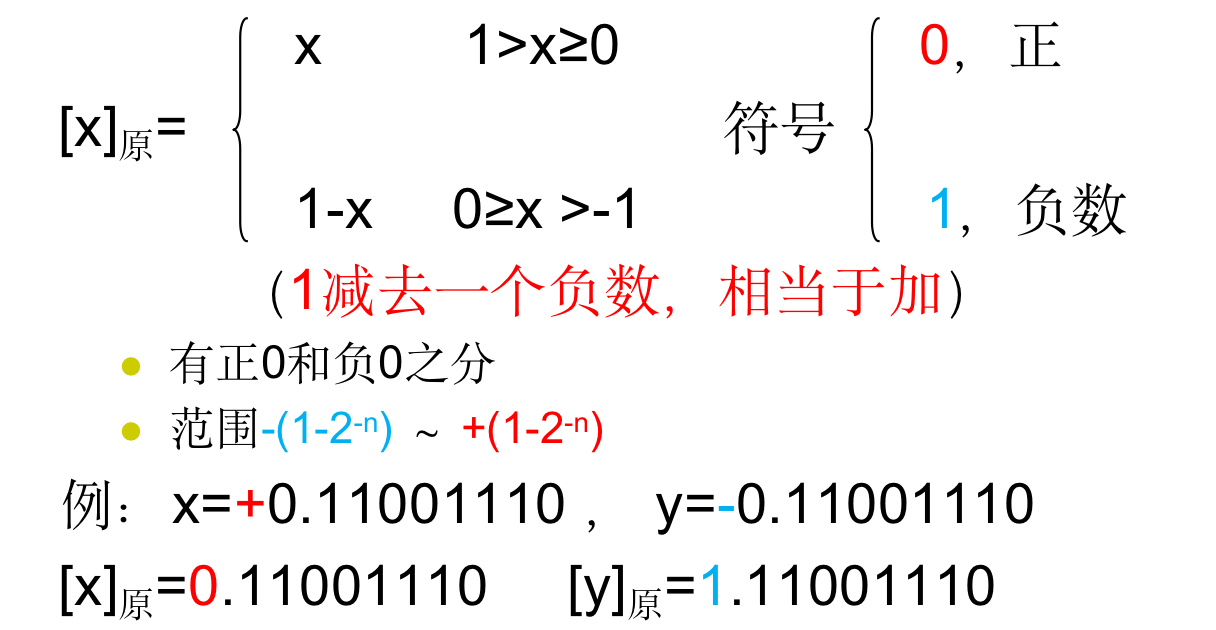

1、原码表示法

- 定点小数x0. x1x2…xn

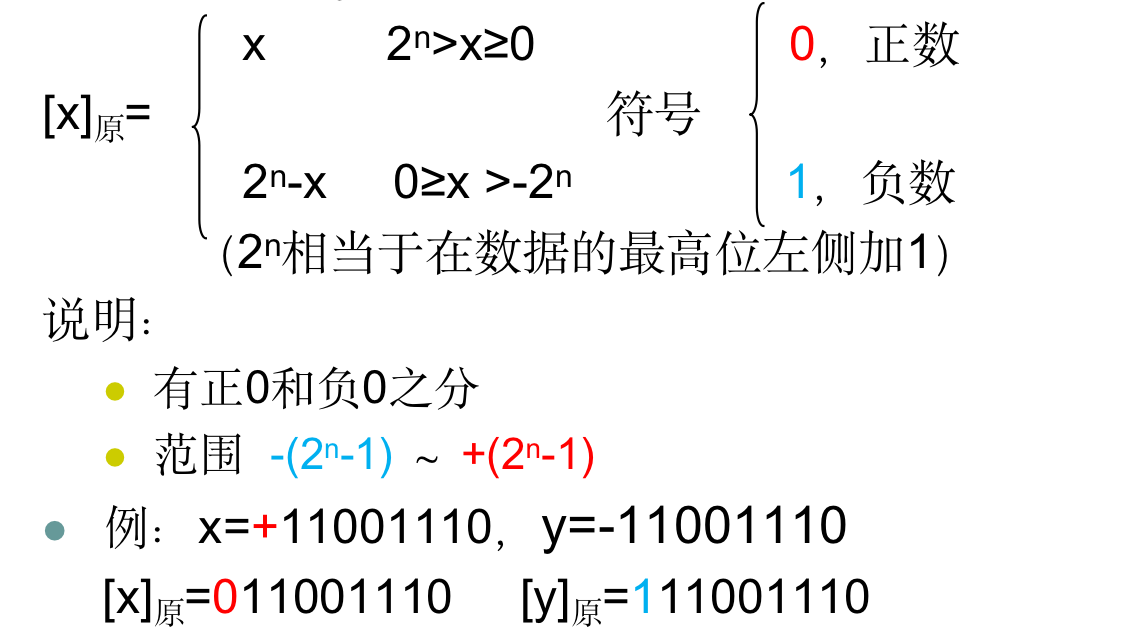

- 定点整数X0X1X2…Xn

- 原码特点:

- 表示简单,实现乘除运算规则简单。

- 进行加减运算十分麻烦 P20。

2、补码表示法

- 生活例子:现为北京时间下午4点,但钟表显示为7点。有两种办法校对:

- 做减法 7-3 = 4 (逆时针退3格)

- 做加法 7+9 = 16 (顺时针进9格)16 (mod 12) = 16-12 = 4 (以12为模,变成4)

- 定义:正数的补码就是正数的本身,负数的补码是原负数加上模。

- 计算机运算受字长限制,属于有模运算.

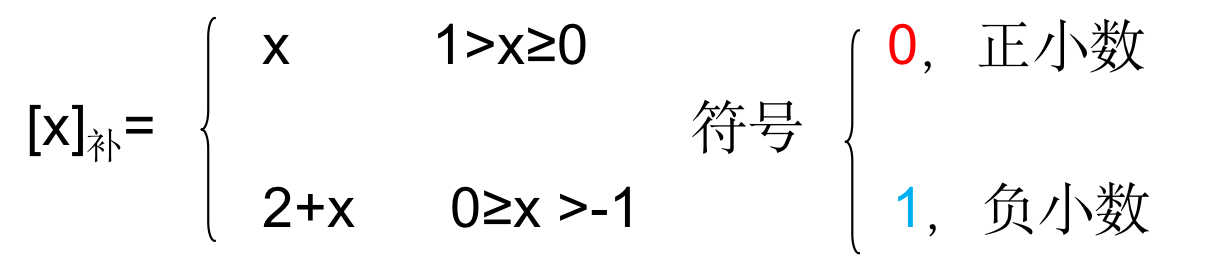

- 定点小数x0.x1x2…xn,以2为模

- 定点整数x0.x1x2…xn,以2n+1为模

- 定点小数x0.x1x2…xn

- 定点整数x0.x1x2…xn

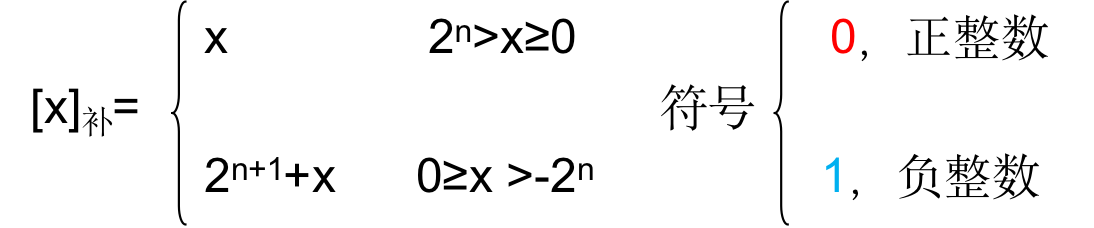

3、反码表示法

- 定义:正数的表示与原、补码相同,负数的补码符号位为1,数值位是将原码的数值按位取反,就得到该数的反码表示。

- 电路容易实现,触发器的输出有正负之分。

- 对尾数求反,它跟补码的区别在于末位少加一个1,所以可以推出反码的定义

- 定点小数x0.x1x2…xn

- [x ]补=[x ]反+2-n(证明见书)

- 反码表示有正0和负0之分

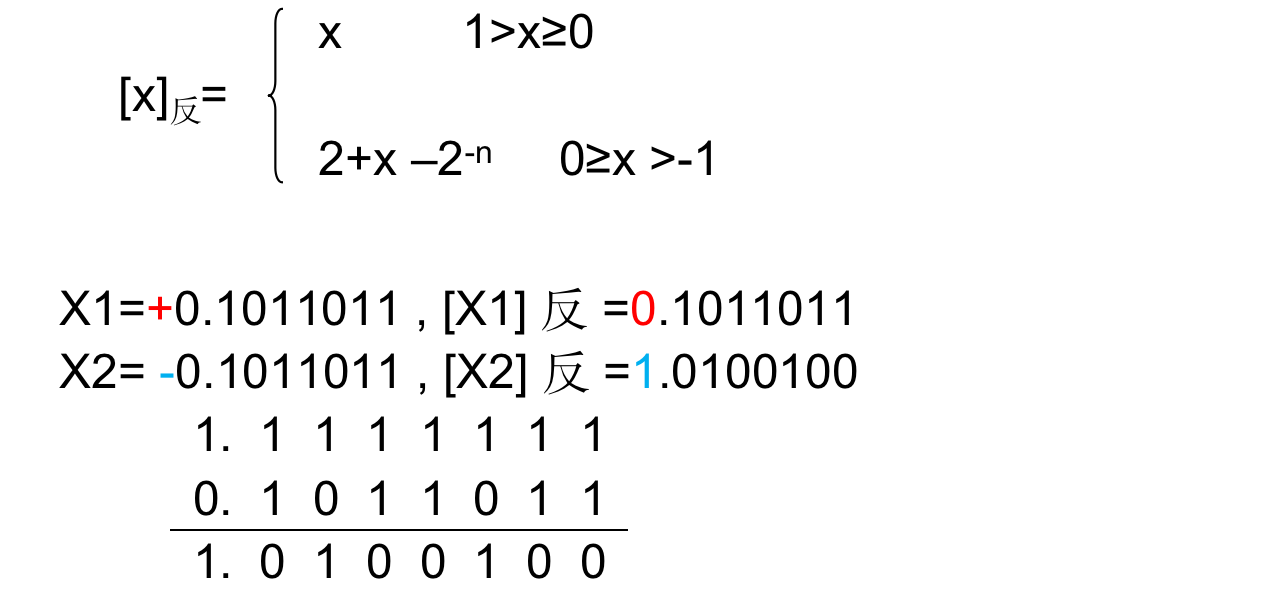

4、移码表示法

- 移码表示法(用在阶码中)

- 定点整数定义 [x]移=2n+x 2n >x≥-2n

- 00000000 - 11111111( -2n~2n-1 )

- 例1 x=+1011111

- 原码为01011111

- 补码为01011111

- 反码为01011111

- 移码为11011111

- 例2 x=-1011111

- 原码为11011111

- 补码为10100001

- 反码为10100000

- 移码为00100001

- 特点:移码和补码尾数相同,符号位相反

- 范围:-2n~2n-1

- 浮点IEEE754表示e=-127~+128

- 00000000阶码表示数字”0”,尾数的隐含位为0

- 11111111阶码表示数字”无穷大” ,尾数的隐含位为0

2.1.3字符与字符串的表示方法

- 符号数据:字符信息用数据表示,如ASCII等;

- 字符表示方法ASCII:用一个字节来表示,低7位用来编码(128),最高位为校验位,参见教材P24表2.1

- 字符串的存放方法

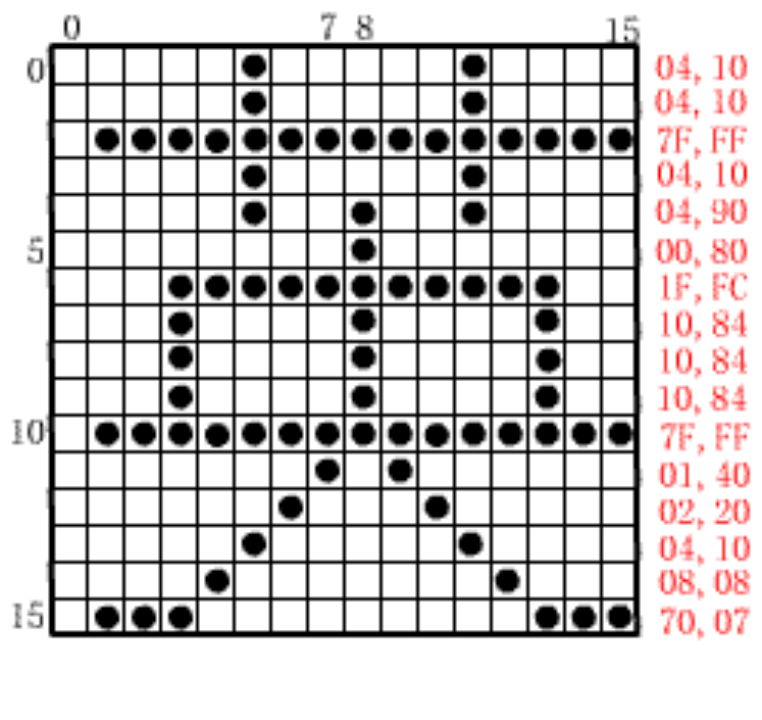

2.1.4汉字的表示方法

-

汉字的表示方法(一级汉字3755个,二级汉字3008个)

- 输入码

- 国标码:一级(16-55)* 94;二级(56-87)*94;图形符号(682个)(01~09)*94

- 拼音、五笔

- 汉字内码:汉字信息的存储,交换和检索的机内代码,两个字节组成,每个字节高位都为1(区别于英文字符)

- 输入码

-

汉字字模码:汉字字形

-

点阵

-

汉字库

2.1.5校验码

- 校验码(只介绍奇偶校验码)

- 引入:信息传输和处理过程中受到干扰和故障,容易出错。

- 解决方法:是在有效信息中加入一些冗余信息(校验位)

- 奇偶校验位定义

- 设x=(x0x1…xn-1)是一个n位字,则奇校验位C定义为:C=x0⊕x1⊕…⊕xn-1,式中⊕代表按位加,表明只有当x中包含有奇数个1时,才使C=1,即C =0。同理可以定义偶校验。

- 只能检查出奇数位错;不能纠正错误。

- p26例10自己看

- 其它还有Hamming,CRC

2.2 定点加法、减法运算

2.2.1 补码加法

- [x+y]补=[x]补+[y]补 (mod 2n+1)

2.2.2 补码减法

- [x-y]补= [x]补 - [y]补 = [x]补 + [-y]补

- [-y]补 = -[y]补 + 2-n P28

2.2.3 溢出概念与检测方法

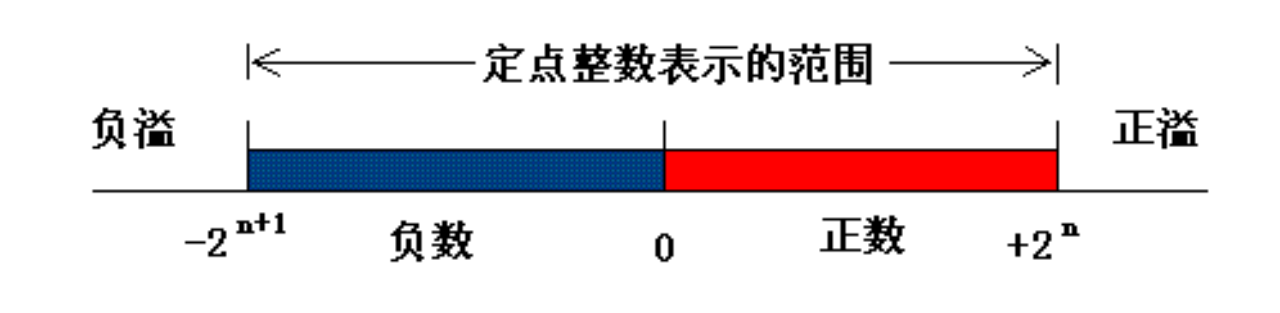

溢出的概念

- 可能产生溢出的情况

- 两正数加,变负数,正溢(大于机器所能表示的最大数)

- 两负数加,变正数,负溢(小于机器所能表示的最小数)

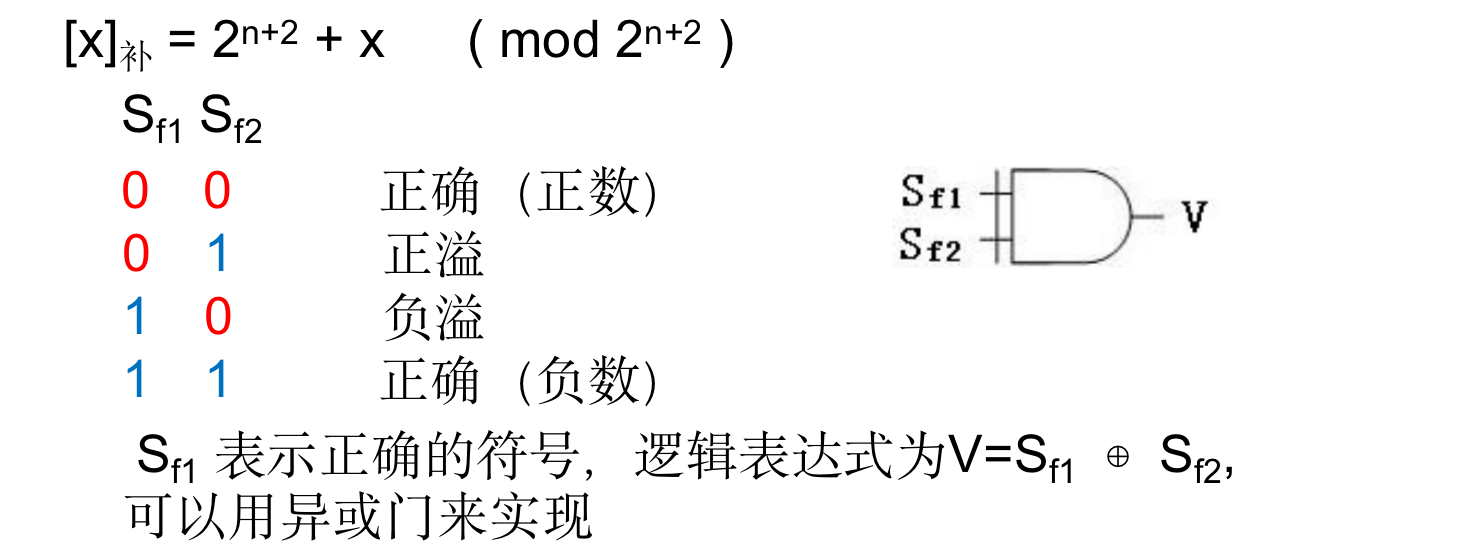

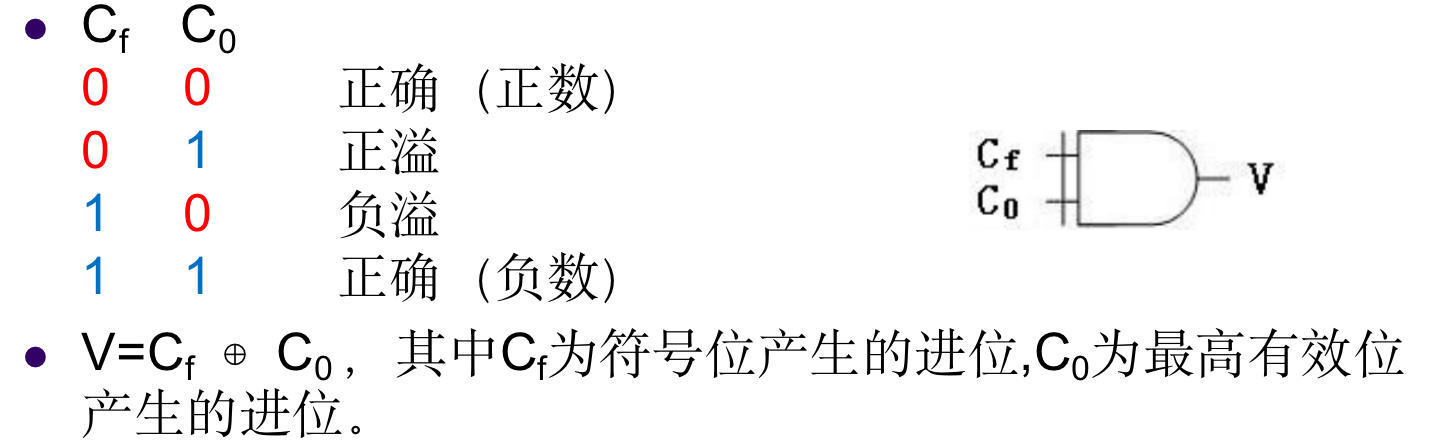

检测方法

- 双符号位法(变形补码)

- 单符号位法

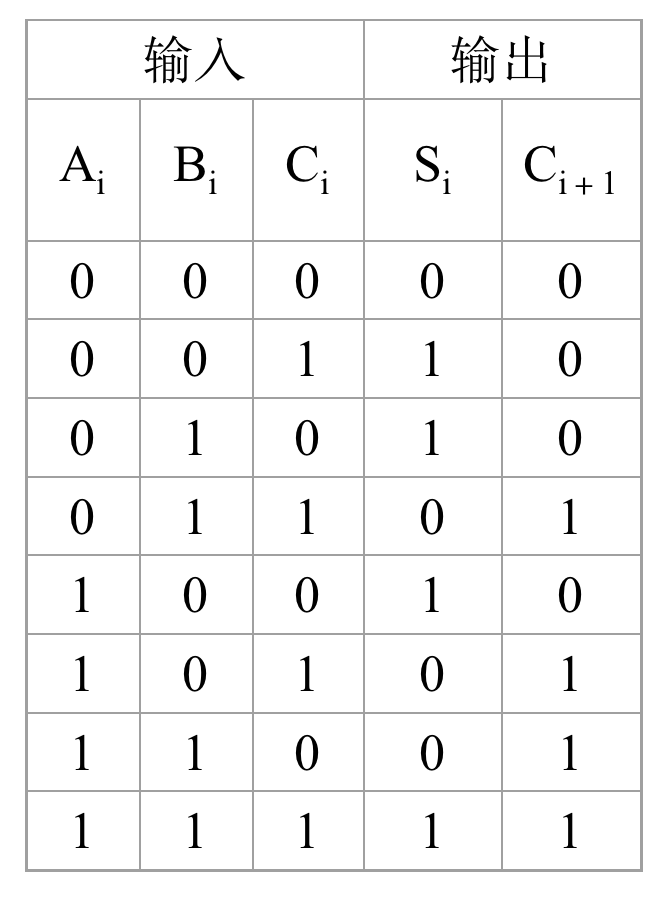

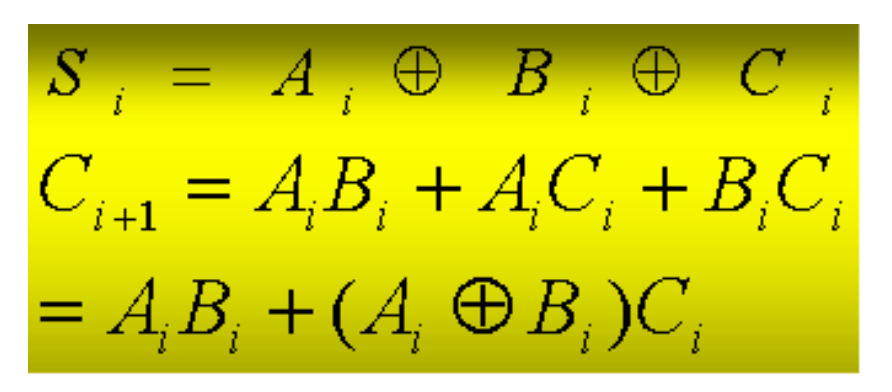

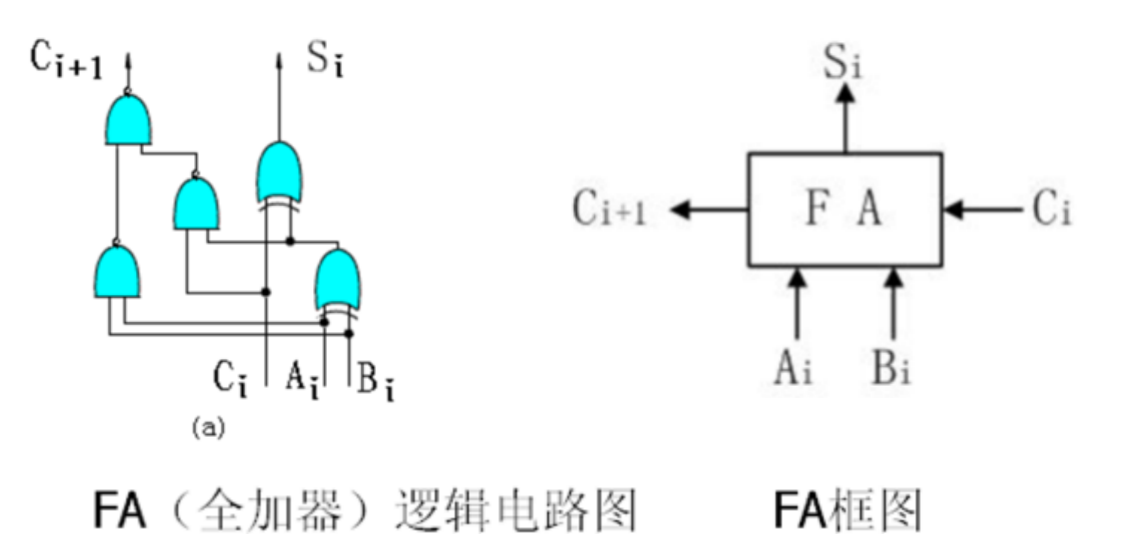

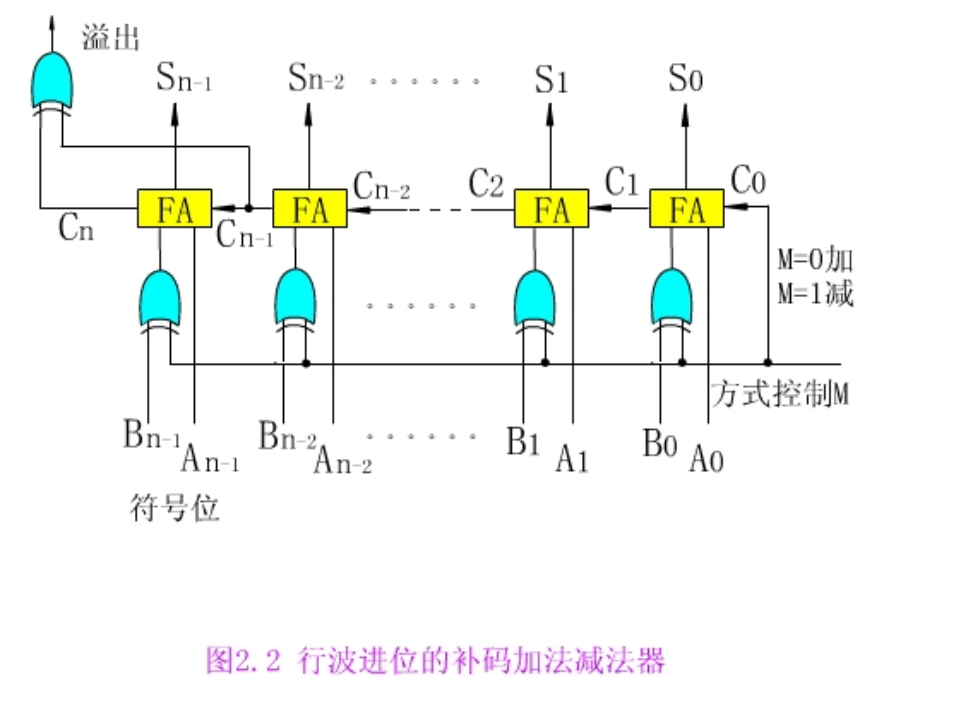

2.2.4 基本的二进制加法/减法器

- 一位全加器真值表

- FA逻辑方程

- FA逻辑电路和框图

- n位行波进位加法器

2.3定点乘法运算

2.3.1 原码并行乘法

1、人工算法与机器算法的同异性

- [x]原=xf.xn-1…x1x0 [y]原=yf.yn-1…y1y0

- [x.y]原=(xf ⊕ yf)+(xn-1…x1x0).(yn-1…y1y0)

- n位乘n位积可能为2n位(包含最高位的进位).

- 乘积的最后是所有部分积之和

- 采用流水式阵列乘法器,取代串行方案。

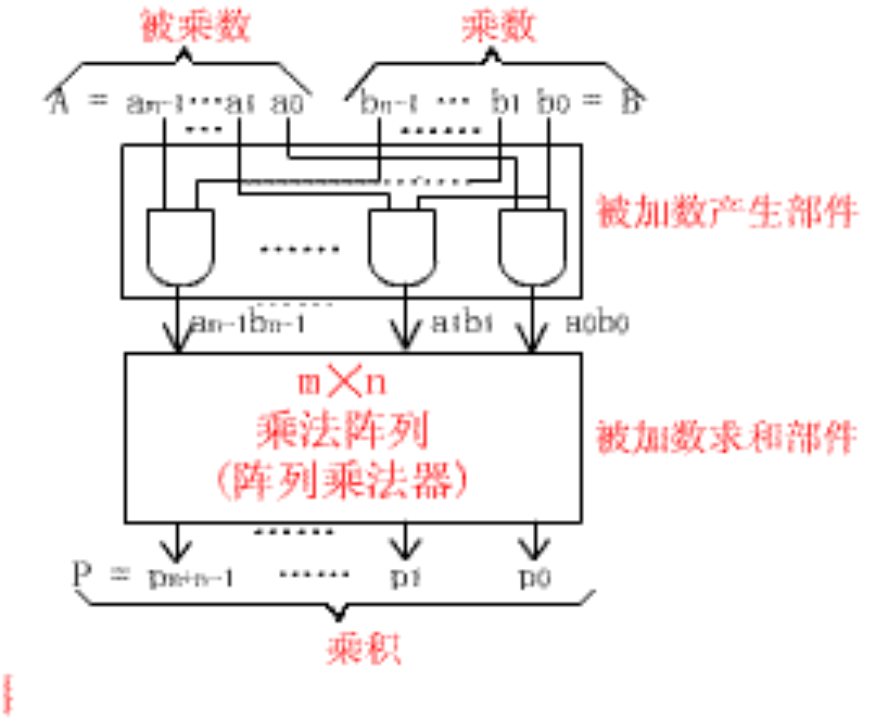

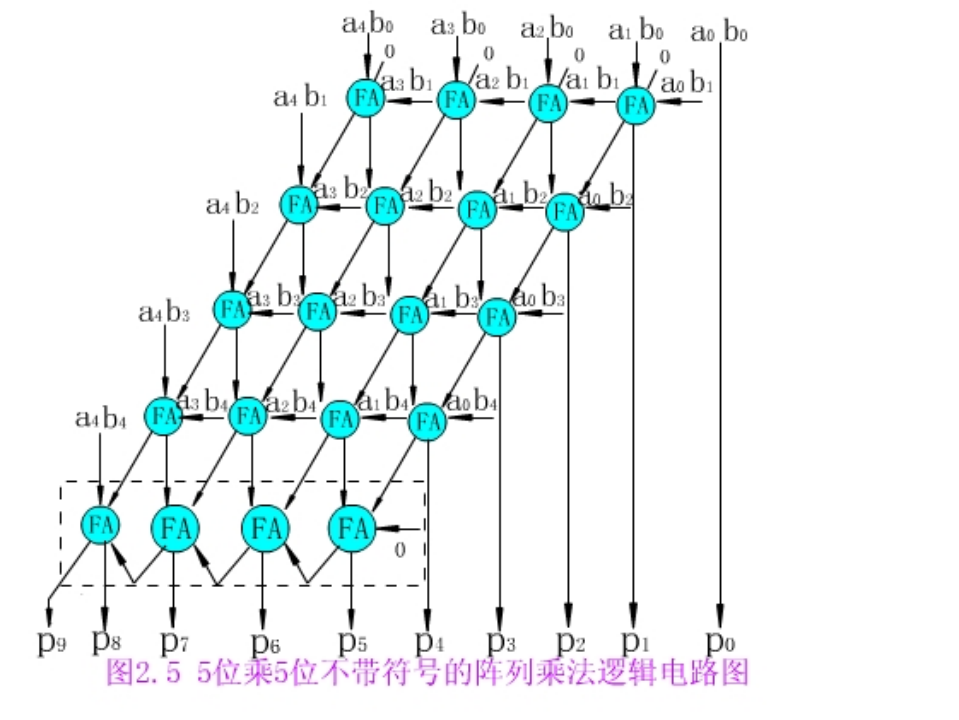

2、不带符号的阵列乘法器

- 不带符号阵列乘法器逻辑图

- 5x5位不带符号的阵列乘法逻辑电路图

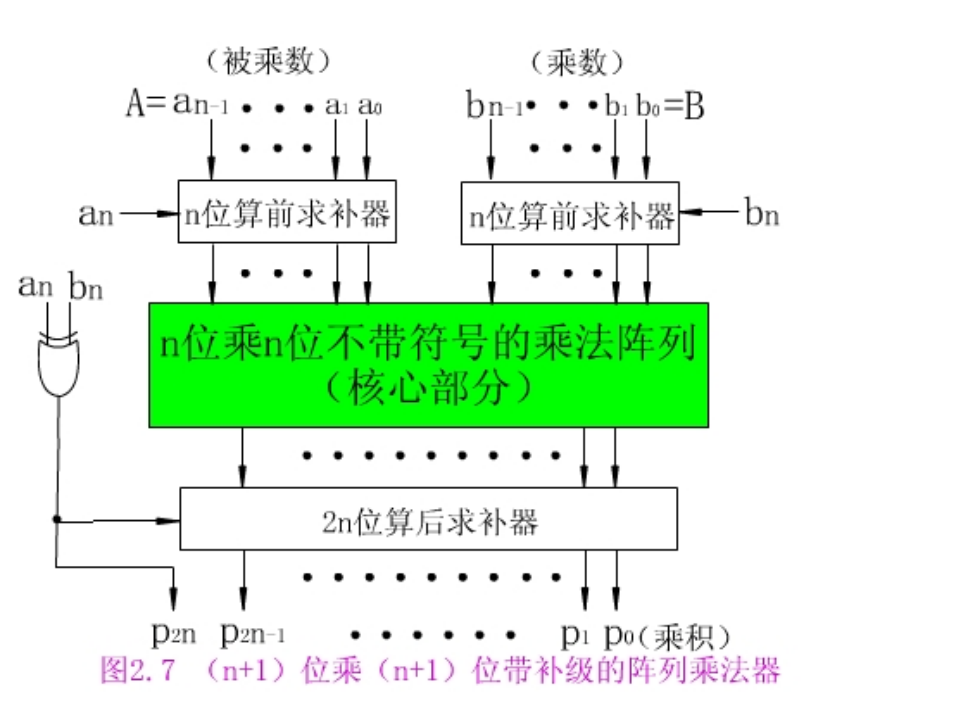

3、带符号的阵列乘法器

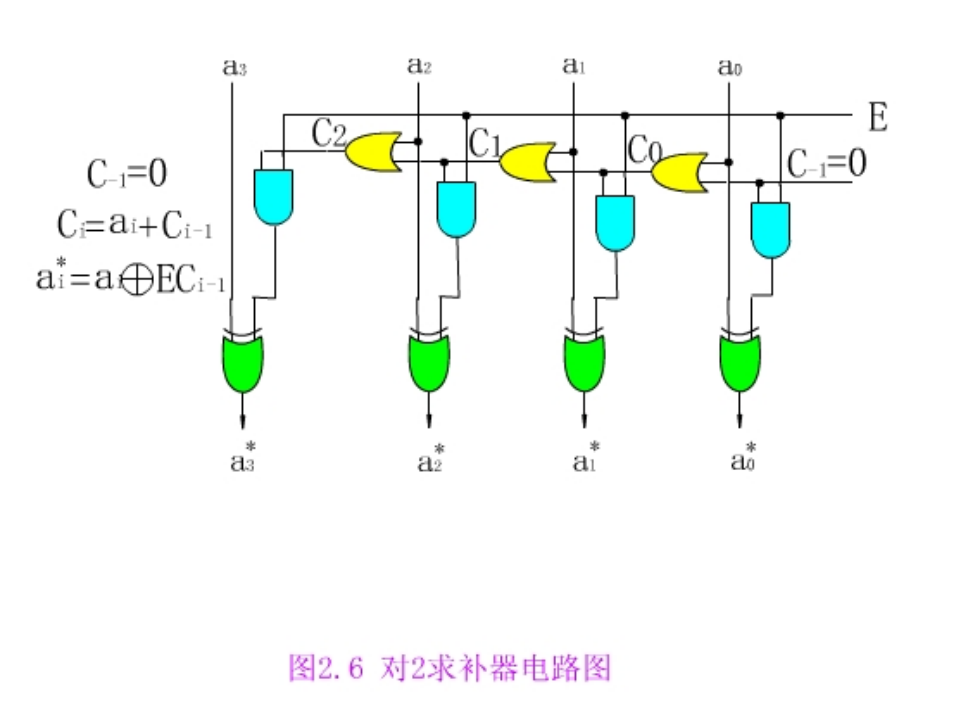

-

求补电路

- 原理:算前求补-乘法器-算后求补,见下图

- 原理:算前求补-乘法器-算后求补,见下图

-

求补电路小结

-

E=0时,输入和输出相等

-

E=1时,则从数最右端往左边扫描,直到第一个1的时候,该位和右边各位保持不变,左边各数值位按位取反

-

可以用符号作为E 的输入

-

原:1.11110 补:1.000 10 (不变,左边数值位取反)

2.3.2 直接补码并行乘法

(暂无)

2.4 定点除法运算

- 设有n位定点小数(定点整数也适用)

- 被除数x,[x]原=xf.xn-1…x1x0

- 除数y, [y]原=yf.yn-1…y1y0

- 则有商q=x/y ,[q]原=(xf⊕yf)+(0.xn-1…x1x0/0.yn-1…y1y0)

- 商的符号运算qf=xf⊕yf与原码乘法一样,用模2求和得到。

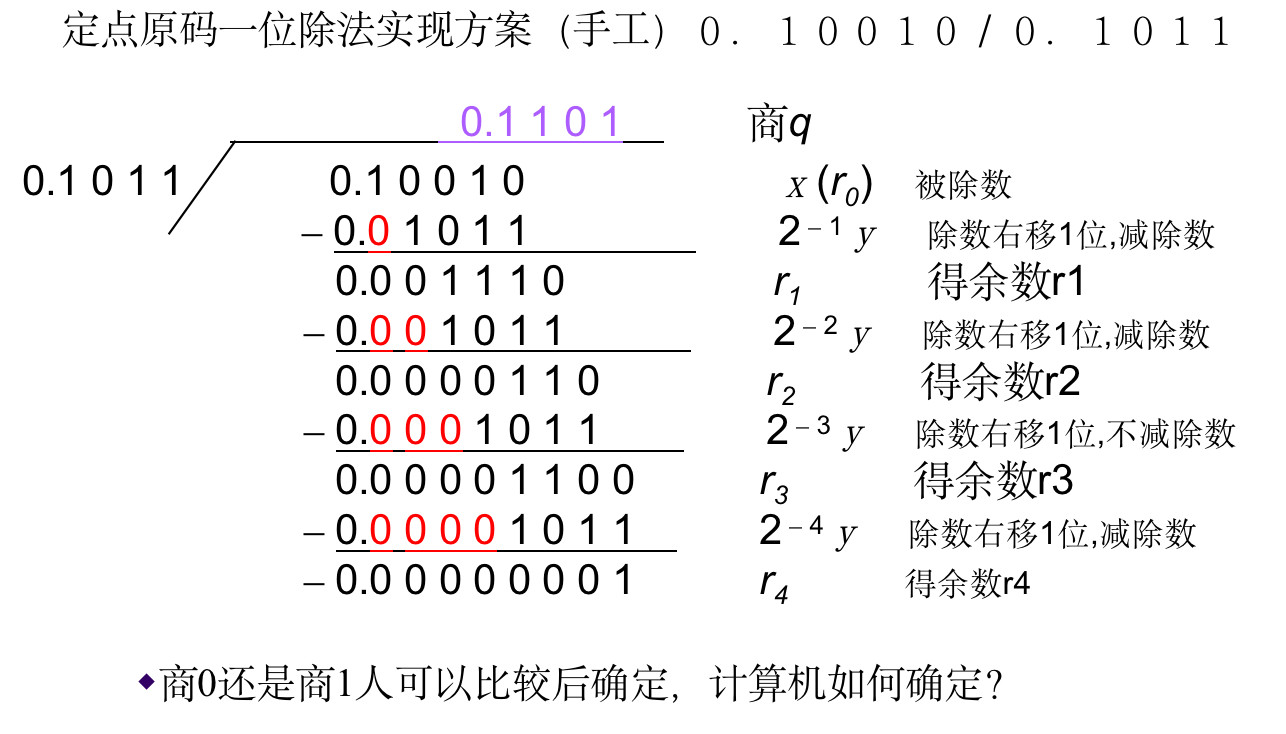

2.4.1 原码除法算法原理

1、定点原码除法

2、不恢复余数的除法

- 人工除法时,人可以比较被除数(余数)和除数的大小来确定商1(够减)或商0(不够减)

- 机器除法时,余数为正表示够减,余数为负表示不够减。

- 不够减时必须恢复原来余数,才能继续向下运算。

- 这种方法叫恢复余数法,控制比较复杂。

- 不恢复余数法(加减交替法)

- 余数为正,商1,下次除数右移做减法;

- 余数为负,商0,下次除数右移做加法。

- 控制简单,有规律。

2.4.2 并行除法器

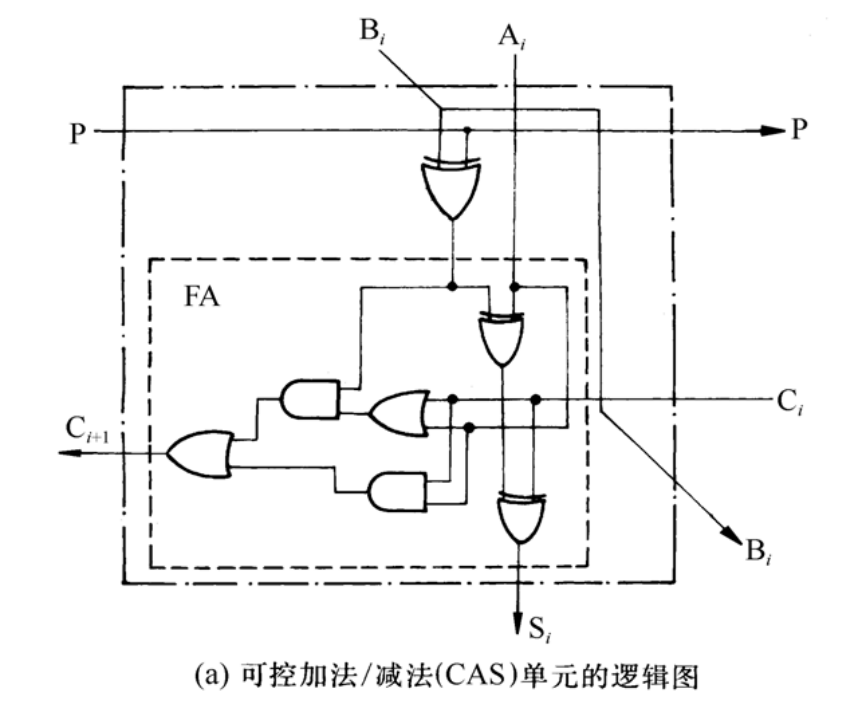

1、可控加法/减法(CAS)单元

- 原理:采用不恢复余数(加减交替)法

- P=0,作加法运算

- P=1,作减法运算

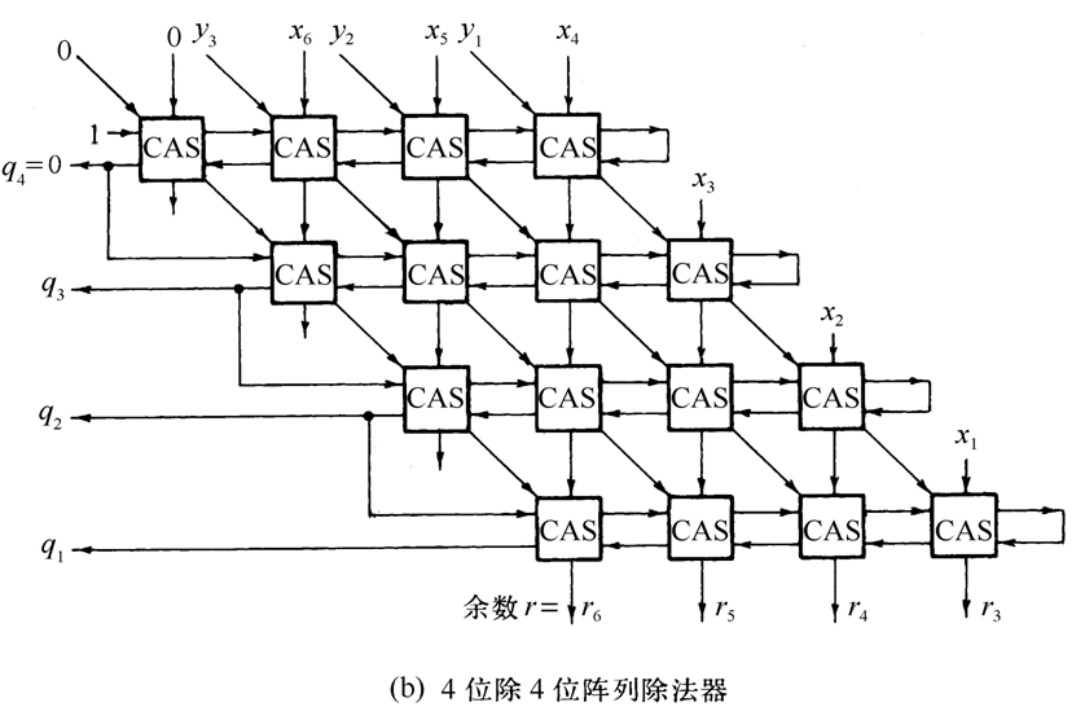

2、不恢复余数的阵列除法器

- 被除数 x=0.x6x5x4x3x2x1(双倍长)

- 除数 y=0.y3y2y1

- 商数 q=0.q3q2q1

- 余数 r=0.00r6r5r4r3

- 除数右移

2.5 定点运算器的组成

2.5.1 逻辑运算

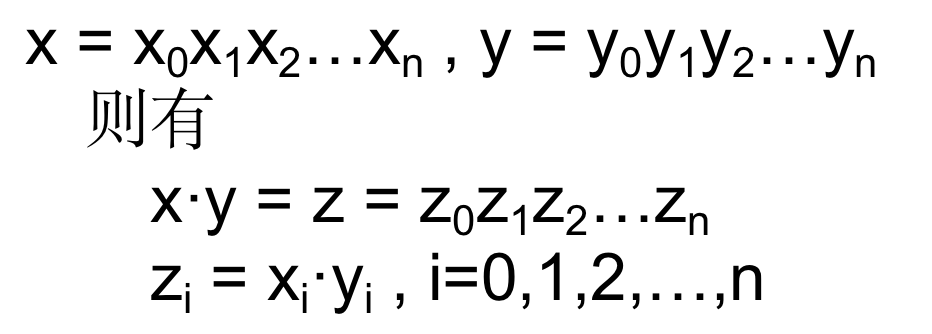

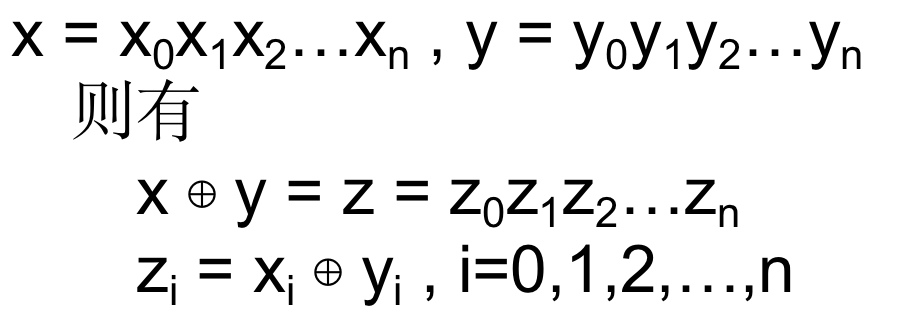

- 逻辑非运算

- 逻辑加运算

- 逻辑乘运算

- 逻辑异运算

2.5.2 多功能算术/逻辑运算单元ALU

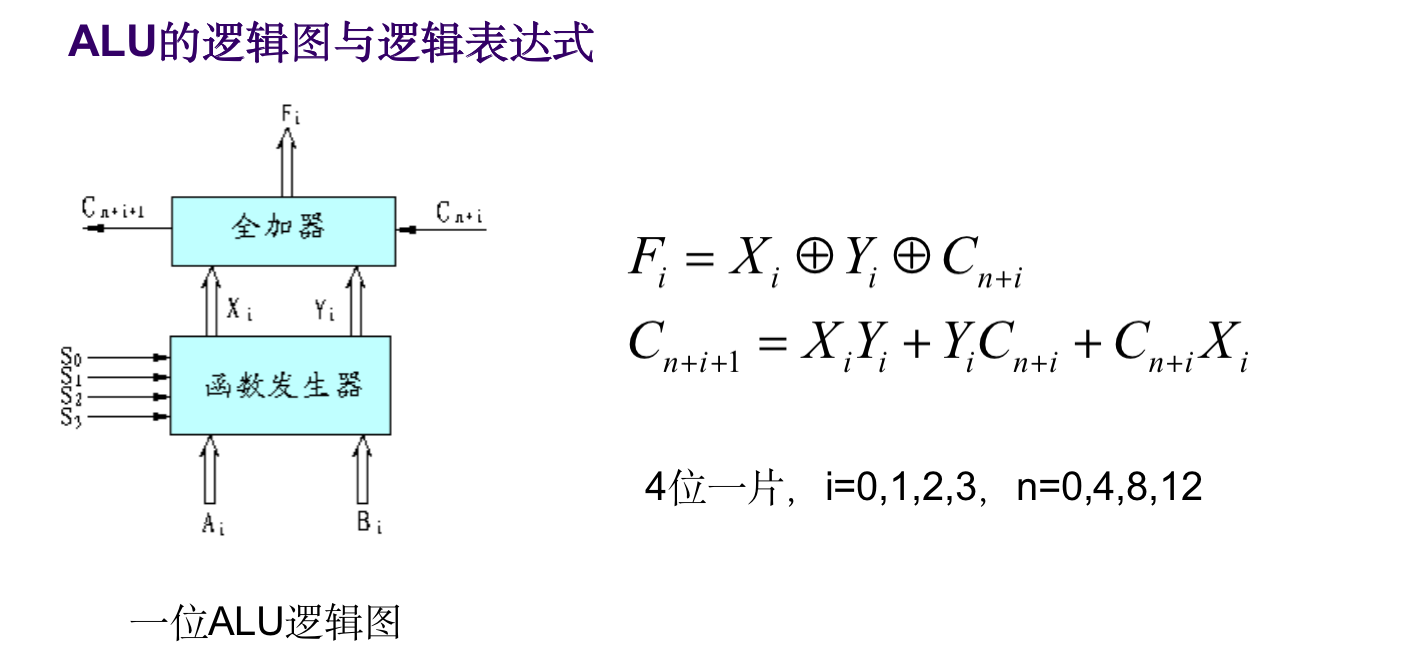

1、基本思想

- 创新点:

- 实现并行进位(先行进位)

- 实现16种算术运算,16种逻辑运算

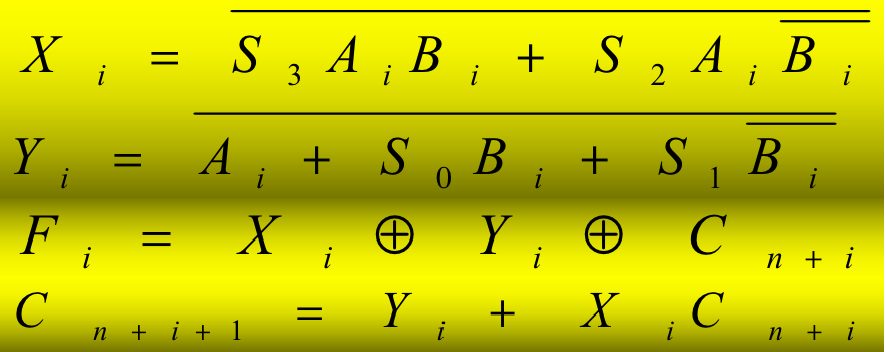

- 基本思想:一位全加器FA的逻辑表达式:

- 为了实现多种算术逻辑运算,可将Ai和Bi输入一个函数发生器(进位传递函数和进位产生函数)得到输出Xi和Yi,作为一位全加器的输入(见下页图)。

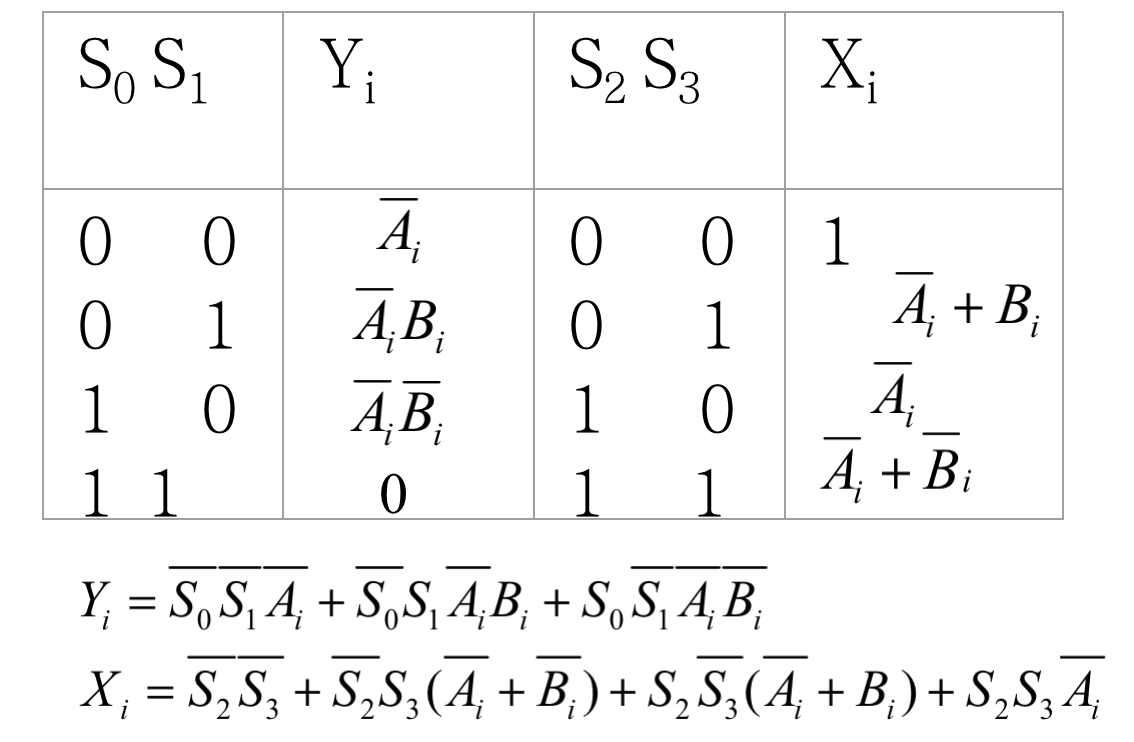

2、逻辑表达式

- XiYi 与控制参数和输入量的关系构造如下真值表

- ALU的某一位逻辑表达式见下:

- 如何实现先行进位?

- 令G=Y3+Y2X3+Y1X2X3+Y0X1X2X3 P=X0X1X2X3

- G为进位发生输出 P为进位传送输出

- 增加P和G的目的在于实现多片(组)ALU之间的先行进位,需要配合电路,称为先行进位发生器(CLA)

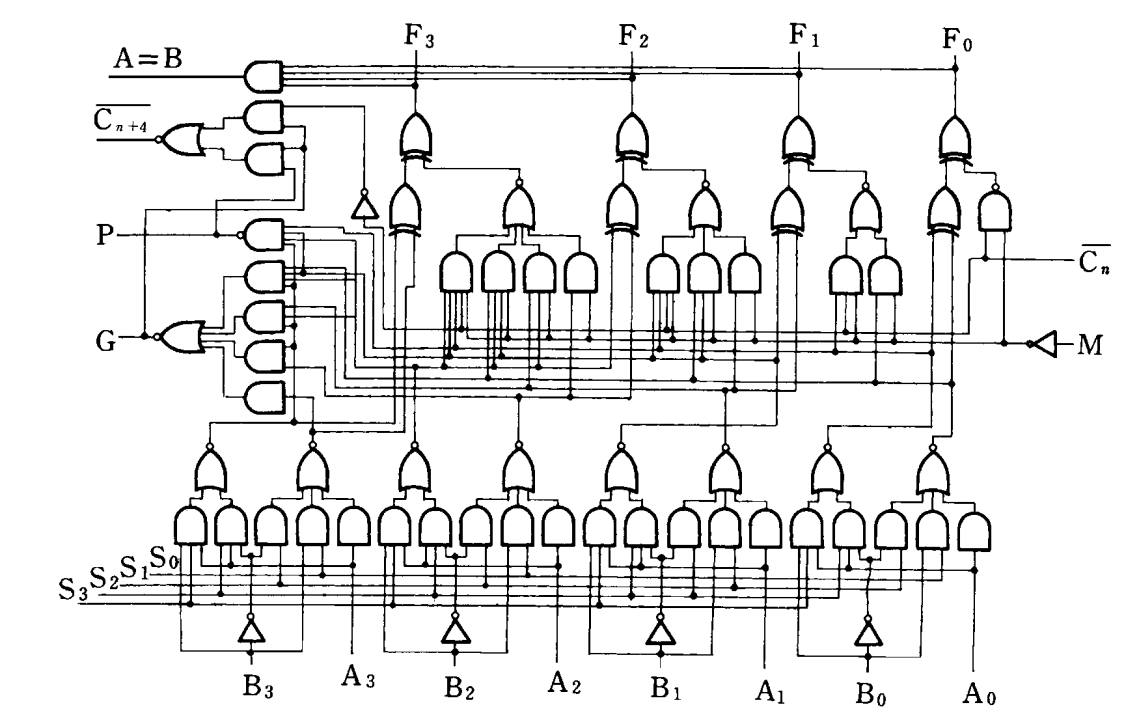

- 器件: 74181

3、算术逻辑运算的实现

- 正逻辑操作数表示的74181ALU逻辑电路图

- 算术逻辑运算的实现(74181)

- M=L时,对进位信号没有影响,做算术运算

- M=H时,进位门被封锁,做逻辑运算

- 说明:

- 74181执行正逻辑输入/输出方式的一组算术运算和逻辑运算和负逻辑输入/输出方式的一组算术运算和逻辑运算是等效的。

- A=B端可以判断两个数是否相等。

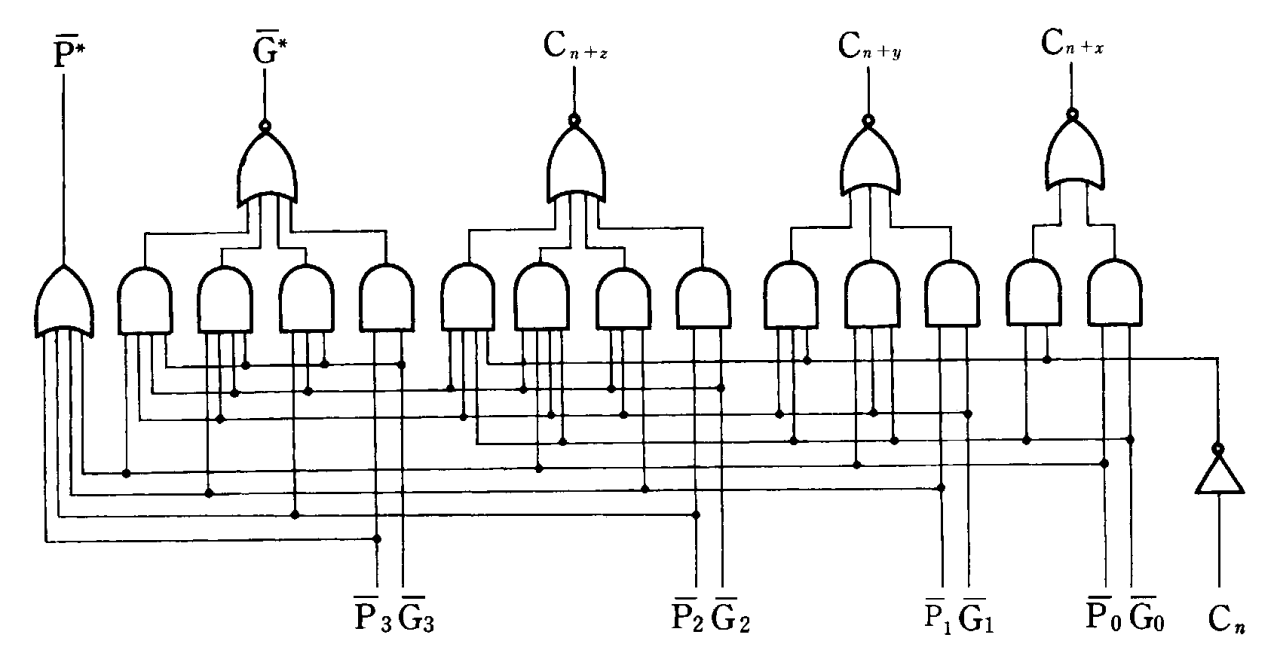

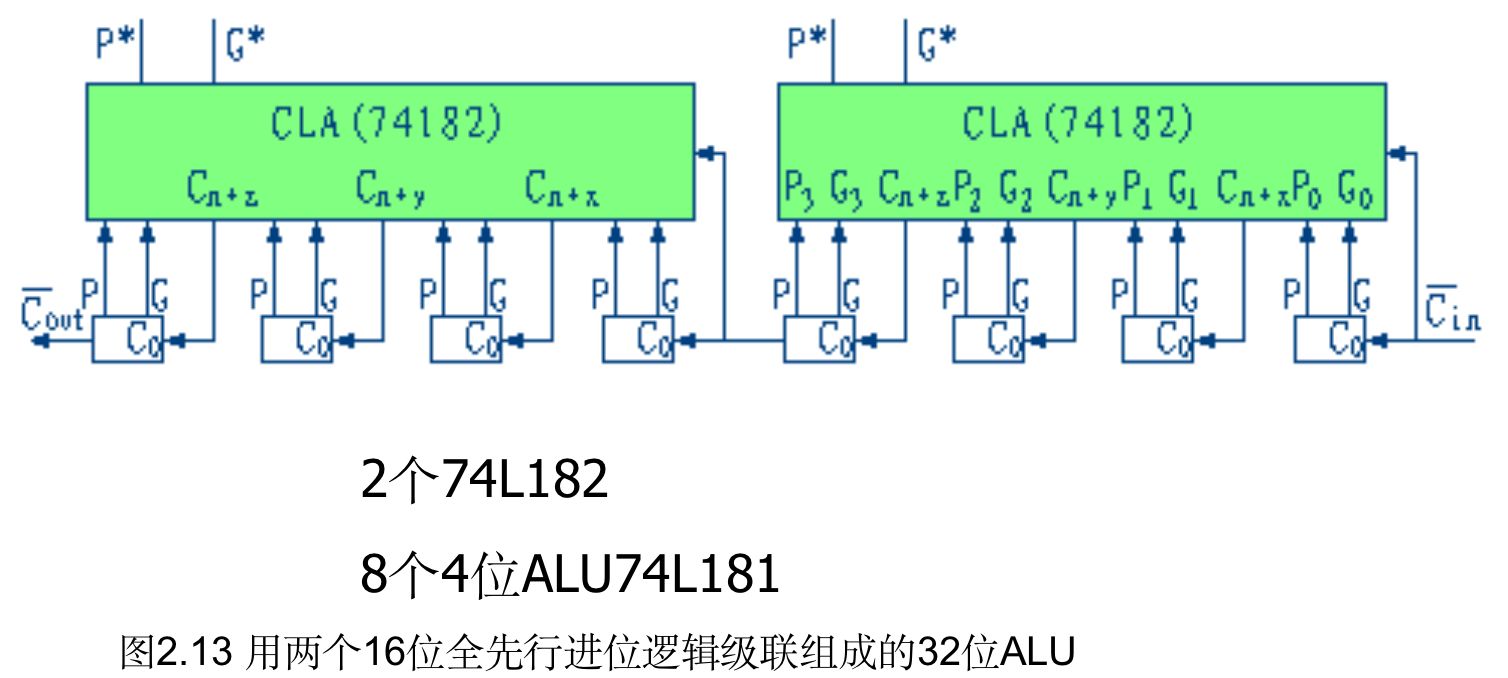

4、两级先行进位的ALU

-

4片(组)的先行进位逻辑

- Cn+x = G0+P0Cn

- Cn+y = G1+P1Cn+x = G1+G0P1+P0P1Cn

- Cn+z = G2+P2Cn+y = G2+G1P2+G0P1P2+P0P1P2Cn

- Cn+4 = G3+P3Cn+z = G3+G2P3+G1P2P3+G0P1P2P3+P0P1P2P3Cn = G*+P*Cn

- G*为成组先行进位发生输出

- P*为成组先行进位传送输出

-

成组先行进位部件CLA的逻辑图

-

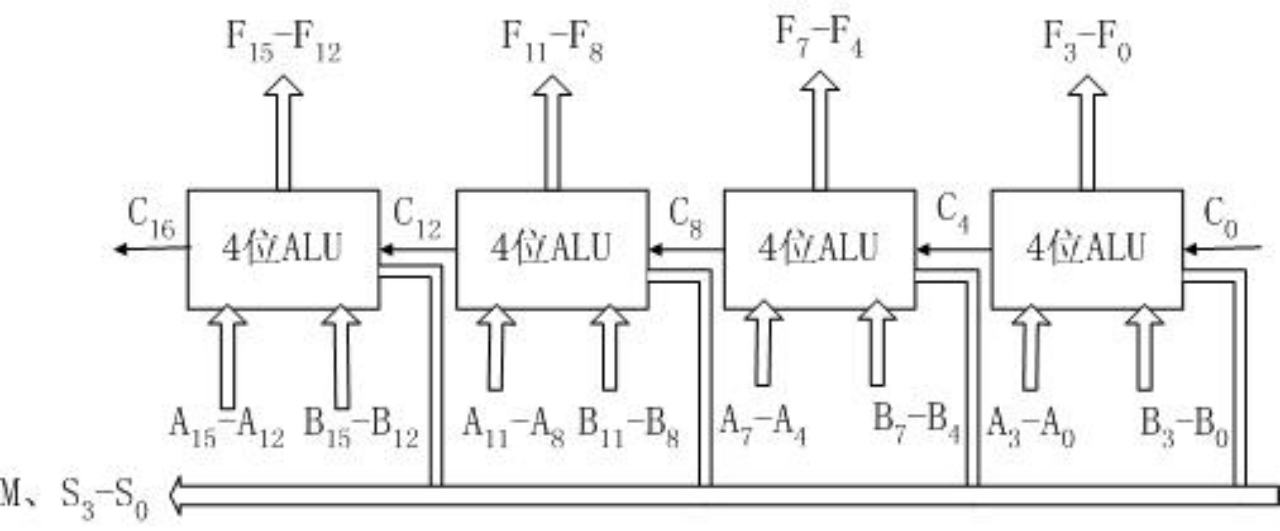

设计16位ALU

-

Cn+x=G2+P2Cn+y Cn+4=G3+P3Cn+z

-

片内先行进位,片间行波进位.

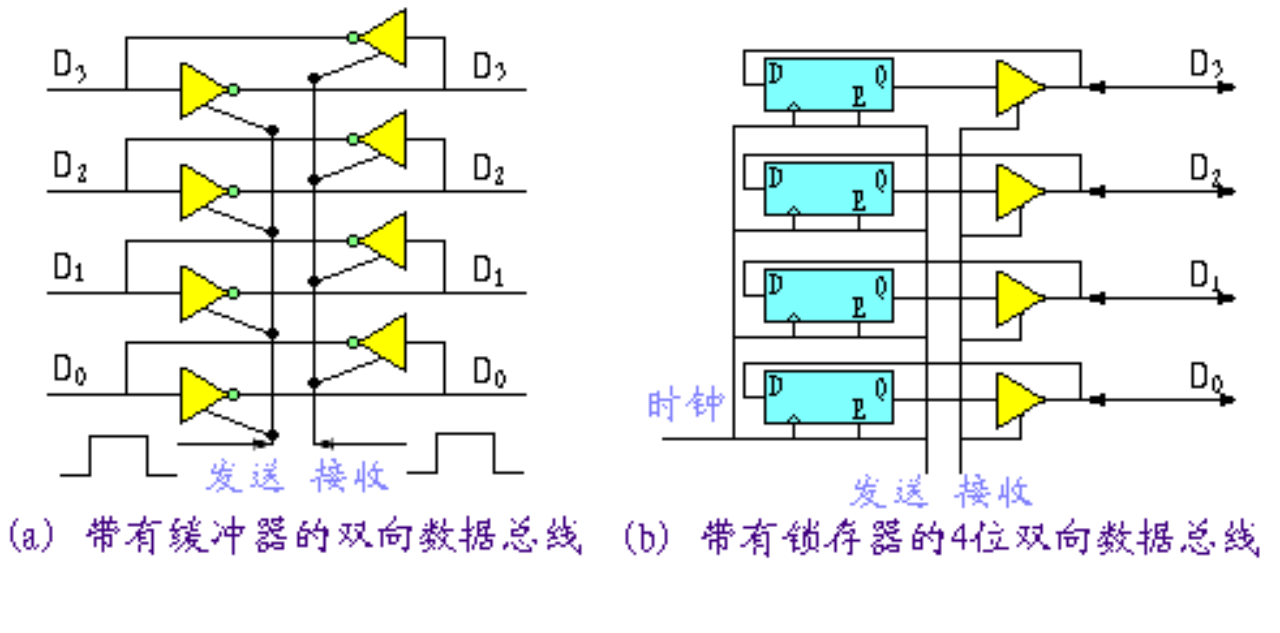

2.5.3 内部总线

- 机器内部各部份数据传送频繁,可以把寄存器间的数据传送通路加以归并,组成总线结构。

- 总线の分类

- 所处位置:内部总线(CPU内)、 外部总线(系统总线)

- 逻辑结构:单向传送总线、 双向传送总线

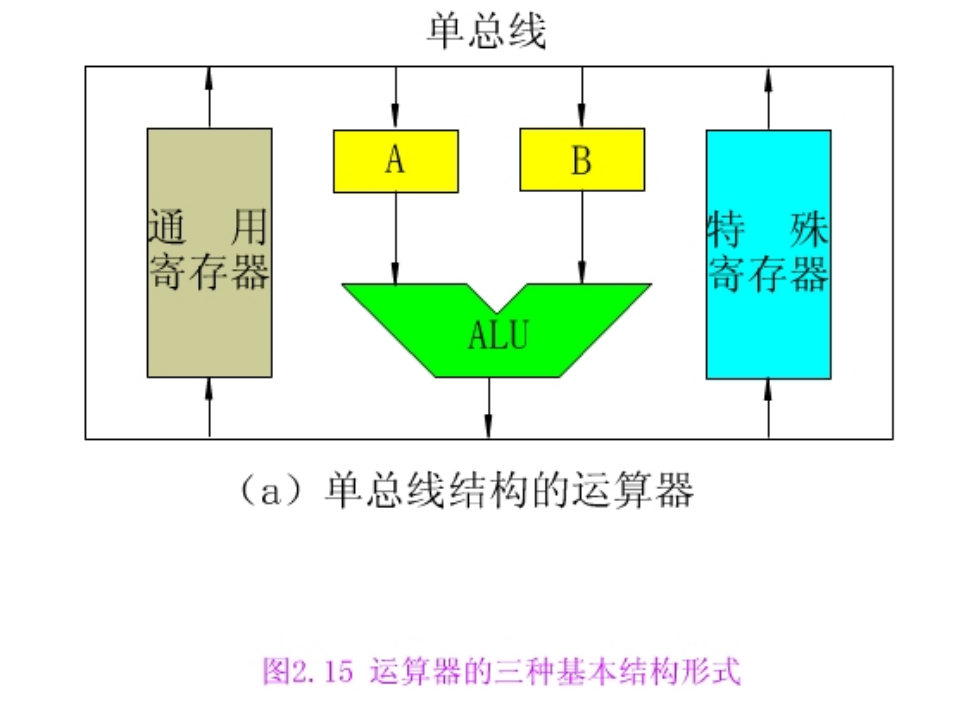

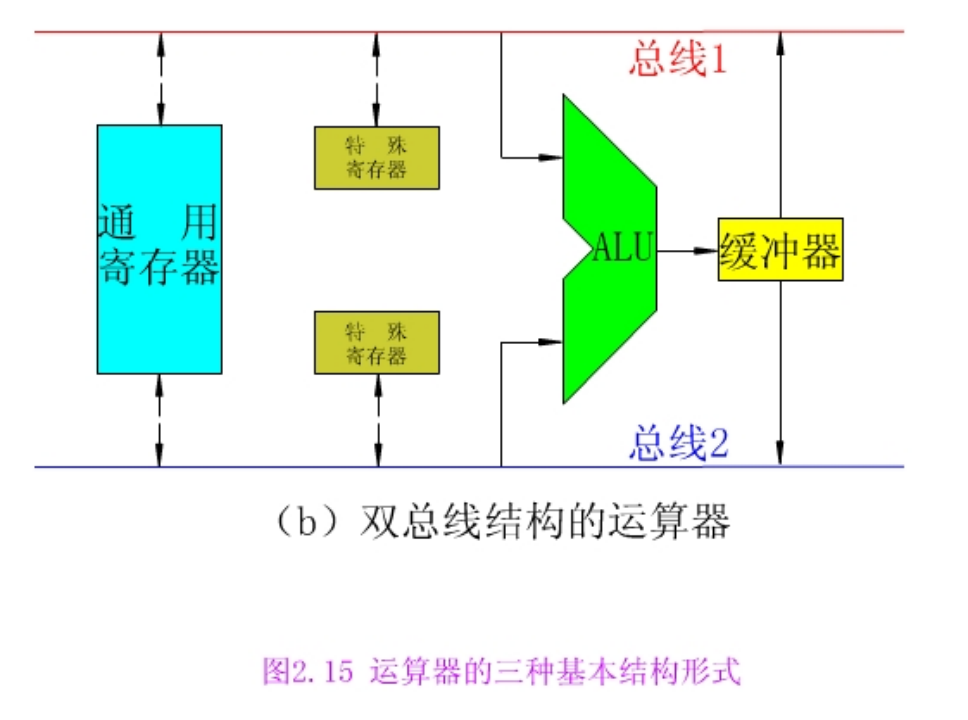

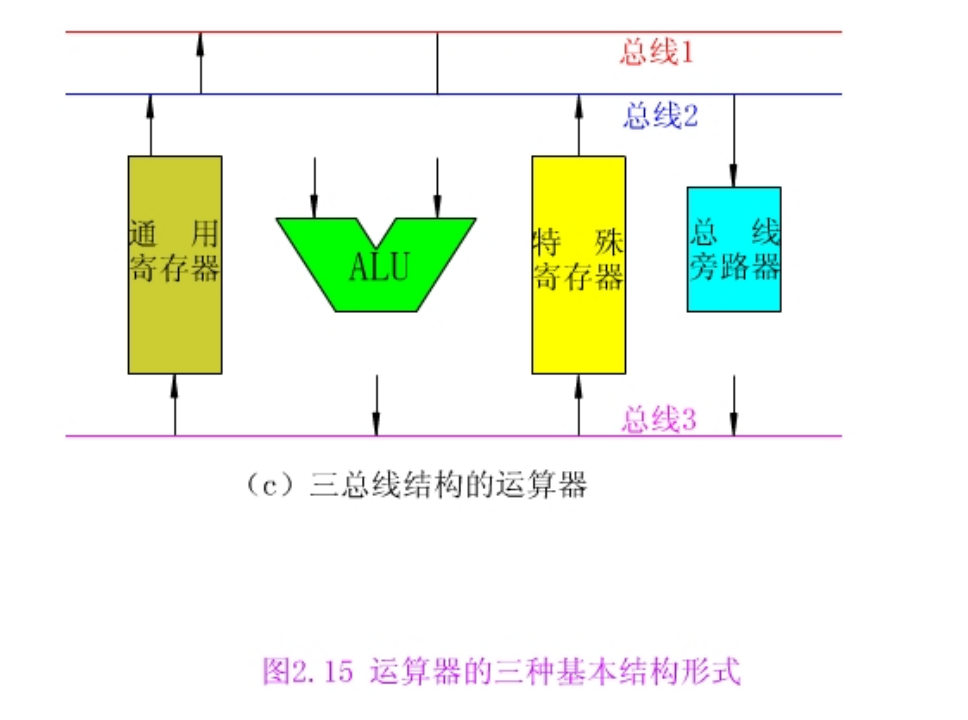

2.5.4 定点运算器的基本结构

-

单总线结构的运算器

-

双总线结构的运算器

-

三总线结构的运算器

2.6 浮点运算与浮点运算器

1、浮点加减运算

- 设有两个浮点数x和y,它们分别为

- x=2Ex·Mx

- y=2Ey·My

- 其中Ex和Ey分别为数x和y的阶码,Mx和My为数x和y的尾数。两浮点数进行加法和减法的运算规则是

- x±y=(Mx2Ex-Ey±My)2Ey,

- 设Ex<=Ey

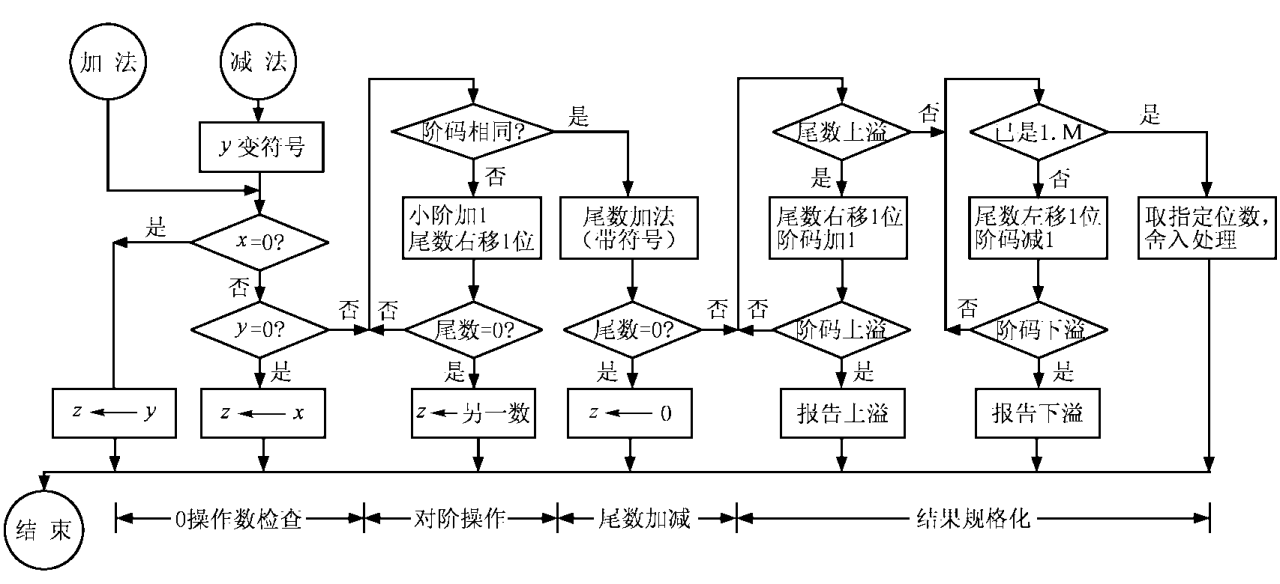

2、浮点运算步骤如下:

-

浮点运算步骤

- 0 操作数检查;

- 比较阶码并完成对阶(小阶向大阶对齐);

- 尾数求和运算;

- 结果规格化;

- 舍入处理。

-

浮点加减法运算操作流程

-

尾数相加(补码加法)

-

结果规格化

- 规则:尾数右移1位,阶码加1,尾数左移1位,阶码减1。

- 左规处理,结果为11.00010101(10),阶码为00011

-

舍入处理(对阶和向右规格化时)

- 就近舍入(0舍1入):类似”四舍五入”,丢弃的最高位为1,进1

- 朝0舍入:截尾

- 朝+∞舍入:正数多余位不全为”0”,进1;负数,截尾

- 朝-∞ 舍入:负数多余位不全为”0”,进1;正数,截尾

- 采用0舍1入法处理,得到1.00010110。

-

溢出判断和处理

- 阶码上溢,一般将其认为是+∞和-∞ 。

- 阶码下溢,则数值为0。

- 阶码符号位为00,不溢出。

- 得最终结果为: x+y = 2011×(-0.11101010)

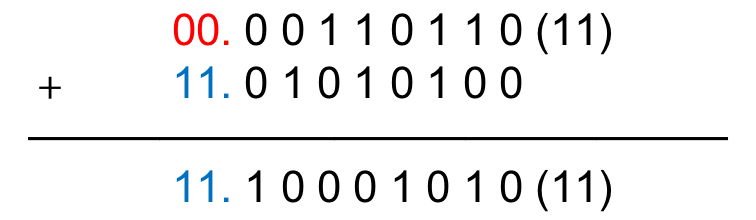

2.6.1 浮点加法、减法运算

- 课堂练习:x=0.1101201 y=-0.1010211

- 尾数和阶符都采用补码表示,都采用双符号位表示法。

- 求x+y

- [x]浮=0001,00.1101

- [y]浮=0011,11.0110

- 阶差=1110 即为-2

- Mx应当右移2位,

- [x]浮=0011,00.0011(01)

- 尾数和为11.1001(01)

- 左规11.0010(10),阶码减1为0010

- 舍入(就近舍入)11.0011 丢弃10

- x+y=-0.1101*210

2.6.2 浮点乘法、除法运算

- 设有两个浮点数x和y:

- x=2Ex·Mx

- y=2Ey·My

- x×y=2(Ex+Ey)·(Mx×My)

- x÷y=2(Ex-Ey)·(Mx÷My)

- 乘除运算分为四步

- 0操作数检查

- 阶码加减操作

- 尾数乘除操作

- 结果规格化和舍入处理

- 补码采用双符号位,为了对溢出进行判断

- 00 为正 11 为负

- 01 上溢 10 下溢

- 尾数处理

- 截断

- 舍入

- 尾数用原码表示时

- 只要尾数最低为1或者移出位中有1数值位,使最低位置1

- 0舍1入

- 尾数用原码表示时

- 尾数用补码表示时

- 丢失的位全为0,不必舍入。

- 丢失的最高位为0,以后各位不全为0时;或者最高为1,以后各位全为0时,不必舍入。

- 丢失的最高位为1,以后各位不全为0时,则在尾数的最低位入1的修正操作。

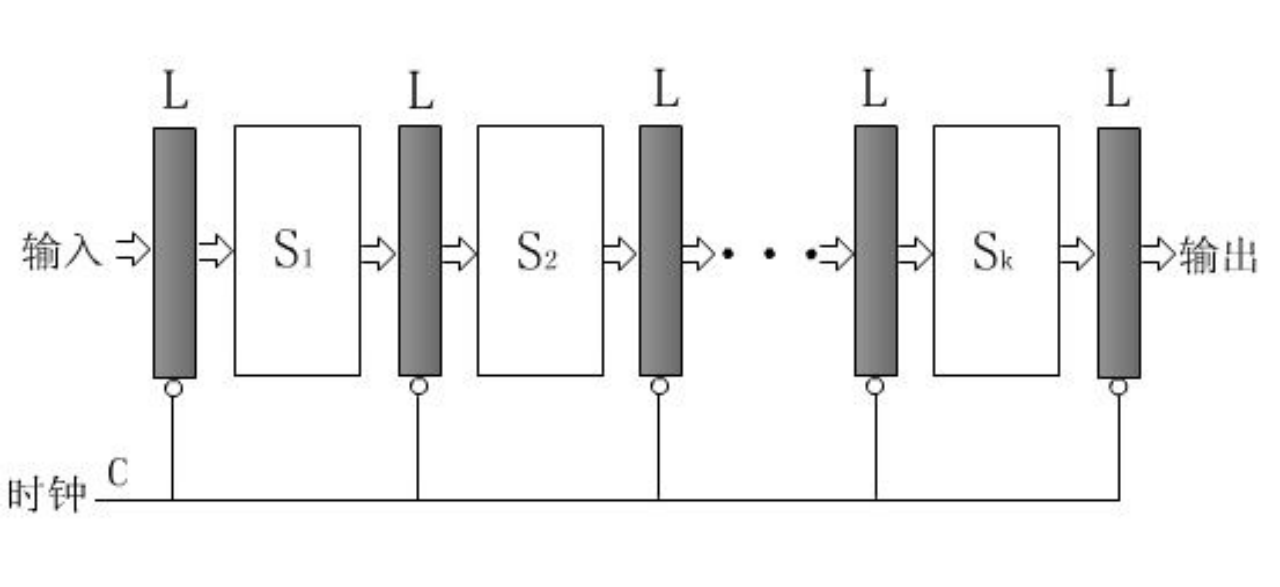

2.6.3 浮点运算流水线

1、提高并行性的两个渠道:

- 空间并行性:增加冗余部件,如增加多操作部件处理机和超标量处理机

- 时间并行性:改善操作流程如:流水线技术

2、流水技术原理

- 在流水线中必须是连续的任务,只有不断的提供任务才能充分发挥流水线的效率

- 把一个任务分解为几个有联系的子任务。每个子任务由一个专门的功能部件实现

- 在流水线中的每个功能部件之后都要有一个缓冲寄存器,或称为锁存器

- 流水线中各段的时间应该尽量相等,否则将会引起“堵塞”和“断流”的现象

- 流水线需要有装入时间和排空时间,只有当流水线完全充满时,才能充分发挥效率

- 设过程段 Si所需的时间为τi,缓冲寄存器的延时为τl,线性流水线的时钟周期定义为

- τ=max{τi}+τl=τm+τl

- 流水线处理的频率为 f=1/τ

- 一个具有k 级过程段的流水线处理 n 个任务需要的时钟周期数为Tk=k+(n-1)

- 所需要的时间为: T=Tk × τ

- 顺序完成的时间为:T=n×k×τ

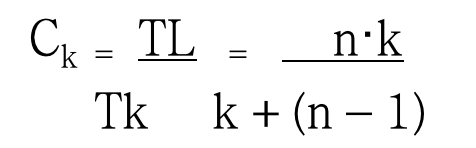

- k级线性流水线的加速比:

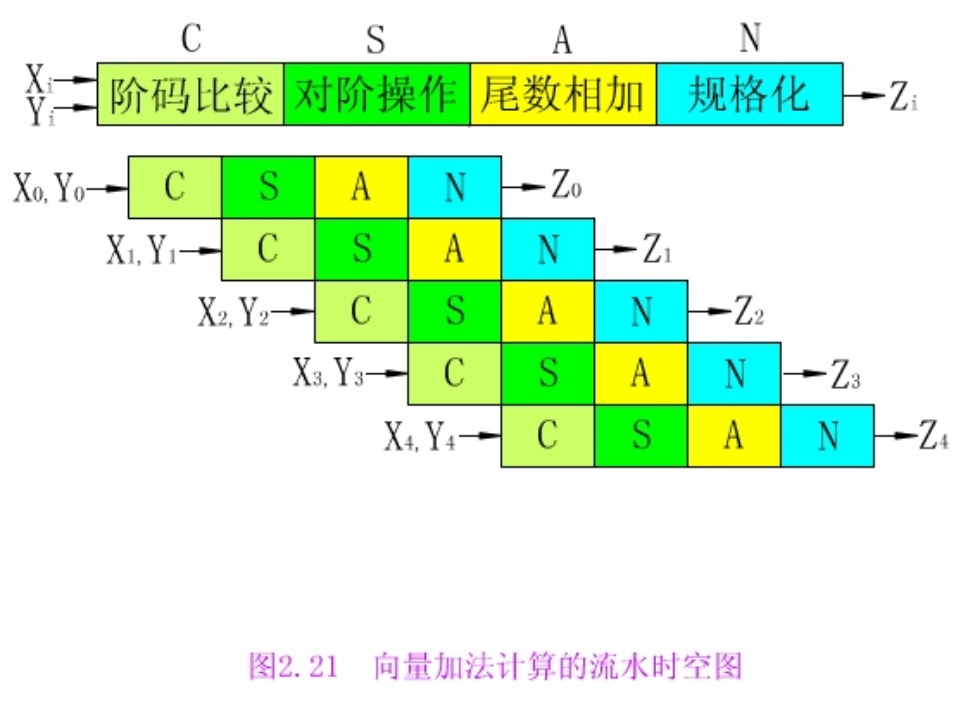

3、流水线浮点运算器

- A=a×2P, B=b×2q

- 在4级流水线加法器中实现上述浮点加法时,分为以下操作:

- 求阶差、对阶、相加、规格化

- 求阶差、对阶、相加、规格化

2.6.4 浮点运算器实例

- 浮点运算器实例

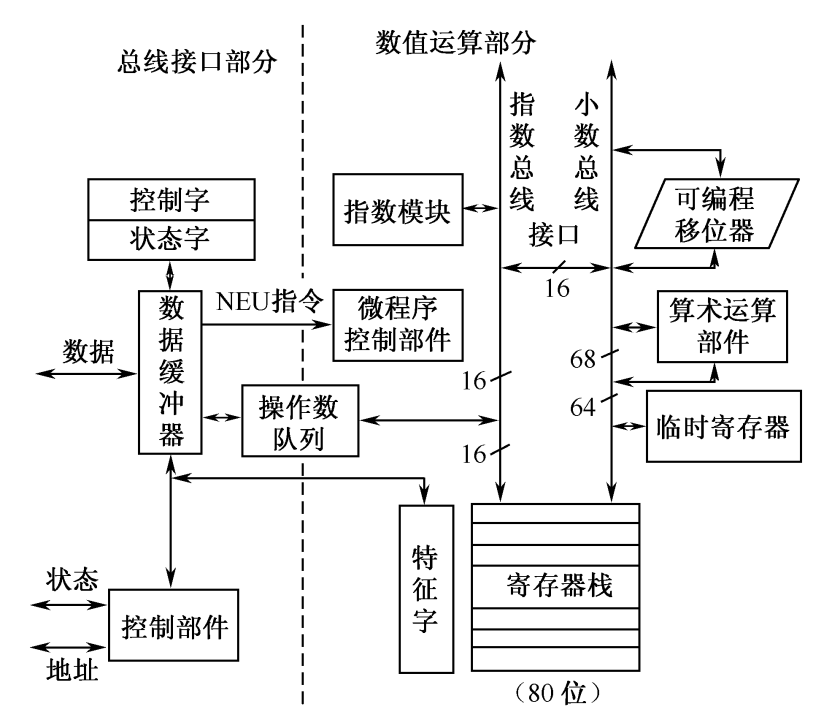

- CPU之外的浮点运算器(数学协处理器)如80287

- 完成浮点运算功能,不能单用。

- 可以和80386或80286异步并行工作。

- 高性能的80位字长的内部结构。有8个80位字长以堆栈方式管理的寄存器组。

- 浮点数格式完全符合IEEE标准。

- CPU之内的浮点运算器(486DX以上)

- CPU之外的浮点运算器(数学协处理器)如80287

1250

1250

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?