目录

中断

中断简介

UG585 CH7 Interrupts

以下主要是翻译的文档。

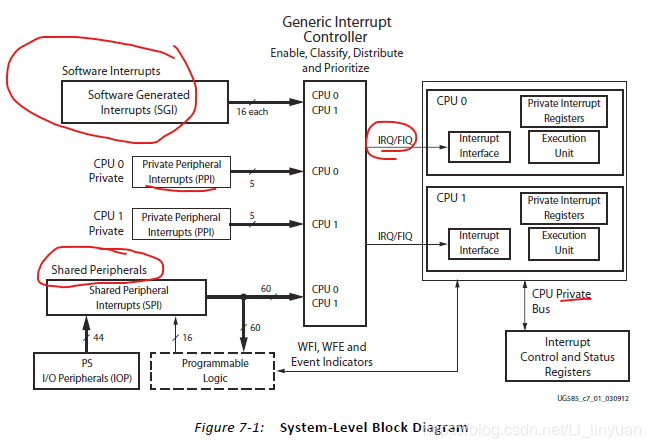

中断通过GIC pl390连接CPU。

CPU接收的中断包括来自外围I/O和PL侧。主要包括下面关键点:

私有、共享和软中断

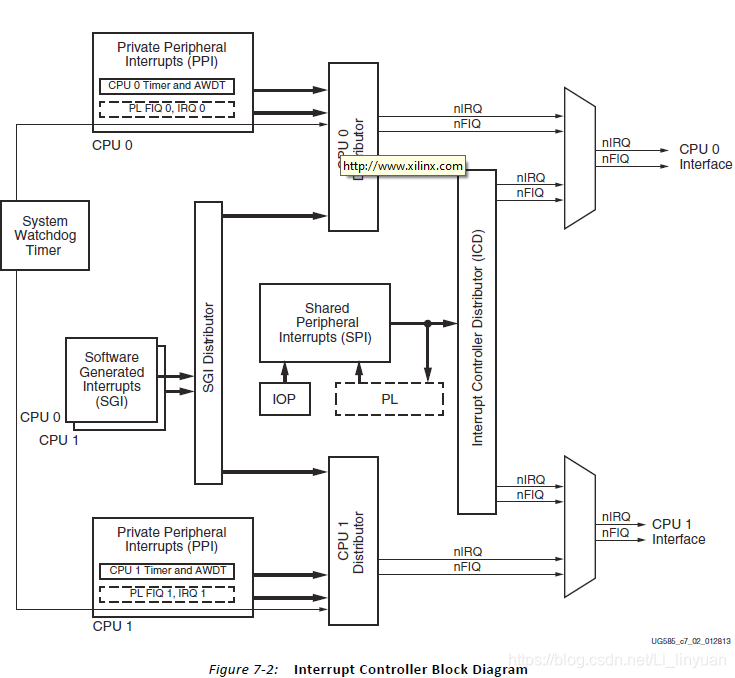

每个CPU都一组私有外设中断PPI,使用分组寄存器专用访问。PPI包括全局全局定时器、私有看梦定时器、私有定时器和PL侧的FIQ/IRQ。(是ARM的两种不同的中断模式)

软中断SGI被路由到一个或两个CPU。SGIs由通用中断控制器GIC的寄存器生成。

共享外设中断SPIs由各种I/O和PS和PL的内存控制器,被连接到一个或两个CPU。SPIs同时也被路由到PL侧。

(从上面的图,可以看到中断分为三类,SGI、PPI和SPI,其中SPI由包括PS和PL两部分)

通用中断控制器GIC

GIC是一个管理来自PS和PL中断的集中资源。当CPU接口接收下一个中断是,GIC使能、禁用、屏蔽和优先处理中断源并以编程方式发送中断给选定的CPU。

此外,GIC支持安全扩展以实现安全感知系统。

GIC基于ARM GIC v1.0 非矢量

为了快速读写响应,GIC通过私有总线访问寄存器,避免暂时阻塞或其他瓶颈。

GIC集中所有的中断资源进行调度,分发最该优先级的中断给各个CPU。

当一个中断面向多个CPU时,GIC确保一次只有一个CPU执行。

所有的中断源都有唯一的中断标识号。

所有的中断源都有自己的可配置的优先级和目标CPU列表。

(从上面的图可以看到,SGI、PPI和SPI都是发给GIC,通过IRQ/FIQ发送给CPU)

复位和时钟

GIC的复位由复位子系统控制,由系统级控制寄存器SLCR的A9_CPU_RST_CTRL寄存器的PERI_RST位.控制。该信号也复位CPU的私有定时器和私有看梦定时器AWDT。复位后,所有挂起或正在进行的中断全部被忽略。

GIC操作的时钟是CPU_3x2x(一半CPU的频率)。

模块图

SPIs由各种子系统生成,包括PS的I/O外设和PL的逻辑。

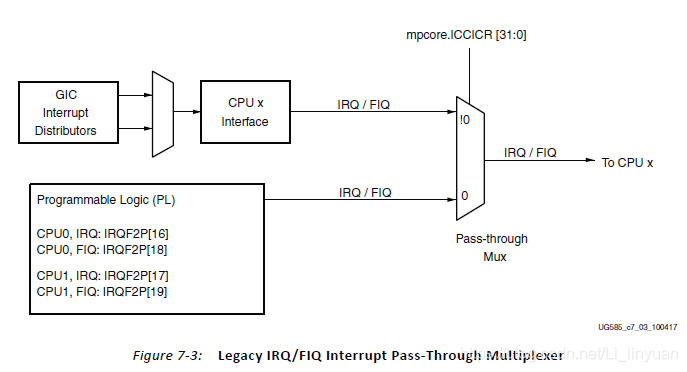

CPU中断信号直通

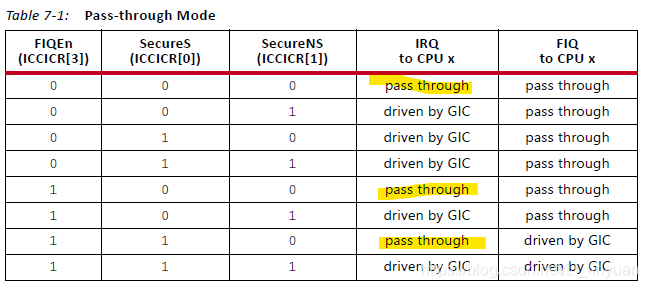

PL的中断可以路由到GIC作为PPI #4或#1中断,或者绕过GIC通过直通复用器。

两个CPU都可以使用。直通模式由mpcore.ICCICR寄存器控制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?