目录

GPIO使用

Zynq GPIO简介

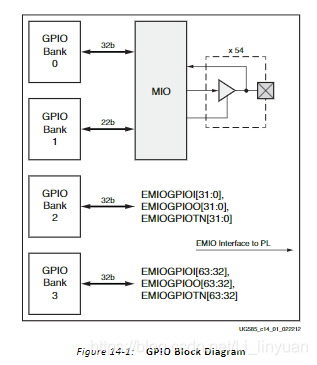

UG585 CH14

BANK0和BANK1控制有54个MIO;

BANK2和BANK3有MIO连接到PL;

硬件系统

在前面的PS最小系统上进行修改。

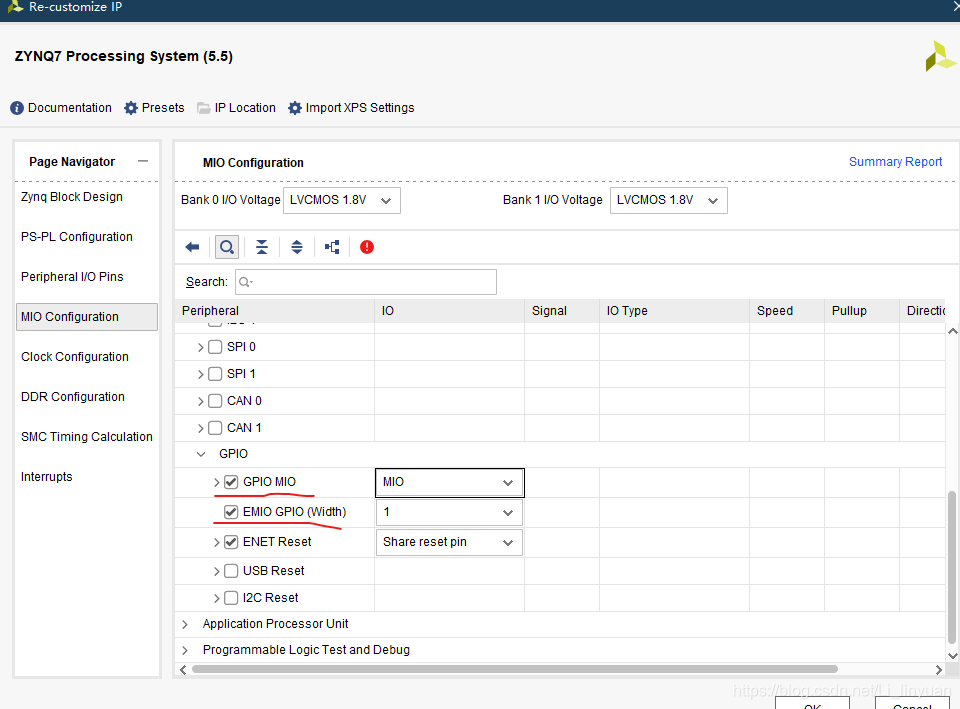

添加MIO和EMIO

在Zynq的IP中选着需要的MIO管脚和需要的EMIO管脚数量。

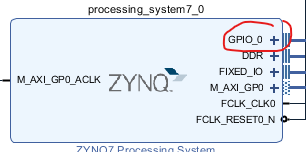

更新的后的IP图标上有GPIO,

这就是PS引出来的EMIO,直接make external引导器件管脚上;

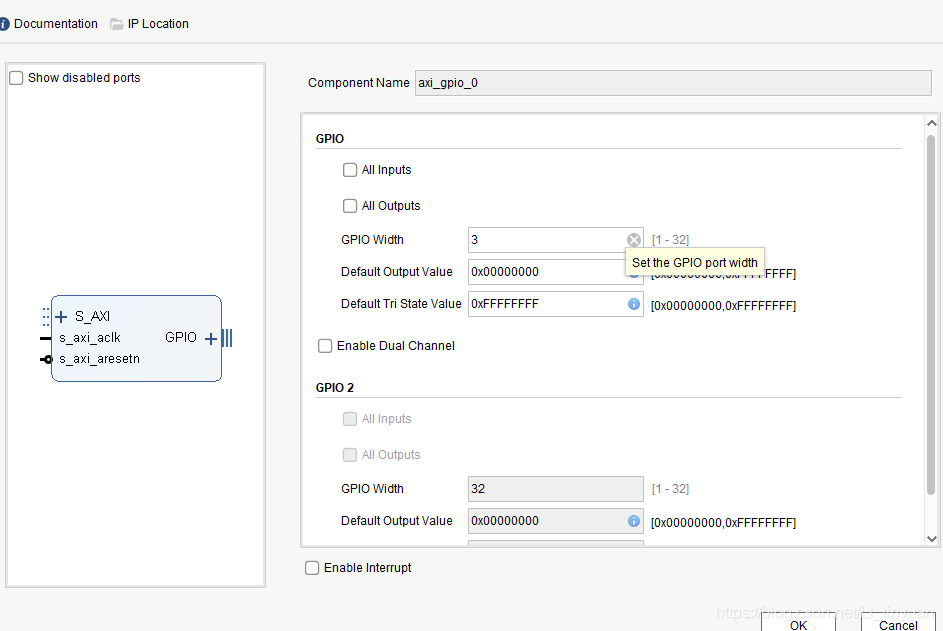

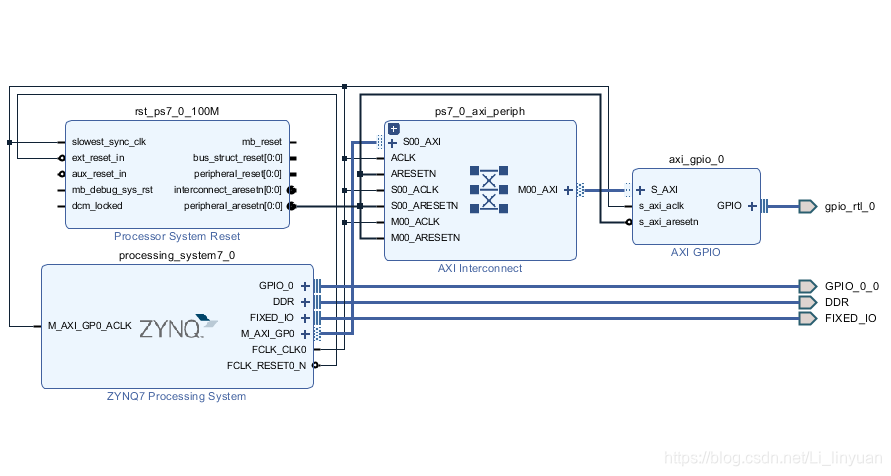

添加AXI GPIO

添加AXI的GPIO IP,是PS通过AXI总线控制GPIO,即一般管脚;

每个IP可以配置两个通道

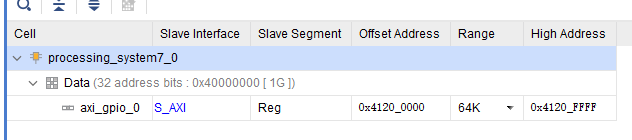

在地址页面有给AXI_GPIO分配的地址

完成后的系统框图如下

管脚约束

# tri-led

set_property PACKAGE_PIN Y16 [get_ports {gpio_rtl_0_tri_io[2]}]

set_property PACKAGE_PIN Y17 [get_ports {gpio_rtl_0_tri_io[1]}]

set_property PACKAGE_PIN R14 [get_ports {gpio_rtl_0_tri_io[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {gpio_rtl_0_tri_io[2]}]

set_property IOSTANDARD LVCMOS33 [g

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

841

841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?