一、TTL 集成电路的功能测试

1、实验目的

(1)熟悉 TTL 各种门电路的逻辑功能;

(2)掌握 TTL 各种门电路的逻辑功能测试方法;

(3)掌握 Multisim 软件使用。

2、步骤设计

(1)与非门逻辑功能测试

① 按下图接线

② 按表要求用开关改变输入端A,B,C,D的状态,借助指示灯和万用表,把测试结果填入表中

(2)或非门逻辑功能测试

① 按下图接线

② 按表的要求用开关改变输入量A,B的状态,借助指示灯和万用表观测各相应输出端F的状态,并将测试结果填入表中

(3)与或非门逻辑功能测试

① 按下图接线

② 按表要求用开关改变输入量A,B,C,D的状态,借助指示灯和万用表观测各对应输出端F的状态,并把测试结果记入表中

(4)异非门逻辑功能测试

① 按下图接线

② 按表要求用开关改变输入量A,B的状态,借助指示灯和万用表观测各对应输出端F的状态,并把测试结果填入表中

(5)利用74LS00与非门实现”与电路”,”或电路”,”或非电路”,”异或电路”要写出各种电路的逻辑表达式和真值表,画出逻辑图并在实验仪上加以验证

3、电路仿真

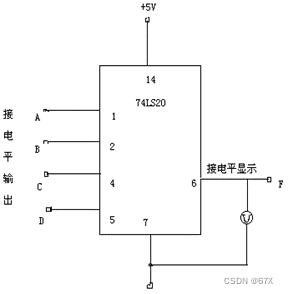

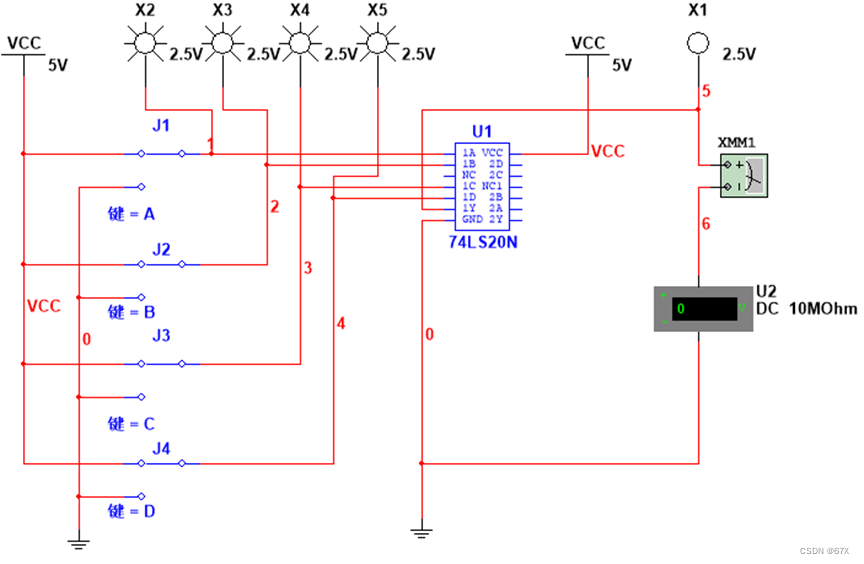

(1)与非门逻辑功能测试

用74LS20双四输入与非门进行实验,虚拟仿真实验原理图如图所示:

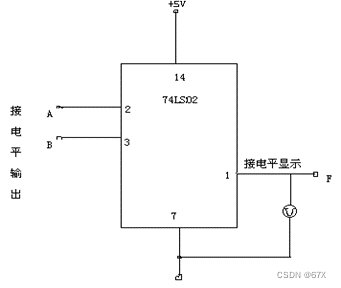

(2)或非门逻辑功能测试

用74LS02二输入四或非门进行实验,虚拟仿真实验原理图如图所示:

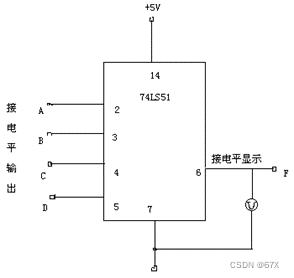

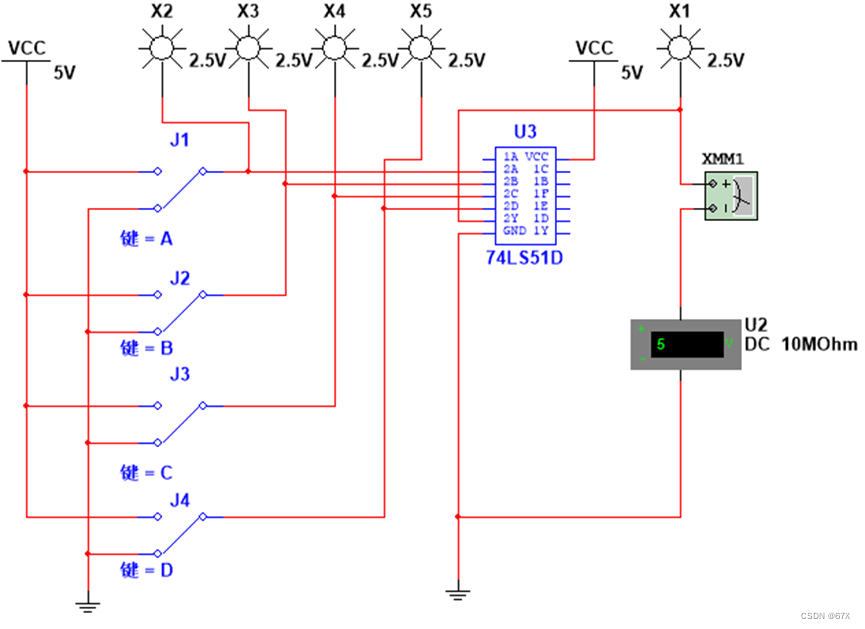

(3)与或非门逻辑功能测试

用7451双2–3输入与或非门进行实验,虚拟仿真实验原理图如图所示:

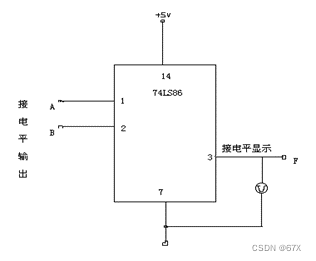

(4)异或门逻辑功能测试

用74LS86二输入四异或进行实验,虚拟仿真实验原理图如图所示:

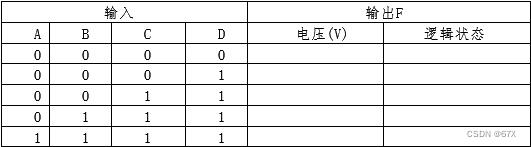

4、实验结果与分析

(1)74LS20 双四输入与非门功能测试

| 输入 | 输出F | ||||

| A | B | C | D | 电压(V) | 逻辑状态 |

| 0 | 0 | 0 | 0 | 5 | 1 |

| 0 | 0 | 0 | 1 | 5 | 1 |

| 0 | 0 | 1 | 0 | 5 | 1 |

| 0 | 0 | 1 | 1 | 5 | 1 |

| 0 | 1 | 0 | 0 | 5 | 1 |

| 0 | 1 | 0 | 1 | 5 | 1 |

| 0 | 1 | 1 | 0 | 5 | 1 |

| 0 | 1 | 1 | 1 | 5 | 1 |

| 1 | 0 | 0 | 0 | 5 | 1 |

| 1 | 0 | 0 | 1 | 5 | 1 |

| 1 | 0 | 1 | 0 | 5 | 1 |

| 1 | 0 | 1 | 1 | 5 | 1 |

| 1 | 1 | 0 | 0 | 5 | 1 |

| 1 | 1 | 0 | 1 | 5 | 1 |

| 1 | 1 | 1 | 0 | 5 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

分析:输入 A,B,C,D 中有一个逻辑电平为“0”时输出为“1”,只有当输入 A,B,C,D 全为“1”时输出才为“0”,满足与非门的“见0为1,全1为0”,所以仿真实验验证该芯片实现了四输入与非门的功能。

(2)74LS02二输入四或非门功能测试

| 输入 | 输出F | ||

| A | B | 电压(V) | 逻辑状态 |

| 0 | 0 | 5 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 |

分析:输入A,B中有一个逻辑电平为“1”时输出为“0”,只有当输入A,B全为“0”时输出才为“1”,满足或非门的“见1为0,全0为1”,所以仿真实验验证该芯片实现了二输入或非门的功能。

(3)7451双2–3输入与或非门功能测试

| 输入 | 输出F | ||||

| A | B | C | D | 电压(V) | 逻辑状态 |

| 0 | 0 | 0 | 0 | 5 | 1 |

| 0 | 0 | 0 | 1 | 5 | 1 |

| 0 | 0 | 1 | 0 | 5 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 5 | 1 |

| 0 | 1 | 0 | 1 | 5 | 1 |

| 0 | 1 | 1 | 0 | 5 | 1 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 5 | 1 |

| 1 | 0 | 0 | 1 | 5 | 1 |

| 1 | 0 | 1 | 0 | 5 | 1 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

分析:输入A,B,C,D中以A、B和C、D分成的两组输入中任意一组的逻辑电平全为“1”时输出为“0”,只有当两组输入的每一组都不全为“1”时输出才为“1”,满足与或非门的输出特性,所以仿真实验验证该芯片实现了四输入与或非门的功能。

(4)74LS86二输入四异或异或门功能测试

| 输入 | 输出F | ||

| A | B | 电压(V) | 逻辑状态 |

| 0 | 0 | 5 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 5 | 1 |

分析:输入A,B中逻辑电平互不相同时输出为“0”,只有当输入A,B相同时输出才为“1”,满足异或门的“相同为1,不同为0”,所以仿真实验验证该芯片实现了二输入异或门的功能。

二、3/8译码器

1、实验目的

(1)熟悉 3/8译码器的逻辑功能;

(2)掌握 3/8译码器的逻辑功能测试方法;

(3)掌握 Multisim 软件使用。

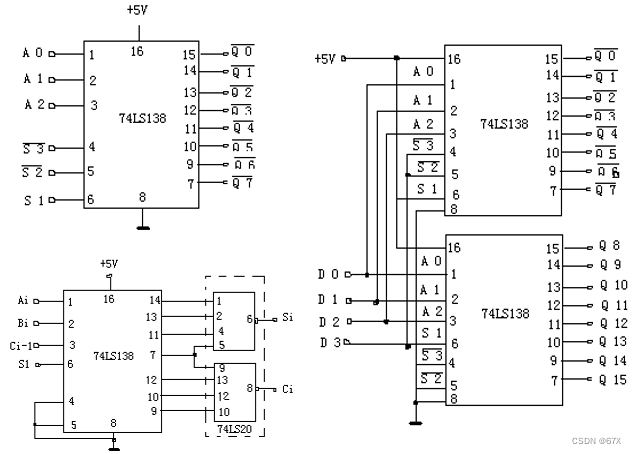

2、芯片引脚图

3、仿真测试

(1)3/8译码器逻辑功能测试

用74LS138进行实验,利用开关设置S1,S2,S3及A2,A1,A0的状态,借助指示灯或万用表观测Q0-Q7的状态,虚拟仿真实验原理图如图所示:

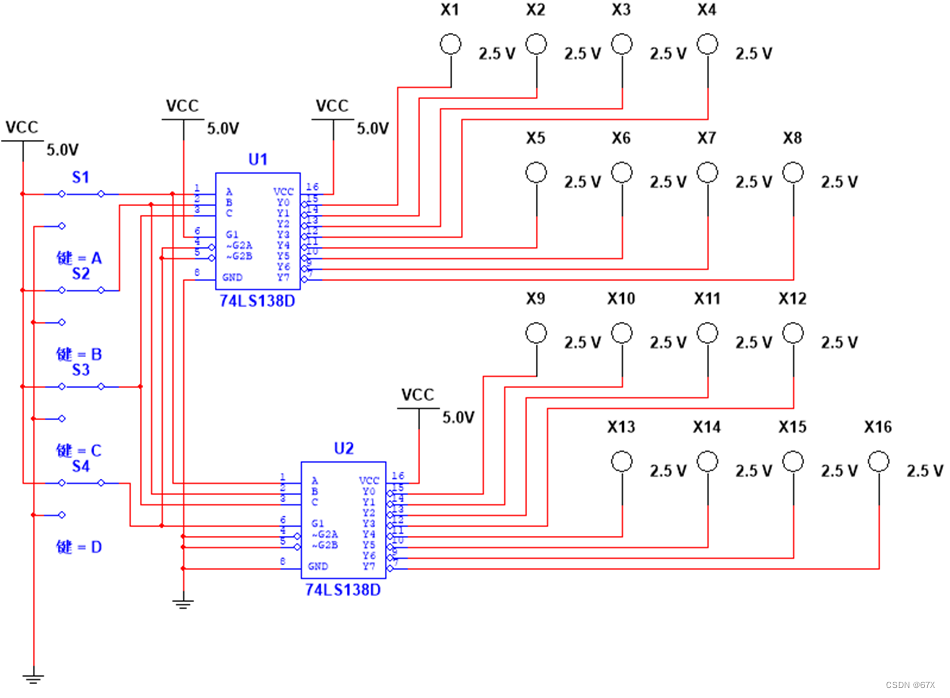

(2)两片74LS138组成4-16线译码器

利用开关改变输入D0-D3的状态,借助指示灯或万用表监测输出端,虚拟仿真实验原理图如图所示:

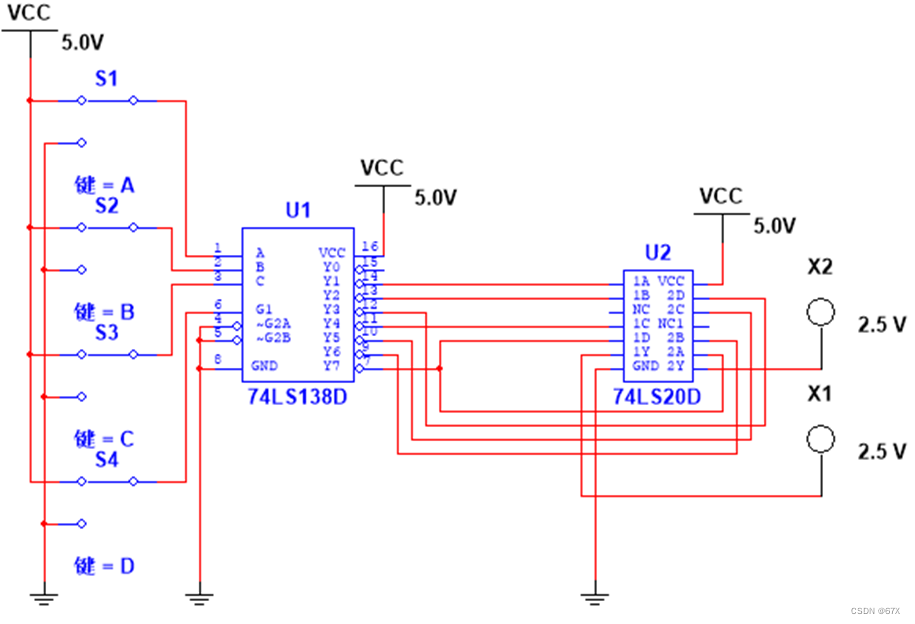

(3)利用译码器组成全加器线路

用74LS138和74LS20接线,74LS20芯片14脚接+5V,7脚接地.利用开关改变输入Ai,Bi,Ci状态,借助指示灯或万用表观测输出Si,Ci的状态,虚拟仿真实验原理图如图所示:

4、实验结果与分析

(1)74LS138 3/8译码器功能测试

| 输入 | 输出F | ||||||||||||

| S1 | S2 | S3 | A2 | A1 | A0 | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 |

| 0 | X | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| X | 1 | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| X | X | 1 | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

根据表可得逻辑表达式为:

分析:A2,A1,A0为三位二进制代码输入端,Q0~Q7是8个输出端,S1,S2,S3为三个输入控制端,只有S1=0,S2=S3=0时译码器才处于工作状态,否则译码器处于禁止状态,所有输出端均为高电平。工作状态时将A2A1A0的输入状态看做三位二进制数,各二进制数对应的十进制数对应下标的输出端为“0”,其余输出端为“1”。所以仿真实验验证了74LS138的功能。

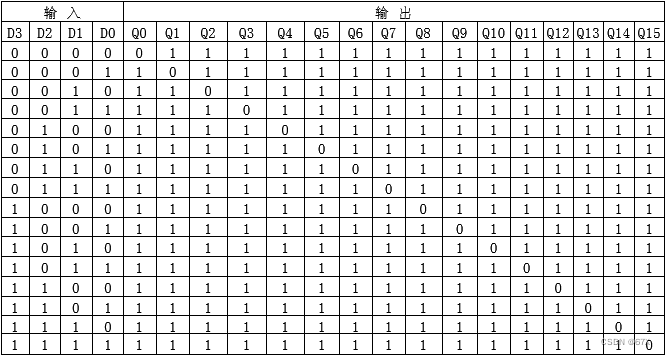

(2)4-16线译码器功能测试

根据表可得逻辑表达式为:

分析: 用两片3线-8线译码器组成4-16线译码器可正常工作,输出有效电平为低电平。

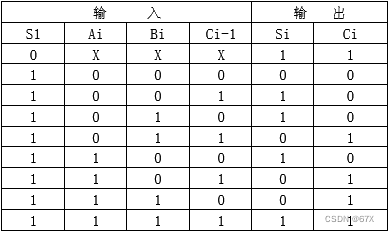

(3)全加器功能测试

根据表可得逻辑表达式为:

![]()

分析:S1为控制端,S1为低电平时输出全为“1”,表示处于禁止状态;当S1为“1”时,正常工作,Ai 为加数 Bi 为被加数Ci-1 为低位的进位,Si为和数Ci为进位,由测试表数据可知该全加器实现了对两个一位二进制数相加的同时,还加上了来自低位的进位,实现了全加器的功能。

三、振荡、计数、译码、显示电路

1、实验目的

(1)熟悉振荡、计数、译码、显示电路的逻辑功能;

(2)掌握振荡、计数、译码、显示电路的逻辑功能测试方法;

(3)掌握 Multisim 软件使用。

2、实验原理

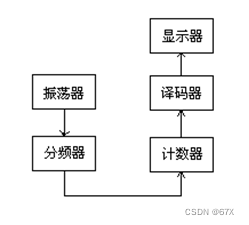

本实验电路分别由多谐振荡器、分频器、计数器、译码器和数字显示器等五部分组成,电路原理框图如图所示:

芯片引脚图如下:

3、振荡、计数、译码、显示电路逻辑功能测试

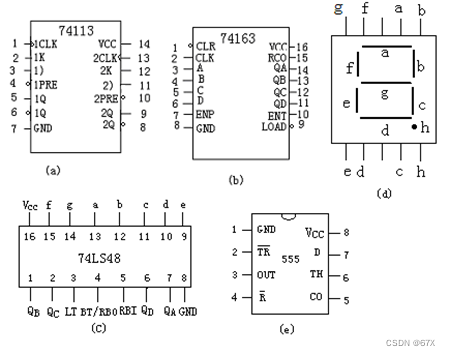

用555定时器和集成JK触发器进行实验,虚拟仿真实验原理图如图所示:

4、实验结果与分析

图中74LS112为2JK触发器组成分频电路,其中CLK为CP脉冲输入端,为置位端,低电平有效,正常工作时应接高电平。计数器用于记录脉冲的个数,采用74LS163组成,CLK为CP脉冲输入端 CLR为清零端。只要CLR=0.各触发器均被清零,计数器输出为0000。不清零时应使CLR=1.LOAD为预置数控制端。只要在LOAD=0的前提下,加入CP脉冲上升沿,计数器被计数,即计数器输出QA,QB,QC,QD等于数据输入端A,B,C,D输入的二进制数。这就可以使计数器从预置数开始做加法计数。不预置时应使LOAD=1.ENP,ENT为功能控制端,当ENP=ENT=1(CLR=1,LOAD=1)时,计数器处于计数状态.当计数到1111状态时,进位输出RCO=1。再输入一个计数脉冲,计数器输出由1111返回0000状态,RCO由1变成0,作为进位输出信号。当ENP=0,ENT=1(CLR=1,LOAD=1)时,计数器处于保持工作状态。ENP=1,ENT=0(CLR=1,LOAD=1)时,计数器输出状态保持不变,可进位输出RCO=0。译码器就是把输入代码译成相应的输出状态, BCD7DEC(74LS48)是把四位进制码经内部组合电路“翻译”成七段(a,b,c,d,e,f,g)输出,然后直接推动LED,显示0~15等十六个数字。显示部分是译码器的输出以数字形式直观显示出来.实验采用共阴极LED七段器.使用时可把BCD7DEC(74LS48)译码器输出端a,b,c,d,e,f,g接到对应的引脚即可。所以仿真实验验证了555定时器和集成JK触发器功能。

四、多路智力抢答器

1、实验目的

(1)熟悉编码器、译码器和触发器的工作原理及特点。

(2)学习抢答器的设计方法。

2、实验思路

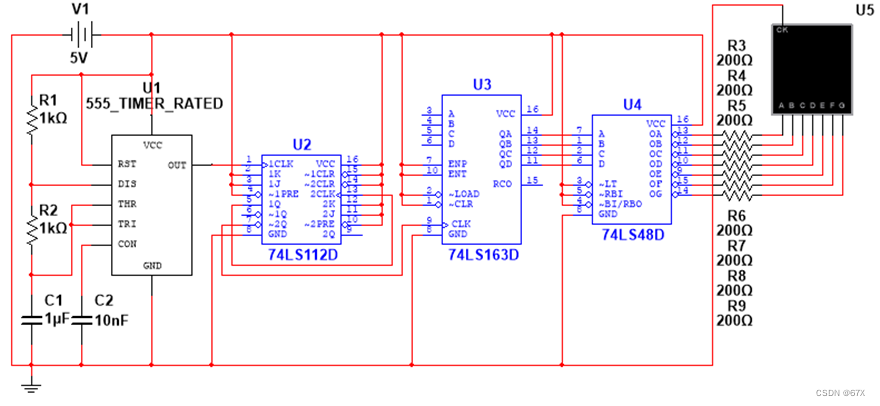

用3/8译码器实现抢答控制,用LED数码管显示选手序号。设计框图如图:

3、设计任务

(1)自选元器件设计抢答器,要求最多可以容纳8名选手参加比赛,每人一个抢答开关,分别对应为S0、S1、S2、S3、S4、S5、S6、S7。主持人用一个开关S,给系统清零(复位)。

(2)选手面前各有一个发光二极管,主持人发出指令后,选手同时开始抢答,唯一抢答成功的选手面前灯亮,其他选手将抢答无效,即需要具有封存输入编码电路的功能。

(3)抢答器应具有锁存功能,并保持到主持人清零时为止。

(4)抢答器应具有显示功能,将选手的编号显示出来。

4、电路设计

(1)抢答电路:

选用优先编码器74LS148、锁存器74LS279和译码器74LS48组成,实现以下功能:

① 判断最先进入的选手信号并锁存该信号,同时将该信号传入译码显示电路;

② 阻隔滞后首个选手的选手信号,使其无法进入译码显示电路。

(2)译码、显示电路设计:

选用译码器74LS48和共阴极7段显示器组成,实现以下功能:

① 对传入信号的译码和显示;

② 反映电路的抢答功能并能通过显示管的显示情况来判断电路的工作状况。

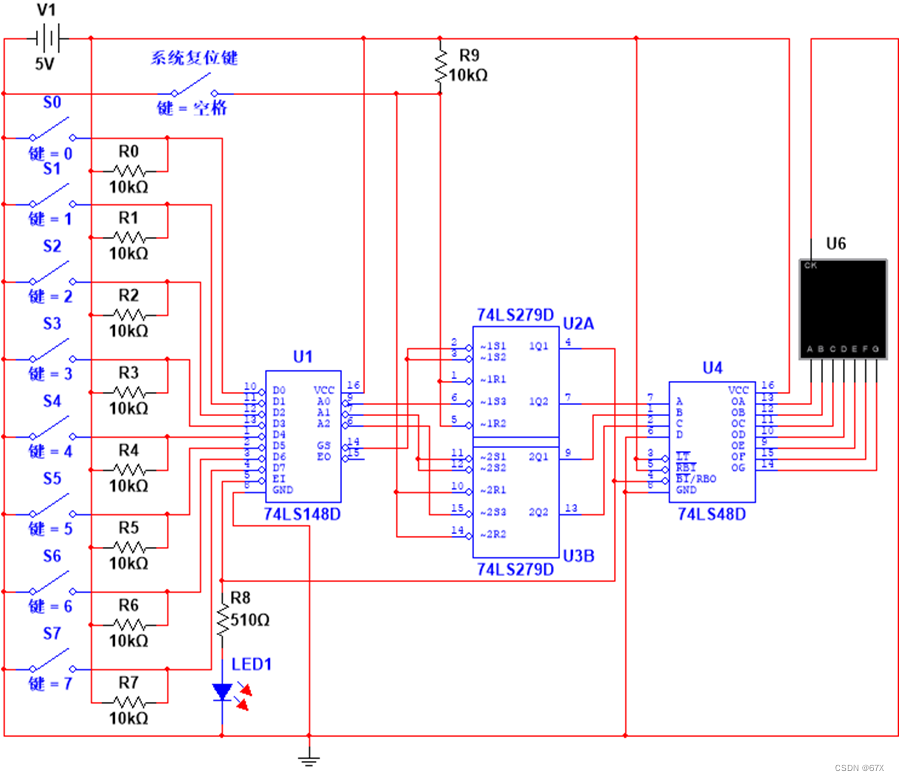

5、多路智力抢答器逻辑功能测试

用3/8译码器进行实验,虚拟仿真实验原理图如图所示:

用开关改变输入端A,B,C,D 的状态,借助指示灯和虚拟电压表。

6、实验结果与分析

多路智力抢答器功能测试表格如下:

| 输入 | 输出 | |||||||

| S0 | S1 | S2 | S3 | S4 | S5 | S6 | S7 | 显示 |

| 1 | X | X | X | X | X | X | X | 0 |

| X | 1 | X | X | X | X | X | X | 1 |

| X | X | 1 | X | X | X | X | X | 2 |

| X | X | X | 1 | X | X | X | X | 3 |

| X | X | X | X | 1 | X | X | X | 4 |

| X | X | X | X | X | 1 | X | X | 5 |

| X | X | X | X | X | X | 1 | X | 6 |

| X | X | X | X | X | X | X | 1 | 7 |

分析:S为控制清零端,当S端断开时,电路将复位完成,如果此时开关S0、S1、S2、S3、S4、S5、S6、S7的任意一个闭合(即对应选手率先按下抢答器),显示器会显示对应闭合开关的编号(即选手编号)。这里假设当S7闭合(即选手8率先完成抢答),抢答器将进入工作状态,此时如若有其他选手(假设是选手2)按下对应的抢答器(S1)时,信号进入优先编码器74LS148后传入锁存器74LS279,再经过译码器74LS48进入共阴极7段显示器,使得显示器电路处于工作状态。此时从锁存器74LS279中传出的信号为Q3Q2Q1=001, 经译码器74LS48后传入共阴极7段显示器,显示为“2”。而此时Q4=1,优先编码器74LS148的工作标志端为1(禁止状态),封锁除了S7闭合传入的信号以外的其他所有信号,并在按键抬起之后由于Q4(优先编码工作标志端)保持为1,74LS148将保持禁止状态,从而阻隔了非首次传入的所有信号,直到主持人按下S端复位电路后才能输入新的信号。

3058

3058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?