概述 本文主要针对MIPI调试过程中的常见问题进行一些分析,并结合MIPI配置参数对MIPI相关寄存器/功能的影响进行说明。

尽量为调试MIPI的同学提供一些解决问题的方向,同时能更清楚的了解在用户层配置的参数会对MIPI通路造成什么样的影响。

1 概述................................................................................................................

1.1 MIPI完整通路....................................................................................

1.2 名词缩写..........................................................................................

1.3 参数介绍..........................................................................................

1.3.1 通用参数................................................................................

1.3.2 MIPI Host专用参数.............................................................

1.3.3 MIPI Device专用参数.........................................................

2 参数配置........................................................................................................

2.1 MIPI Host配置...................................................................................

2.1.1 D-PHY clock配置.................................................................

2.1.2 IPI clock配置.........................................................................

2.1.3 HSD配置................................................................................

2.1.4 IPI配置....................................................................................

2.1.5 AdvancedFeatures..............................................................

2.2 MIPI Device配置...............................................................................

2.2.1 D-PHY clock配置.................................................................

2.2.2 PLL配置...................................................................................

2.2.3 IPI配置....................................................................................

2.2.4 VPG配置.................................................................................

3 调试建议........................................................................................................

3.1 配置流程..........................................................................................

3.1.1 RX配置流程...........................................................................

3.1.2 TX配置流程.........................................................................

3.2 错误流程.......................................................................................

3.2.1 RX流程错误.........................................................................

3.2.2 TX流程错误.........................................................................

3.3 参数错误.......................................................................................

3.3.1 Clock配置错误...................................................................

3.3.2 Frame rate配置错误.........................................................

4 错误分析.....................................................................................................

4.1 MIPI Host错误................................................................................

4.1.1 INT_ST_PHY_FATAL............................................................

4.1.2 INT_ST_PKT_FATAL.............................................................

4.1.3 INT_ST_FRAME_FATAL......................................................

4.1.4 INT_ST_PHY.........................................................................

4.1.5 INT_ST_PKT..........................................................................

4.1.6 INT_ST_IPI............................................................................

4.2 MIPI Device错误............................................................................

4.2.1 INT_ST_PHY.........................................................................

4.2.2 INT_ST_IPI

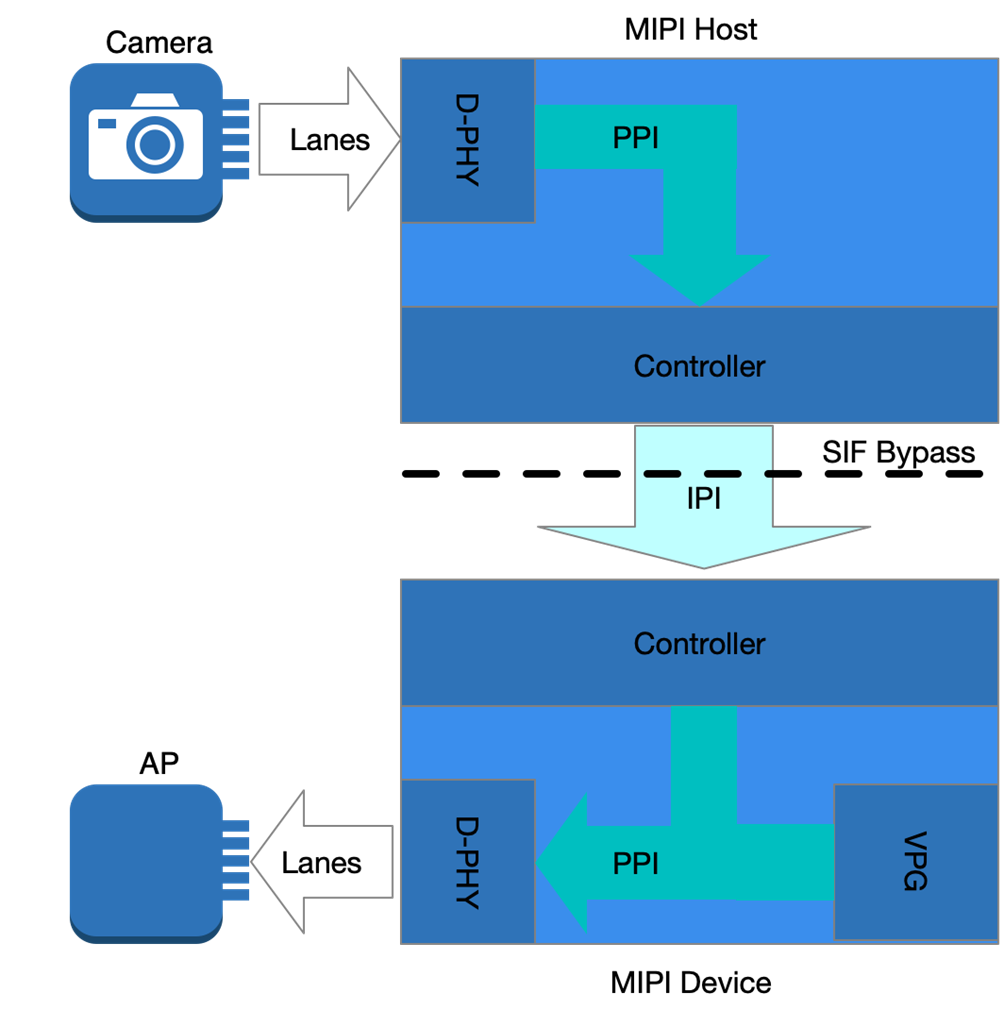

1.1 MIPI完整通路

1.2 名词缩写

PPI:PHY-Protocol Interface

IPI: ImagePixel Interface

HS: High-Speed

LP: Low-Power

RX: Receiver

TX:Transmitter

SoT: Start ofTransmission

SoF: Start ofFrame

Vsync: VerticalSynchronism

Hsync:Horizontal Synchronism

Mbps: Megabitsper second

FPS: FramesPer Second

HSA: HsyncActive time

HSD: HsyncDelay time

HBP: HorizontalBack Porch time

CLK: clock

ULPM: UltraLow Power Mode

1.3 参数介绍

1.3.1 通用参数

lane: MIPI传输中物理线对的数量

mipiclk: MIPI传输中总的Bit Rate, 单位Mbps

fps: Camera送数的帧率

width: Camera输出实际有效宽度,单位为pixel数量

height: Camera输出实际有效高度,单位为line数量

linelenth: Camera输出行长,包括有效宽度和消隐区的宽度,单位为pixel数量

framelenth: Camera输出行数,包括有效高度和消隐区的行数,单位为line数量

settle: Camera输出时,从LP到进入HS的delay

format: Camera输出图像格式,按照SIF的图像格式枚举配置

pix_len: Camera输出图像每个pixel占用的bit数,按照SIF的pixel length枚举配置

1.3.2 MIPI Host专用参数

hsa: IPI 产生的Hsync持续时间

hbp: IPI 产生Hsync到使能data_en的时间

hsd: IPI收到有效数据到产生Hsync(准备取数据)的delay时间

vc_num: Camera输入的virtual channel个数,最大支持2个

vc0_index: Camera输入的virtual channel 0需要对应的IPI index

vc1_index:Camera输入的virtual channel 1需要对应的IPI index

1.3.3 MIPI Device专用参数

format: MIPIDevice输出图像的CSI2格式,在device单独输出时使用,如IAR/VPG

width: MIPIDevice输出图像的宽度,在device单独输出时使用,如IAR/VPG

height: MIPIDevice输出图像的高度,在device单独输出时使用,如IAR/VPG

vpg: 是否开启VPG模式

ipi_lines:MIPI Device检测IPI传入图像的总行数,主要在IAR时使用

2、参数配置

本章节主要说明1.3中介绍的配置参数在MIPI配置中的使用,以及针对MIPI驱动配置的关键点进行说明

2.1 MIPI Host配置

MIPI Host与参数相关的关键配置主要分D-PHY clock的配置,IPI clock的配置,IPI及HSD的配置

2.1.1 D-PHY clock配置

关键函数:x2_mipi_dphy.c:mipi_dphy_clk_range

使用参数:lane,mipiclk

配置说明:

1.根据mipiclk/lane,计算出单lane的bit rate(laneclk)

2根据laneclk, 结合data book,选择合适的HS clock range

将range value,写入到IPS对应的寄存器中。

data book参考:RX D-PHY data book page 143, Table 5-8

2.1.2 IPI clock配置

关键函数:x2_mipi_host.c:mipi_host_pixel_clk_select

使用参数:width,height, fps, linelenth, framelenth

配置说明:

1.计算总的pixel clock, pixel clock = linelenthframelenthfps

特别说明,新的计算公式pixclk = (width + 128) * (height + 96) * fps

这里修改了pixclk的计算方式,主要是避免出现在Camera blanking过大时,HSD的计算会超出范围(最大4095)。理论上,pixel clk只要比Camera的实际传输速率大一些,就可以满足需求,但是这个方法对FPS的准确度要求较高,在项目中可以灵活调整下

1.

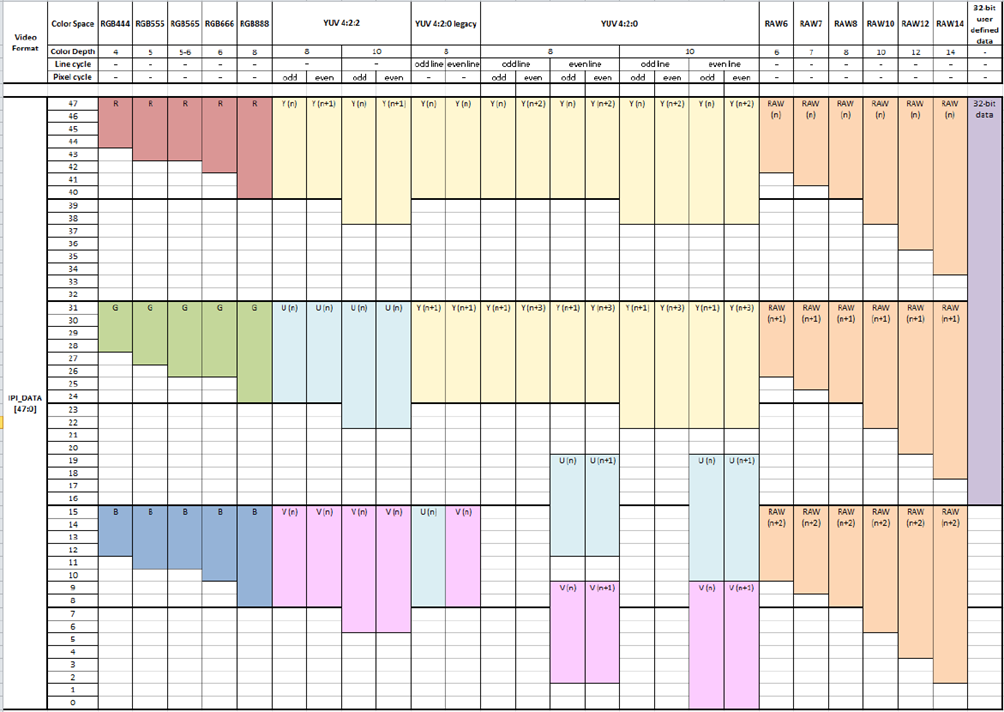

根据data book说明,48-bit的IPI在传输raw时一个clock可以传3个pixel, yuv时一个clock可以传1个pixel。ipiclk= pixel clock (YUV), ipiclk = pixel clock / 3 (RAW)

根据ipiclk,结合当前的clock tree, “向上”查找到合适的(且真实)的clock。

data book参考:csi2 host data book page 53, Figure 2-28

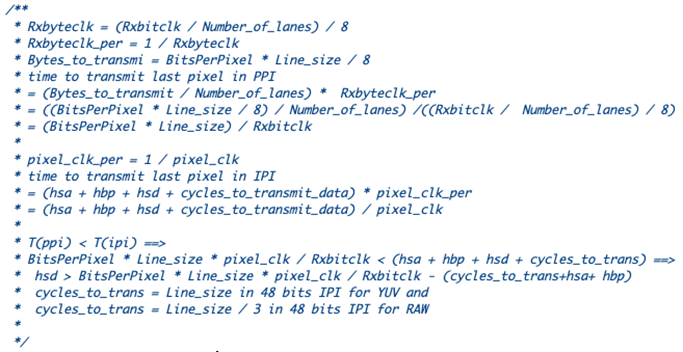

2.1.3 HSD配置

关键函数:x2_mipi_host.c:mipi_host_get_hsd

使用参数:width,fps, linelenth, framelenth, format, pix_len, ipiclk, HSA, HBP

配置说明:

1.在用户层会用format, pix_len转为CSI2的data type

根据data type, 得到bits_per_pixel和cycles_to_trans两个关键参数

计算rx_bit_clk = linelenthframelenthfps*bits_per_pixel, line_size =width

HSD > (bits_per_pixel* line_size * pixclk / rx_bit_clk)-(hsa + hbp + cycles_to_trans)

data book参考:

HostController User Guide page 66, 3.3.3.1

Host data bookpage 60, 2.6.7.1 Camera Timing

2.1.4 IPI配置

关键函数:x2_mipi_host.c:mipi_host_configure_ipi

使用参数:format,pix_len , vc_num, vc0_index , vc1_index, HSA, HBP, HSD

配置说明:

1.

在用户层会用format, pix_len转为CSI2的data type,配置到DATA_TYPE寄存器。

如果vc_num==2, 会新增配置IPI2

vc0_index,vc1_index会分别配置到IPI_VCID, IPI2_VCID寄存器,表示IPI1接收virtual chanel id为vc0_index的数据,IPI2会接收virtual chanel id为vc1_index的数据

4.

HSA=4,HBP=4为代码中的默认值,如果JSON文件有配置hsa, hbp, 则会用配置的值。HSD为2.1.3计算得出,如果JSON文件中有配置hsd,则会用配置的值。

data book参考:

Host data bookpage 150, Table 5-5 MemMap/CSI2 Registers

2.1.5 Advanced Features

关键函数:x2_mipi_host.c:mipi_host_configure_ipi

使用参数:N/A

配置说明:

1.

默认没有开启Advanced Features,controller会自动识别合适的时机来产生Vsync, Hsync信号

2.

在使用不同的camera时可能需要配置相应的line event selection,控制controller产生Vsync, Hysnc的时机。比如Video数据在Vsync/Hsync很久后才来,可能需要开启en_video;Camera确认有送Line Start/End短包,可以开启en_line_start等

data book参考:

Host data bookpage 69, 2.6.12 IPI Advanced Features

Host data bookpage 190, Table 5-30 IPI_ADV_FEATURES

2.2 MIPI Device配置

MIPI Device与参数相关的关键配置主要分D-PHY clock的配置,PLL的配置,IPI的配置, VPG模式的配置。特别说明:MIPI Device的IPI Clock来源于MIPI Host, 不用单独配置

2.2.1 D-PHY clock配置

关键函数:x2_mipi_dphy.c:mipi_dphy_clk_range

使用参数:lane,mipiclk

配置说明:

1.

根据mipiclk/lane,计算出单lane的bit rate(laneclk)

根据laneclk, 结合data book,选择合适的HS clock range

将range value,写入到IPS对应的寄存器中

data book参考:TX D-PHY data book page 142, Table 5-12

2.2.2 PLL配置

关键函数:x2_mipi_dphy.c:mipi_tx_pll_div

使用参数:lane,mipiclk

配置说明:

1.

根据mipiclk/lane,计算出单lane的bit rate(laneclk)

计算输出频率fout = PLL Fout(GHz) = data rate(Gbps) / 2

根据fout, 结合data book中频率范围的说明,得到fvco和fout合适的分频关系

4.

计算fvco = fout << vco_div

5.

根据TX默认的参考时钟TX_REFSCLK_DEFAULT=24M,计算合适的分频(n)和倍频(m)值

特别说明:为了提高计算精度,目前固定n值为12,使分频器出来频率为整数2MHz

1.

因为非浮点运算精度问题,重新计算fout = fvco >> vco_div = ((refsclk * (m + 2)) / (n + 1))>> vco_div

2.

根据data book中vco range,选择合适的vco range以及当前range的频率上限

特别说明:

结合实际使用以及公式推导,data book中的VCO range value应该为fout range

1.根据得到的fvco_max, 重新计算可以得到这个频率倍频(m)

特别说明:

这里重新根据fvco_max计算m值,是希望最终输出频率在vco range内尽量的大,因为在实测中遇到过,按照正常频点(fvco)计算出来的m直接使用的话,某些camera会遇到device报overflow的错误。请RTL分析原因中,有结论再更新。

data book参考:TX D-PHY data book page 67, PLL Programmability

2.2.3 IPI配置

关键函数:x2_mipi_dev.c:mipi_dev_initialize_ipi

使用参数:format,pix_len, width, height/ipi_lines

配置说明:

1.

在用户层会用format, pix_len转为CSI2的data type,配置到PKT_CFG寄存器

PKT_CFG可以控制Device是否发送line sync,以及隔行扫描

特别说明:如果配置了Arbitrary Value Mode, 需要额外配置START_LINE_NUM和STEP_LINE_NUM寄存器

1.配置width到IPI_PIXELS寄存器,配置height+ 1(默认)或ipi_lines到IPI_LINES寄存器

特别说明:

为了满足MIPIDevice的时序需求,SIF在BYPASSIPI数据的过程中,在每帧图像最后会多加一个hsync,否则MIPI Device这里会报underflow的错误(参考Device Controller data boot Figure 2-24, Device IPI在最后一个data_en信号之后,还需要有一个Hsync, 去取最后一行的数据,否则会提前生成Frame End packet)。同时,需要在IPI_LINES这里要配置为height + 1 (多了一个SIF在帧尾加的hsync),否则会报error lines的错误。

另外,如果在MIPIHost中开启了Advance feature中的legacy mode, Host 会在生成Vsync的同时多生成一个Hsync, 此时MIPI DeviceIPI_LINES这里要配置为height + 2(1个Host在帧头加的Hsync, 1个SIF在帧尾加的Hsync)

data book参考:

DeviceController data book page 41, 2.3 Image Pixel Interface

DeviceController data book page 122, 5.1 memmap/CSI2 Registers

HostController data book page 57, 2.6.6 Vertical Timing

2.2.4 VPG配置

关键函数:x2_mipi_dev.c:mipi_dev_initialize_vgp

使用参数:format,pix_len, width, height, linelenth, framelenth

配置说明:

1.

在用户层会用format, pix_len转为CSI2的data type,配置到PKT_CFG寄存器

配置width到PKT_SIZE, height到ACT_LINES寄存器

VPG模式下需要自己配置HSA/HBP/HLINE/VSA/VBP/VFP,目前HSA/HBP/VSA/VBP是固定的。

4.

计算HLINE, 根据data type和linelenth计算一行的时间(in lane byteclk)

5

计算VFP, 根据framelenth计算VFP

6

目前VPG模式配置为Vertical Color Bar, 可以根据需求调整

data book参考:

DeviceController data book page 51, 2.4 Video Pattern Generator

DeviceController data book page 122, 5.1 memmap/CSI2 Registers

3、调试建议

本章节主要介绍在MIPI调试中容易出错的关键点。主要介绍下Host/Camera,Device/AP Rx的流程关系,以及参数配置错误可能带来的问题。

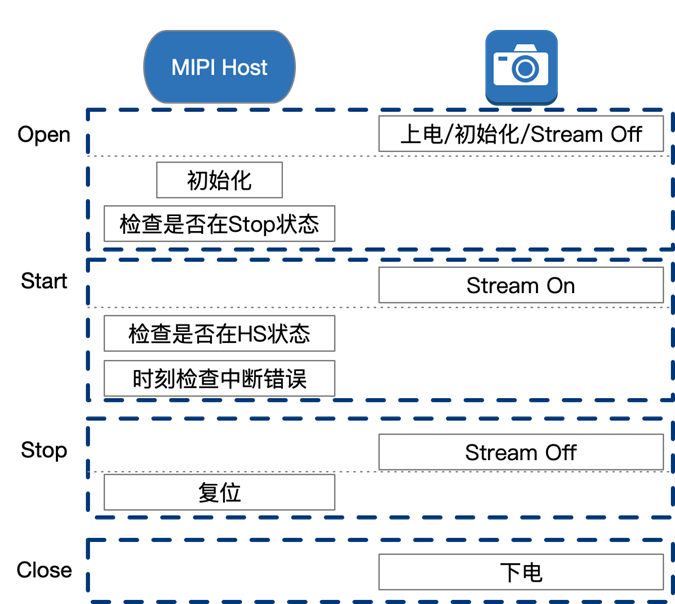

3.1 配置流程

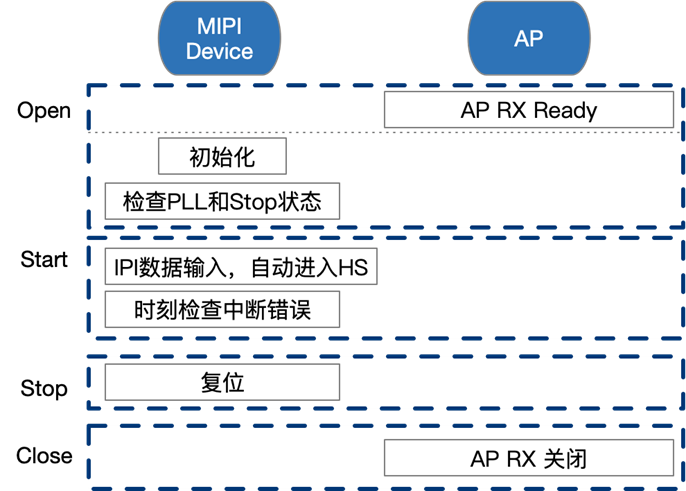

3.1.1 RX配置流程

参考HostController User Guide 3.3 Programming Flow

MIPI Host的配置流程大体分为3个步骤

1、初始化: Start up -> Initialize -> Configure IPI

此时Host会Check 线上Stop状态

此时Camera应该在LP11, 即Camera处于Stop状态/Stream Off状态

2、开始工作: Start HS Reception -> Detect Errors

此时Host会Check 线上HS状态,并注册系统中断,如果收到中断要及时查看对应的中断状态寄存器

此时Camera应该在HS mode,即Camera开始送数/Stream On状态

3、结束: Stop HS Reception -> Reset Controller/PHY

此时Camera应该在LP11,即Camera处于Stop状态/Stream Off状态,掉电也可

3.1.2 TX配置流程

参考DeviceController User Guide 3.2 Programming Flow

MIPI Device的配置流程大体分为3个步骤

1.初始化: Initialize PHY -> Initialize Controller -> Wake Up

此时Device会检测PLL Lock状态并确认是否线上进入LP11, 即处于Stop状态, 等待IPI数据输入

此时AP侧RX应该已经初始化完毕,并处于等待数据输入的状态

2.开始工作:

IPI数据到Device时,Device会自动进入HS状态并开始向外输出数据

3.结束: Reset Controller/PHY

3.2 错误流程

3.2.1 RX流程错误

1.Camera在MIPI Host初始化完毕前就开始送数

结果:MIPIHost在初始化的过程中或者刚初始化完内部信号不稳定时,收到Camera的数据,导致PHY或IPI出现不可恢复的错误。

建议:按照3.1.1的顺序对Camera/Host进行配置,其中Host初始化时建议不要绕过Stop和HS的状态检查,避免出现一些不可预知的问题

2.在MIPI Host开始正常工作时,不断的重启Camera

结果:Camera再重启/上下电时,不能保证Camera本身TX部分数据的完整性和准确性,可能会对MIPI Host的工作状态造成影响

建议:Camera启/停时,最好按照3.1.1的顺序对MIPIHost也进行同样的启/停操作

3.2.2 TX流程错误

1.在AP侧RX还没有准备好时,Camera->Host->SIF->Device已经开始输出

结果:会造成AP侧RX出现和我们MIPI Host同样类似的问题,如3.2.1

同时,有测量过,如果AP侧RX没有准备好,或者AP侧悬空时,MIPI Device的输出信号会异常,如Clock Lane无信号,Data Lane数据异常的情况

3.3 参数错误

3.3.1 Clock配置错误

涉及参数:mipiclk,lane, settle

1、

lane speed= mipiclk/lane,这个参数会用于配置Host/Device的PHY基本配置,涉及Host/Device PHY的HS clock range, Device PHY的PLL计算,同时lane数也会配置到Host/Device PHY的相关寄存器。这2个参数必须要正确!!!

2

2、settle, 正常这个参数PHY可以自动适配,但是有些极端情况下PHY适配不了这个参数,因此在驱动中开启了settle的配置,正常需要Camera厂商提供这个参数,单位为PPI clock,如果厂商未提供,可以试错,这个值的范围很小且鲁棒性尚可。

错误情况:如果以上参数配置错误,会导致PHY在接收/解析CSI2数据时直接出错,报各种PHY/PKT/FRAME Fatal的异常中断。

3.3.2 Frame rate配置错误

涉及参数:width, height, linelenth, framelenth, fps

1.

对于MIPI Host,这些参数会参与IPI Clock以及HSD的计算,如果配置错误,会导致IPI报overflow/underflow,最终影响数据向SIF传输的正确性

2.

对于MIPI Device, width/height是直接配置到IPI寄存器的,直接影响最终输出实际尺寸。linelenth和framelenth会在VPG模式时用到,模拟正常Camera输出的blanking

4、错误分析

本章节主要针对调试中常见的错误LOG进行简要的说明和分析,并提供一些之前总结的解决思路

4.1 MIPI Host错误

参考HostController User Guide page 115 Error Handling

Host data bookpage 76, 2.9 Error Detection

Host data bookpage 150, Table 5-5 MemMap/CSI2 Registers

MIPI CSI-2 Specificaation

4.1.1 INT_ST_PHY_FATAL

错误描述:在datalane上SOT检测出错且无法修复,报出ErrSotSyncHS, SOT为LP-HS的必有数据包,出错会影响数据接收

错误分析:

1.

主要检查PHY Clock以及settle的配置,参考3.3.1

如参数配置确认无误,根据3.1.1确认Camera/Host初始化时序

如果前2条确认无误,需要示波器测量Camera输出的数据是否正常以及信号质量

4.1.2 INT_ST_PKT_FATAL

错误描述:数据传输中和Packet相关的错误

1.

数据包中ECC错误,报出ErrEccDouble

数据包中CRC校验错误,报出ErrCrc。

错误分析:

1.

主要检查PHY Clock以及settle的配置,参考3.3.1

如参数配置确认无误,根据3.1.1确认Camera/Host初始化时序

如果前2条确认无误,需要示波器测量Camera输出的数据是否正常以及信号质量

4.1.3 INT_ST_FRAME_FATAL

错误描述:数据传输中Frame相关的错误,包括:

1.

整帧数据中有CRC错误,报出ErrFrameData:

SOF/EOF没有配对,比如连续收到两次同一个VC的SOF没有收到EOF,报出ErrFrameSync

FrameNumber顺序错误,比如前一帧SOF的framenumber是1,下一次收到的frame number变成了4

错误分析:

1.

主要检查PHY Clock以及settle的配置,参考3.3.1

如参数配置确认无误,根据3.1.1确认Camera/Host初始化时序

如果前2条确认无误,需要示波器测量Camera输出的数据是否正常以及信号质量

4.1.4 INT_ST_PHY

错误描述:datalane上的Warning

1.

SOT检测出错,但是PHY可以自动修复(此时数据也是不可信的),报出ErrSotHs

2.

Escape进入错误,Escape cmd只有在ULPM下有用,报出ErrEsc

错误分析:

1.

主要确认Camera/Host初始化时序

如果时序确认无误,需要示波器测量Camera输出的数据是否正常以及信号质量

4.1.5 INT_ST_PKT

错误描述:数据传输中和Packet相关的Warning

1.

Data type不识别或者不支持,报出ErrID。

出现一个ECC错误,已经自动修正了,报出ErrEccCorrected

错误分析:

1.

确认pixlen, format配置是否正确,比如Camera送RAW8,Host却配为RAW12。

确认Camera/Host初始化时序

3如果时序确认无误,需要示波器测量Camera输出的数据是否正常以及信号质量

4.1.6 INT_ST_IPI

错误描述:IPI相关的Warning

1.FIFOunderflow: IPI在取到足够的pixel数量前FIFO已经空了

错误分析:IPIClock过快,或者HSD过小,导致PPI的数据还没有送完,IPI已经(提前)把FIFO的数据取完了。结合2.1.2和2.1.3,检查width,height, linelenth, framelenth, fps的配置是否正确

1.FIFO overflow:FIFO溢出

错误分析:IPIClock过慢,或者IPI取数慢了,比如HSD过大或者在收到Hsync后过了太久(超过根据blanking计算出的HSD时间太多),导致FIFO已经被塞满后IPI还没开始取数或者IPI取数速度低于PPI填充FIFO的速度导致FIFO被塞满。结合2.1.2和2.1.3,检查width, height, linelenth, framelenth, fps的配置是否正确。

另外可以通过2.1.5介绍的ADV_FEATURE寄存器的配置,调整Hsync产生的时机

1.Frame SyncError: 新的Vsync来的时候,上一帧还没有结束

错误分析: 没有遇到过这种情况,只能从字面上推测,可能某些情况下会和ErrFrameSync的情况一起出现

1.FIFO nempty:在新的Vsync来的时候,FIFO里还有数据

错误分析:通常和FIFO Overflow or Underflow一起出现,尤其是Overflow的情况,overflow时FIFO始终处于full的状态,所以一定也会报出nempty。underflow时,因为IPI在FIFO数据填充完前已经结束取数了,所以在新的Vsync来时FIFO里还有上一帧最后被填进去的一些数据。

在X1时遇到过FIFO nempty独立出现的情况,目前X2还没有遇到过。这种情况的发生应该主要出现在3.2.1 流程上的一些问题,在Host正常工作前,FIFO里已经被填了一些数据。开启MEM_FLUSH寄存器的auto flush功能,可能会缓解

4.2 MIPI Device错误

参考DeviceController data book page 122, 5.1 memmap/CSI2 Registers

如果再调试过程中已经出现MIPI Host报错,那么MIPI Device的报错不用继续分析,Host报错会导致IPI上的数据已经异常,继续分析MIPI Device报错意义不大

4.2.1 INT_ST_PHY

错误描述:TXD-PHY上的错误

1.

TX想要进入LP1, 即想要将line拉高时,检测到了RX端的控制争夺(拉不起来),报errcontentionlp1

2

TX想要进入LP0, 即想要将line拉低时,检测到了RX端的控制争夺(拉不下去),报errcontentionlp0

3

TX想要进入HS,检测到了RX端的控制争夺,导致HS timeout

错误分析:

目前没有遇到过这种错误,但是从字面看,应该是AP侧RX处于错误的状态且对MIPI Lane有强制动作(如拉高,拉低等),导致TX这里进行传输时出现无法控制Lane上行为。如3.2.2中描述,建议遵循3.1.2的配置流程

4.2.2 INT_ST_IPI

错误描述:IPI相关的Warning

1.errpixel:IPI收到的pixel数与配置到寄存器的pixel数(行长)不符

错误分析:主要检查配置参数width是否错误,width大了和小了都会报这个错误。如果width偏差过大,还会报overflow的错误

2.fifo_overflow:FIFO溢出

错误分析:主要检查配置参数width是否错误,width如果配置比实际大很多,会报errpixel的同时报出overflow。另外有遇到过在低频情况时(400Mbps/Lane), 如果如2.2.2 PLL配置中m值过小,也会报出这个错误,可以理解为取数据速度比送数速度慢。目前驱动中PLL的计算已经能适配多个项目,如果后续项目遇到Device Clock的问题修改了计算方式,导致报出overflow的问题可以参考这里。

3.errline:IPI收到的line数与配置到寄存器的line数不符

错误分析:主要检查配置参数height是否错误,height大了和小了都会报这个错误。如果height偏小,还会报underflow的错误

4.fifo_underflow: IPI在取数时FIFO为空

错误分析:主要检查配置参数height是否错误,height偏小,在报出errline的同时会报underflow。另外,如果遇到只报underflow的情况,参考2.2.3中描述,确认SIF是否在帧尾加了Hsync。

文章来源:https://blog.csdn.net/qq_1335857320/article/details/129368885,

作者:qq_1335857320

《Android Camera开发入门》、《Camx初认识》已经上架,可以点击了解 -> 小驰成长圈 |期待见证彼此的成长

觉得不错,点个赞呗

3348

3348

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?