DVT特性

Alt + /:自动补全(点一次:信号变量、方法,点两次:代码模板,点三次:例化)

右键->Source->Quick Fix或者Ctrl+1:快速修正错误

代码模板

模板样式可以在全局代码模板中更新

windows->Preferences->DVT->Code Template

代码模板的插入可以在左侧Code Template窗口拖拽到源代码处

代码格式化

就是重新排版

Preference->DVT->SV->Editor->Formatting

使用:右键需要格式化的文件,找到format source

方法覆盖

指示该方法时覆盖了父类的方法

- 绿色三角形表示被覆盖的方法(绿色就是父类)

- 黄色三角形表示覆盖的是父类未声明为virtual的方法(同名,但子类和父类没关系)

- 白色三角形表示是预定义的方法

对类点击ctrl->open Super Implementation就可以跳转到父类

右键方法名->show->layer可以展示他的层次

使用跟踪

右键,show->usage可以查看在哪用过。可用于类型、变量等等

语义查询

ctrl+h可以搜索,也能使用正则表达式模糊搜索

重构

批量修改某一类型的变量

右键->Refactor->Rename

为模块添加新端口或参数

选中某个模块,右键,Refactor->Add port或parameter

查看历史版本

右键编码区的空白处,Compare with->Local History

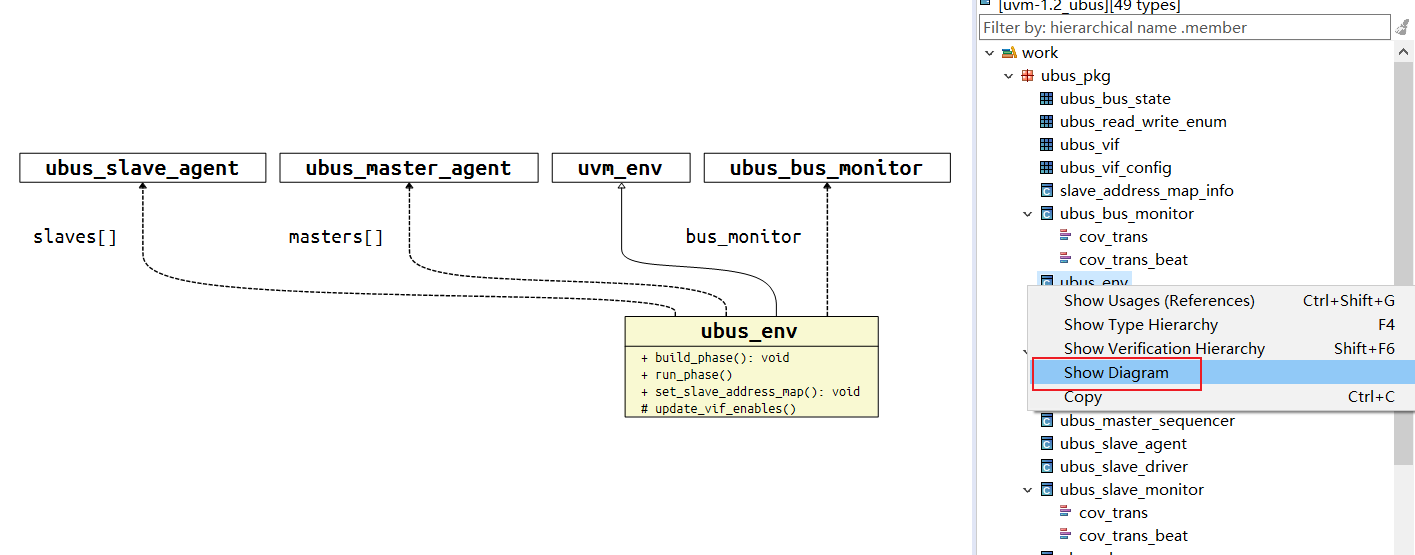

打开类UML的图

实线是ubus_env的父类,虚线应该是包含的类

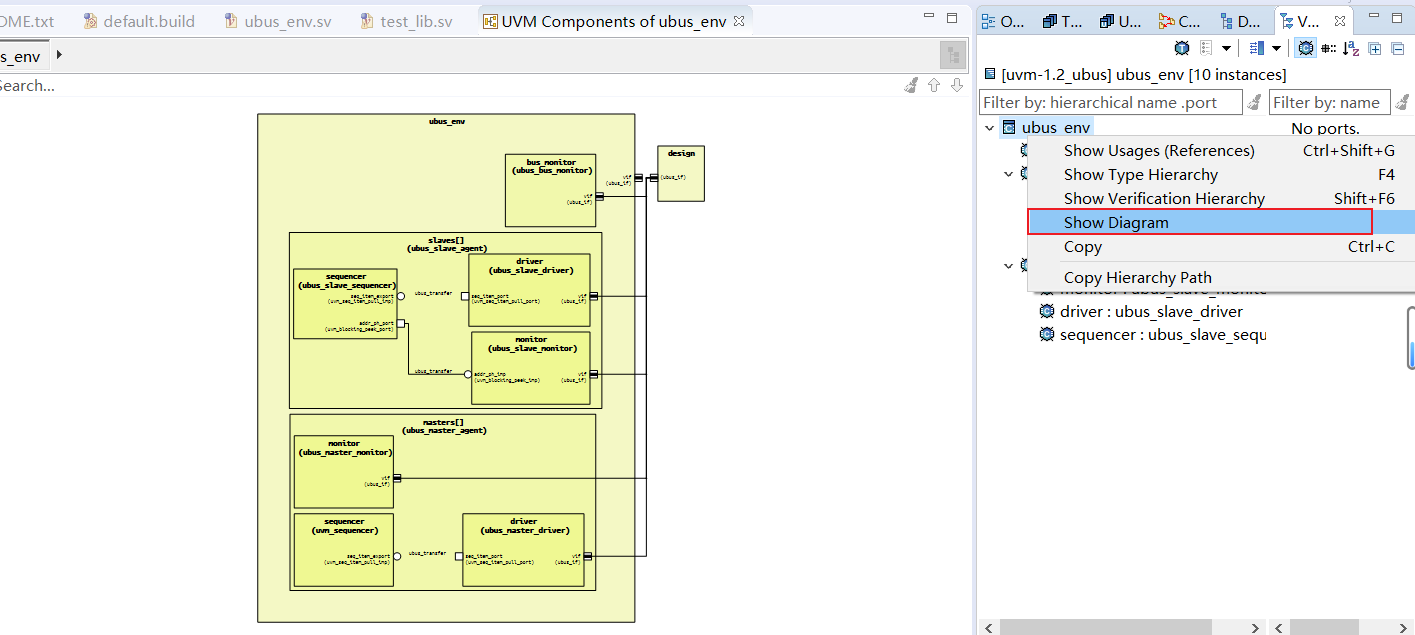

验证结构UML图

点击上一节的Show Verification Hierarchy,再如下图方式操作

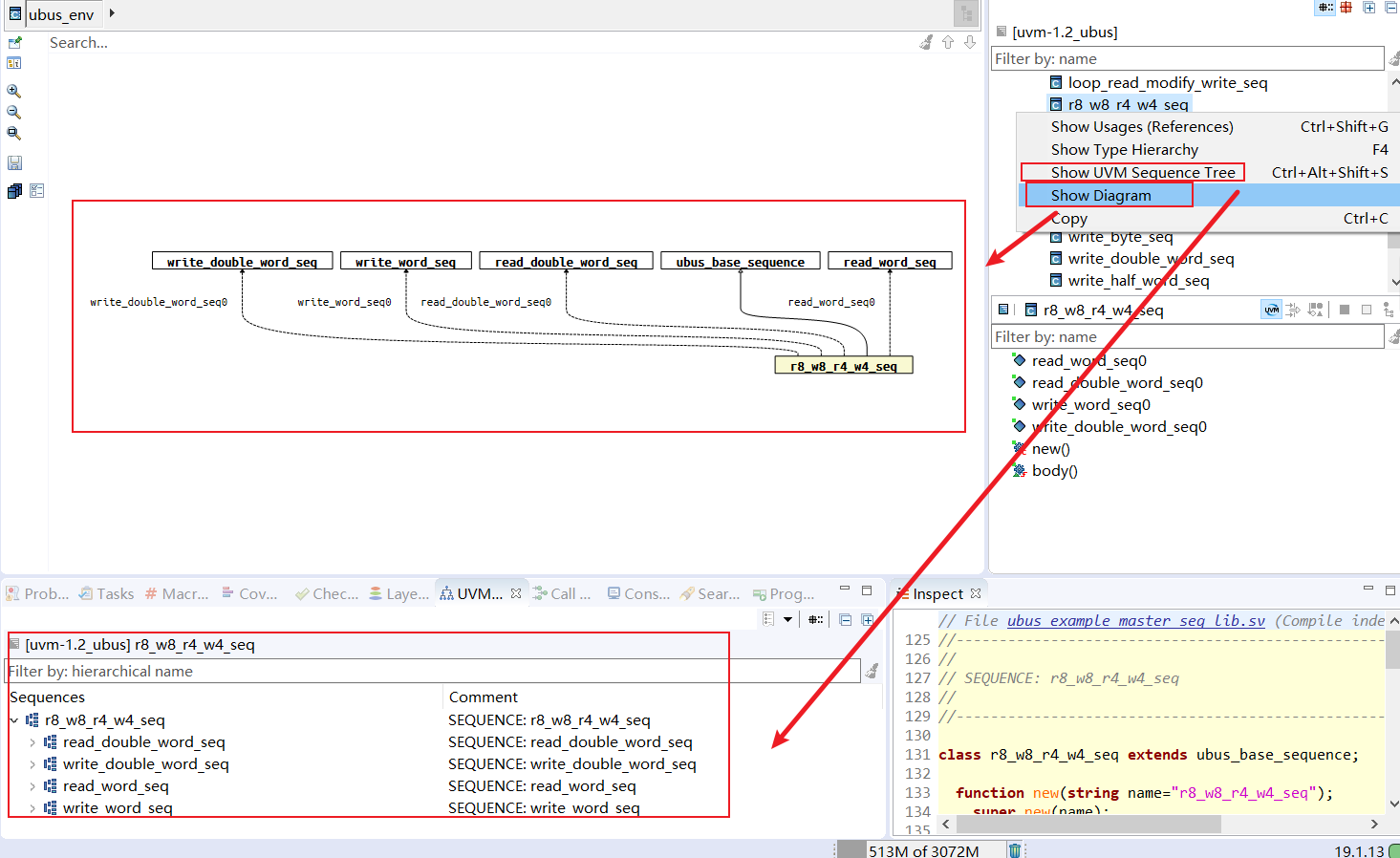

sequence UML图

可以看出seq是怎么构成的,但是不能实时分析发送了几次seq(VCS可以)

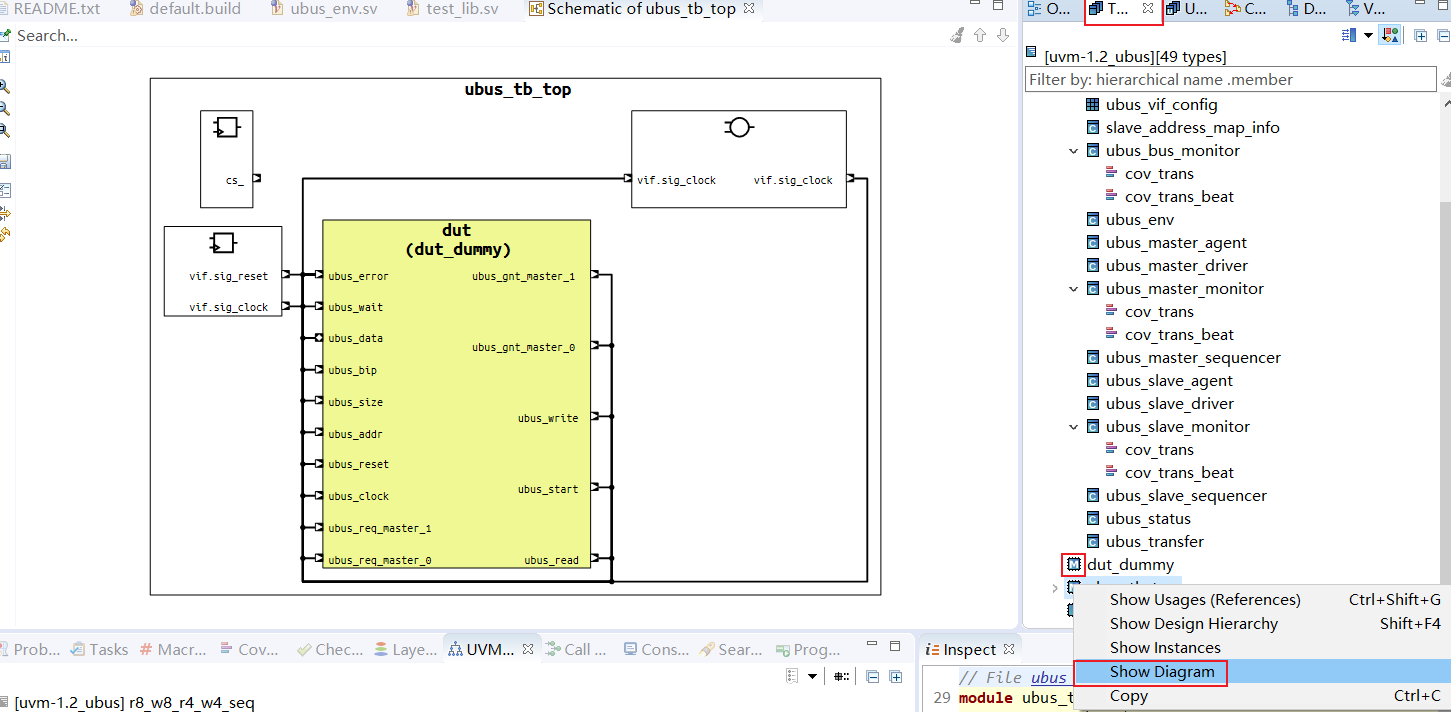

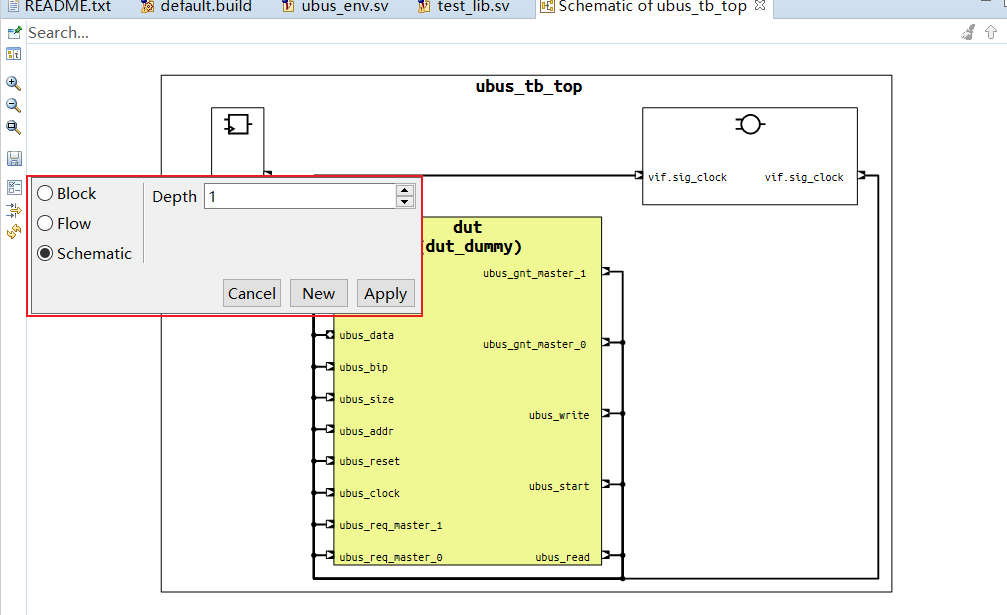

设计图

设计的文件是M图标

可以查看数据流向

引入SV实验

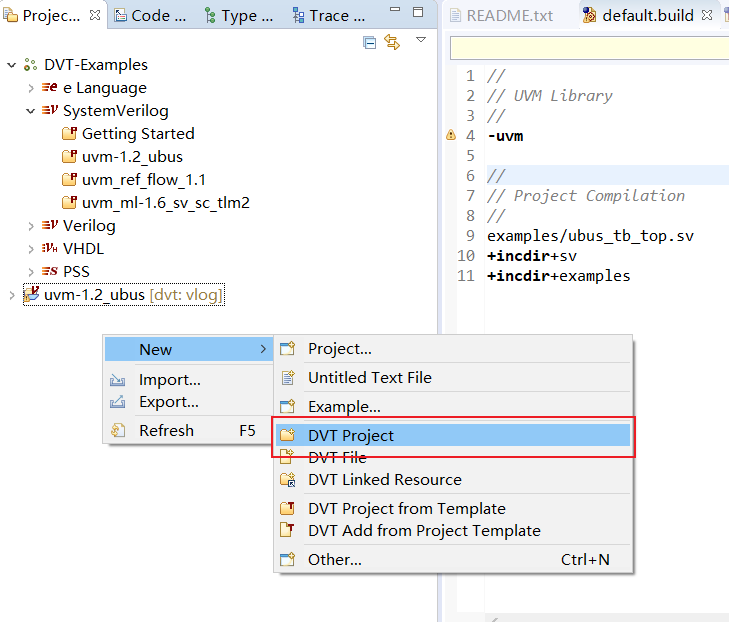

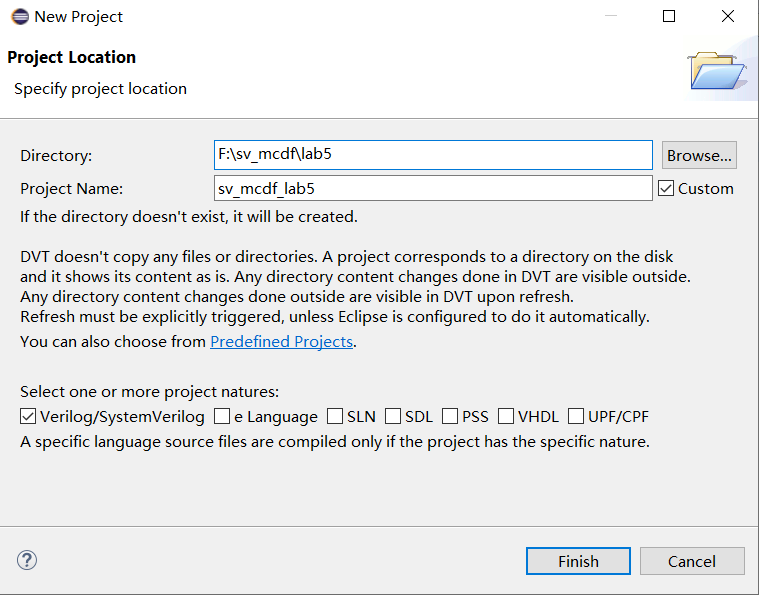

①创建工程

② 选择创建工程的路径,注意:不能和workspace同一个路径

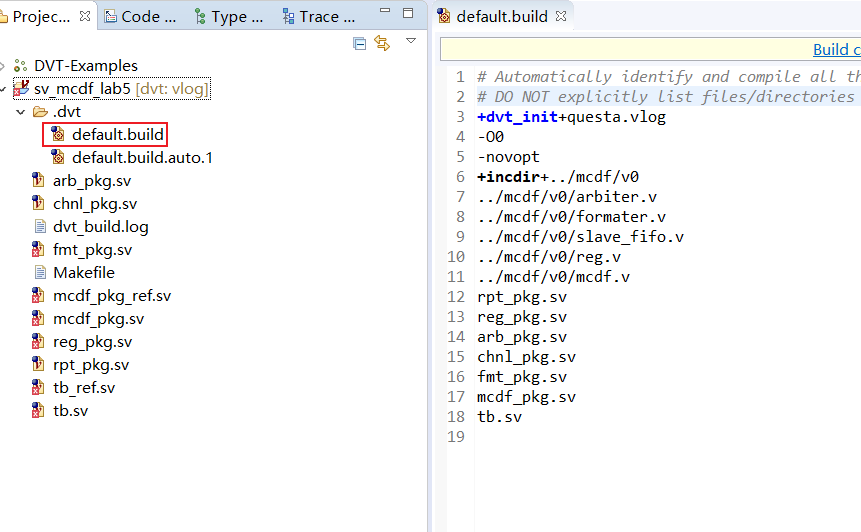

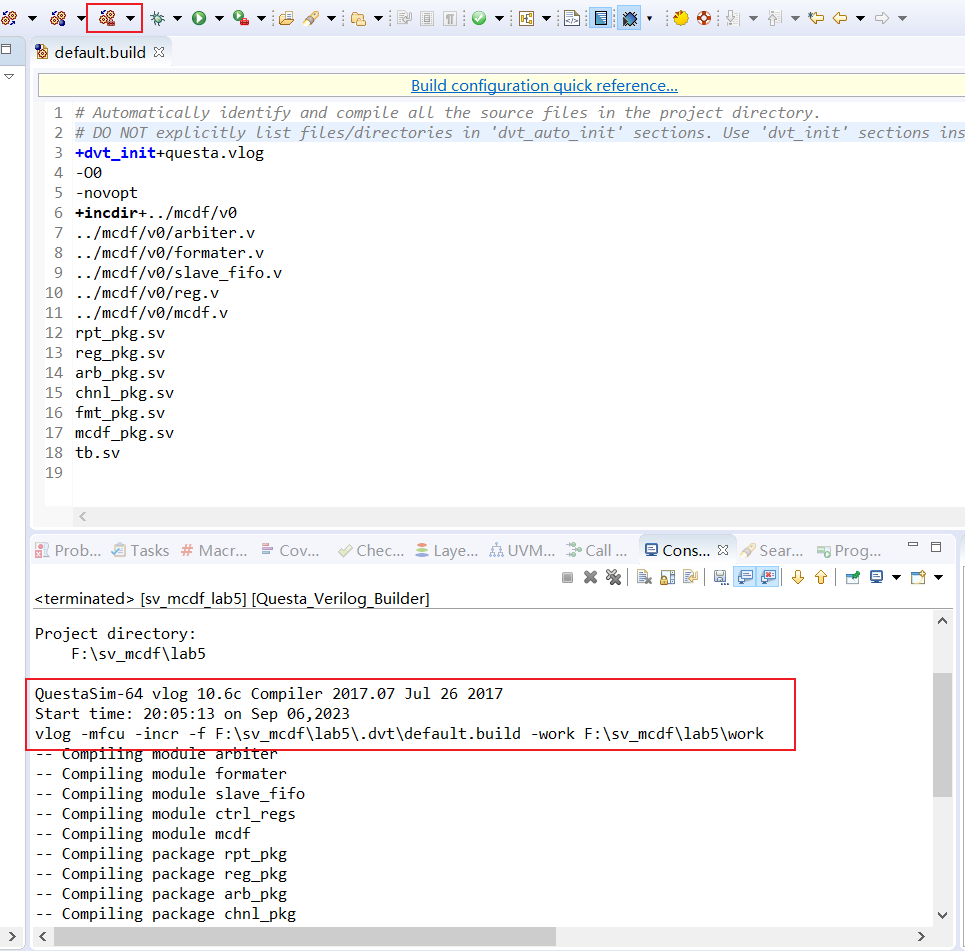

③ 在default.build输入以下编译命令

+dvt_init:表示调用默认的build

+questa.vlog:表示采取questasim的兼容模式,questa可以识别下面的指令

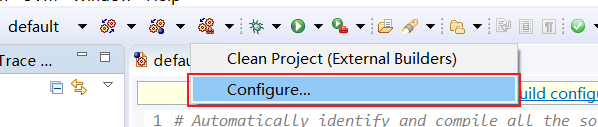

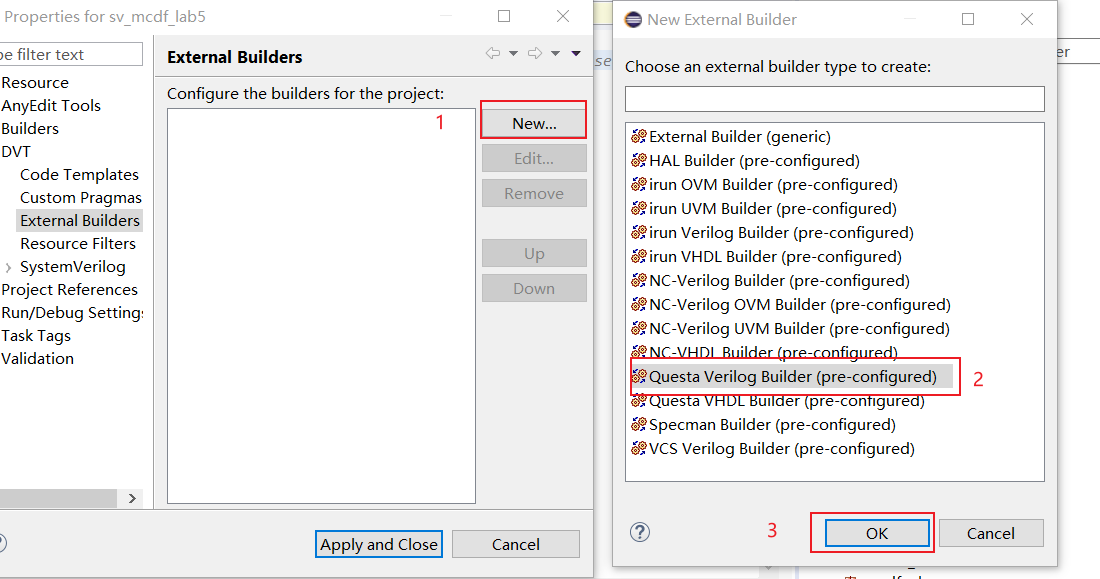

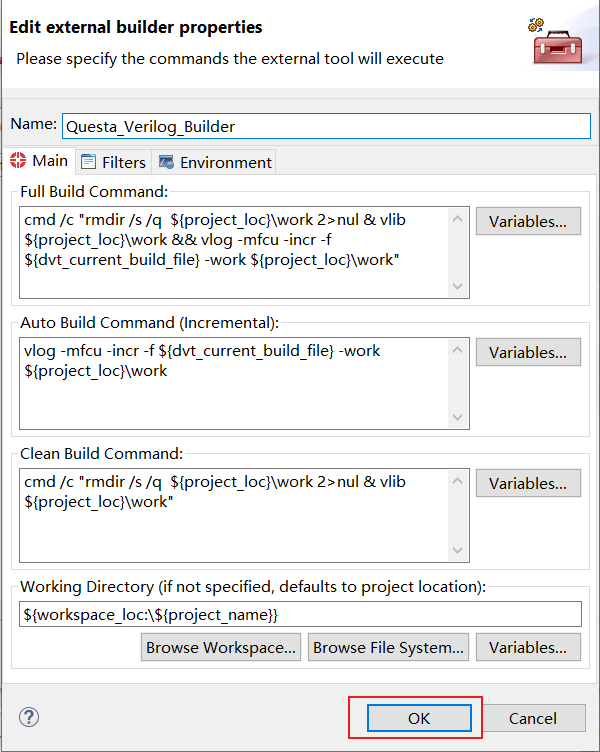

④ 添加外部build,此处用questasim

⑤ 点击外部编译,发现questa能够识别到vlog

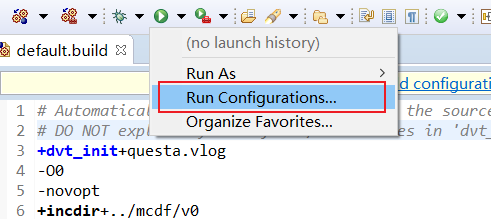

⑥ 创建run指令

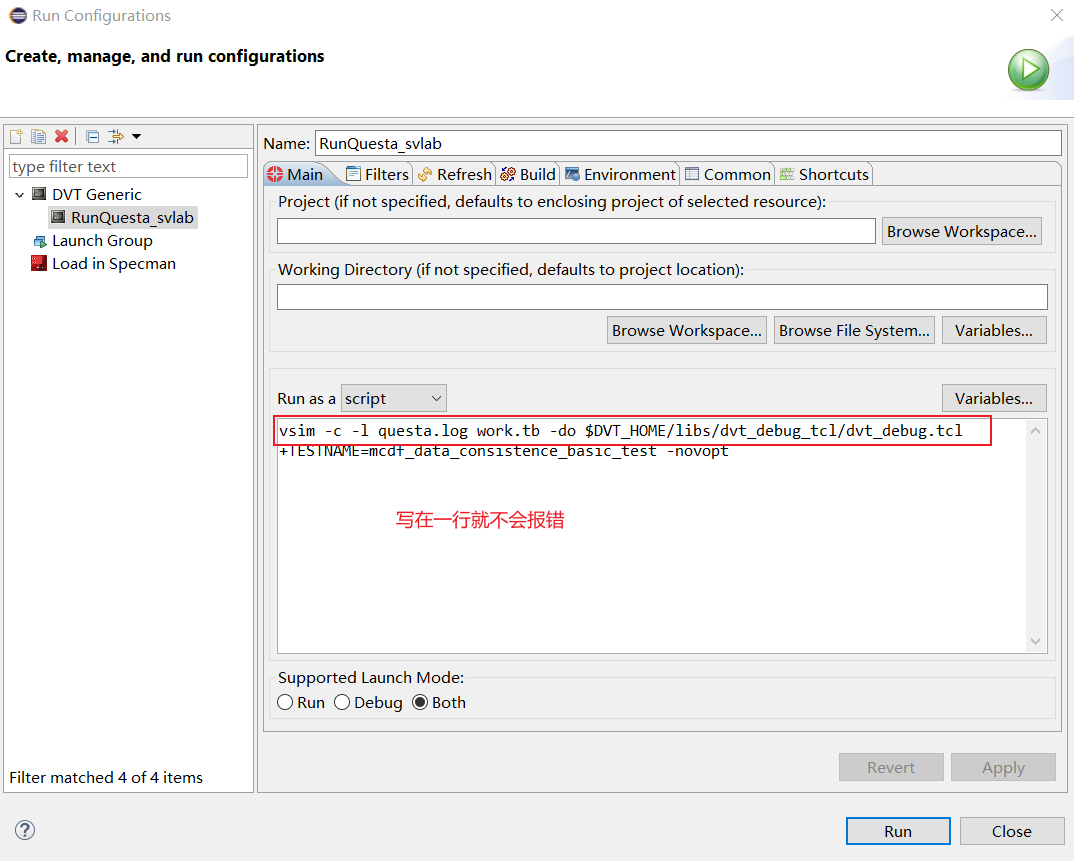

视频中讲错了,按视频中回车后输入$DVT_HOME会报错,所以我不换行输入,(别加回车,都会报错!)

sv的应该为

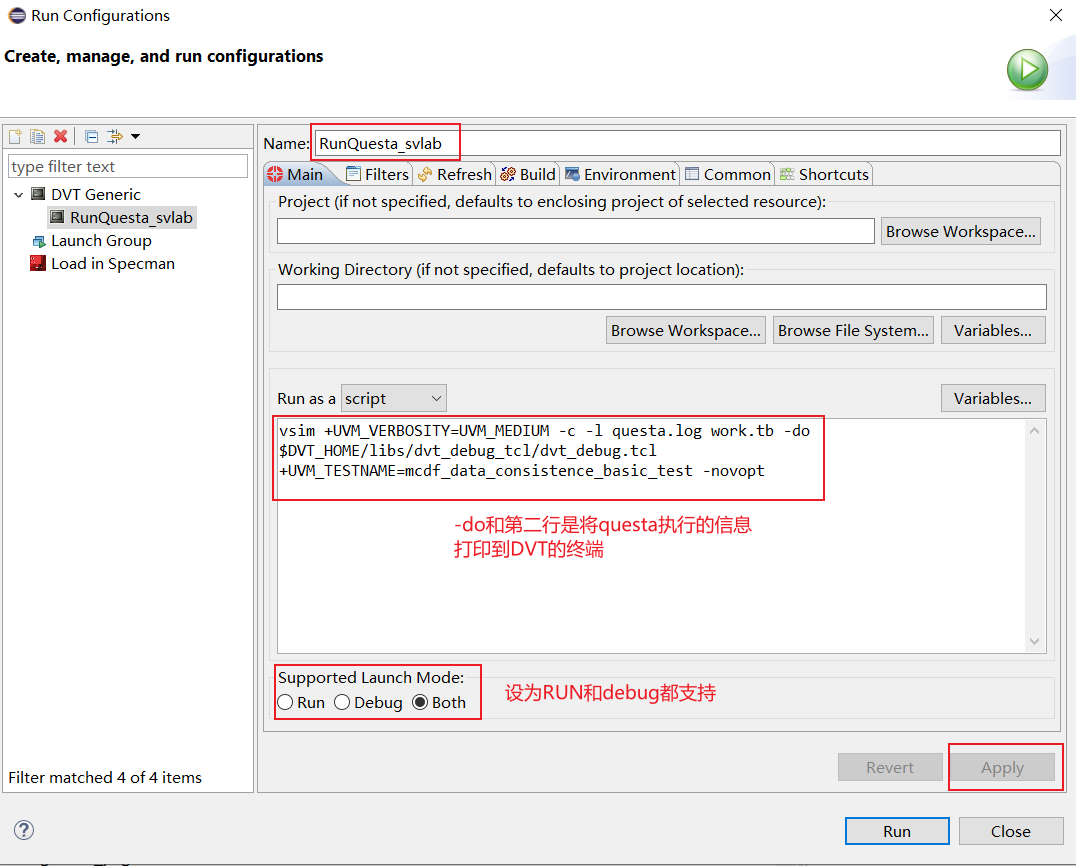

UVM的指令(按下面的指令输入,但是别加换行)

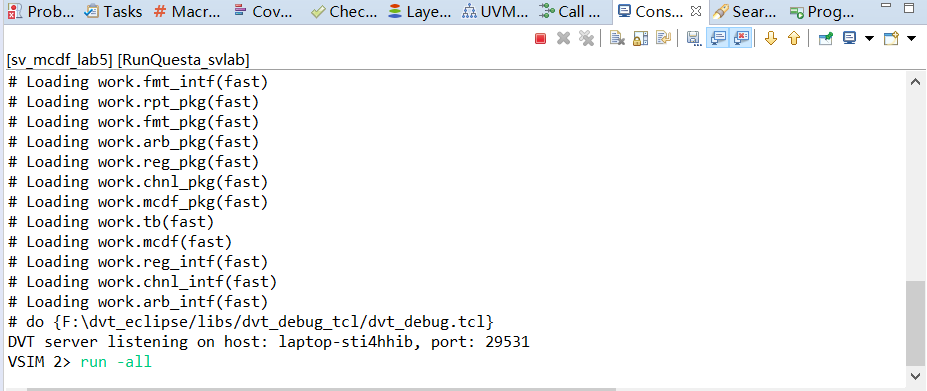

然后输入run -all

803

803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?