第 5 章 存储器系统与接口

1. 存储器系统概述

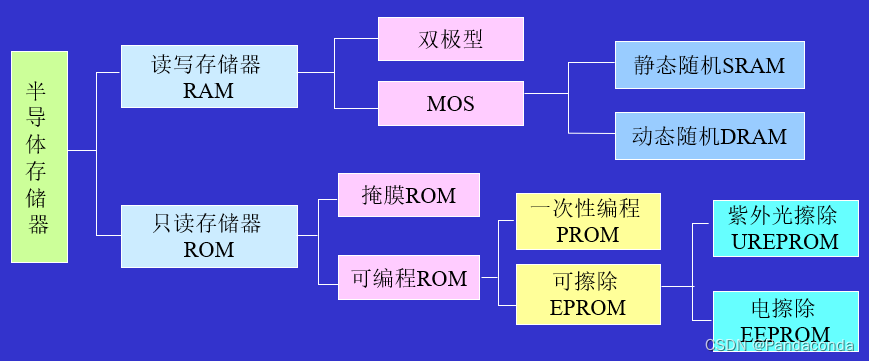

(1)半导体存储器的分类及特点

ROM 和 RAM 的区别 (考点):

| ROM | RAM |

|---|---|

| 只读 | 只写 |

| 固定的数据 | 临时的数据 |

| 掉电后,数据还在 | 掉电后,数据不在 |

2. 储存系统的一般概念(现代)

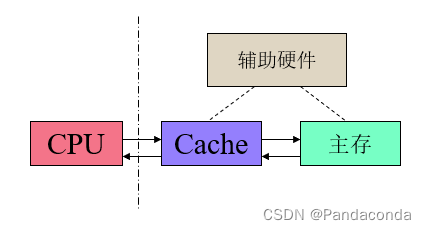

(1)Cache 存储系统 —— 主存层次

1、局部化访问原理:CPU 只访问一部分的地方即 Cache 高速缓存区。

2、一次性取指令 128B 到 Cache 中,提高命中率。

如果 Cache : 内存 的容量比为 1 : 128 ,那么命中率将大于 90% 。

eg. (考点) 若 Cache 存取时间为 5ns ,内存的存取时间为 50ns ,且命中率为 90% ,那么整个存储器系统的存取时间为:

T = 5ns × 90% + 50ns × 10% = 10ns

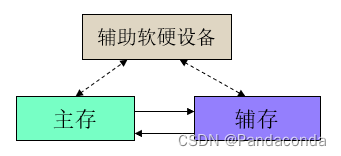

(2)虚拟存储系统 —— 辅存层次

3. 随机储存器 RAM(ROM)

(1)SRAM 和 DRAM 的区别 (考点)

| SRAM | DRAM |

|---|---|

| 成本高 | 集成度高,成本低 |

| 速度快(ns) | 速度慢(n+ns) |

| 稳定 | 不稳定,定时刷新 |

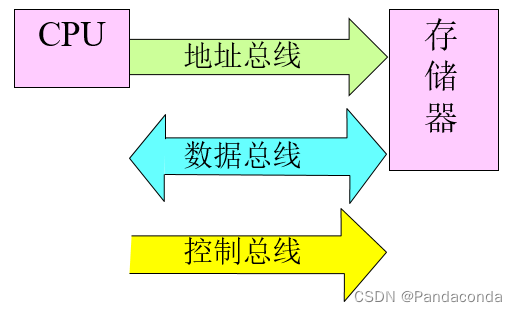

(2)储存器的基本组成

1、芯片管脚

| 地址脚 | 数据脚 | 控制脚 |

|---|---|---|

| 决定容量 | 决定位数 | 决定类型 |

2、SRAM 常用芯片 —— 静态 RAM

eg. 将 1024 × 1 位的芯片组成 1024B 的储存空间,需要 8 块芯片,10 根地址线。

8 位芯片常用。

62128:16K × 8 位(14 根地址线)

62256:32K × 8位(15根地址线)

考点: 例如 6264 即 8K × 8位有多少管脚,一共有 28 条引脚,其中 13 根地址信号线,8 根数据线,4 根控制线

3、DRAM 常用芯片 —— 动态 RAM

典型的动态 RAM 芯片如 Intel 2116(16K × 1 位),21256(256K × 1 位)。

1 位芯片常用,地址管脚复用。

(3)SRAM 芯片应用

1、译码方法 —— 线选法

CPU中用于“选片”的高位地址线(即存储器芯片未用完地址线)若一根连接一组芯片的片选端。这种方法称之为线选法。

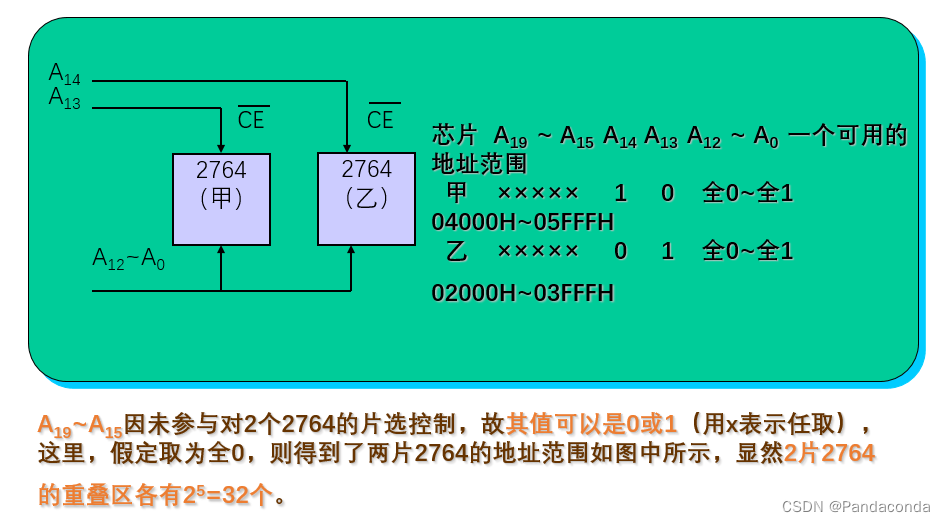

eg.(考点) 用 2764 组成 16kB 的 rom 空间,令 A13 和 A14 分别接芯片甲和乙的片选端。可能的选择只有 10(选中芯片甲)和 01(选中芯片乙)。

① 片选地址线决定容量(范围)

② 参与片选的地址线决定位置

③ 没有参与片选的地址线决 2n

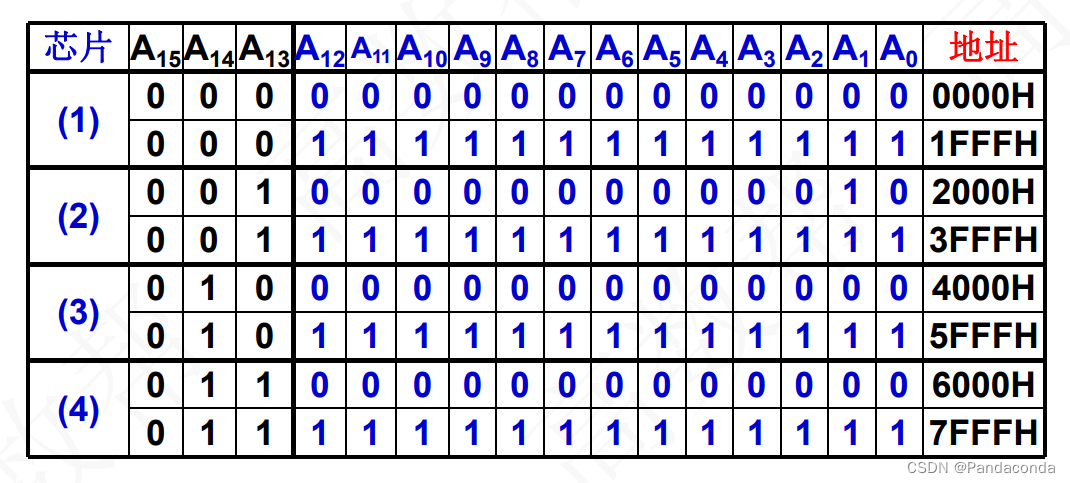

2、译码方法 —— 全译码

地址总线中除片内地址以外的全部剩余高位地址参加译码,产生各存储芯片的片选信号。

特点:地址连续唯一确定,无地址间断和地址重叠。

例如:CPU地址总线为 16 位,存储芯片容量为 8KB 。采用全译码方式寻址 64KB 容量存储器。

3、设计

① 地址分配表

② IO/M 连接

③ 地址范围

3270

3270

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?