课题:RType ALU设计与验证

一、实验目的

1.掌握将组件按需要组合起来,以R类型指令实验为例,实现指令处理器功能

2.掌握寄存器组、ALU单元的工作原理和作用以及组件的组合方法

3.修改本实验中的指令,实现更多的功能

二、实验设备

1.装有ISE Design Suite 14.7的计算机一台

2.EDK-3 SA ISE实验平台

三、实验任务

1.对RType ALU模块进行仿真,验证功能的正确性

2.分析RType ALU功能,修改测试代码,计算

St3&Sk0

St5+Sgp

根据仿真结果验证其正确性

四、实验原理

实验原理

R类型指令主要执行寄存器间的算术逻辑运算,其原理如图所示。

从指令中取得源寄存器号,在寄存器组中读出相应的内容,送到ALU中计算,并将结果回写到寄存器中。ALU的控制通过指令中的功能字段实现。

所需要的组件有:寄存器组、ALU与ALU控制器。

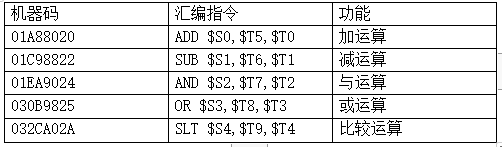

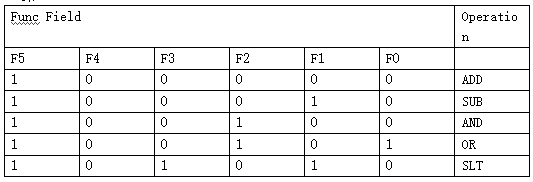

本实验主要实现以下五条指令:

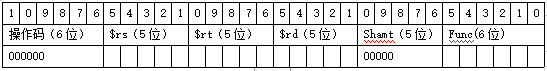

指令各个域定义:

OP:指令的操作码,默认为0

$rs:第一个源操作数寄存器

$rt:第二个源操作数寄存器

r

d

:

目

的

操

作

数

寄

存

器

S

h

a

m

t

:

移

位

位

数

,

在

本

次

实

验

中

默

认

为

0

F

u

n

c

:

功

能

域

,

本

次

试

验

的

任

务

就

是

实

现

rd:目的操作数寄存器 Shamt:移位位数,在本次实验中默认为0 Func:功能域,本次试验的任务就是实现

rd:目的操作数寄存器Shamt:移位位数,在本次实验中默认为0Func:功能域,本次试验的任务就是实现rd=$rs func $rt

五、部分代码

建立测试文件,测试文件采用Verilog HDL编写,一个实例如下

module Test;

reg Clock;

reg[31:0] Instr;

parameter ON_delay=80,OFF_delay=80;

wire[31:0] Adat,Bdat,Value;

Rtype Demo(Clock,Instr,Adat,Bdat,Value);

always

begin

Clock=1;

#ON_delay;

Clock=0;

#OFF_delay;

end

initial

begin

Instr=32'h01A88020;

#160 Instr=32'h01C98822;

#160 Instr=32'h01EA9024;

#160 Instr=32'h030B9825;

#160 Instr=32'h032CA02A;

#1000 $dumpflush;

$stop;

end

initial

begin

$dumpfile("count.dump");

$dumpvars(0,Test);

$dumpvars(0,Clock,Instr,Adat,Bdat,Value);

end

Endmodule

寄存器代码:

要求实现3和0与运算;5和6加运算:

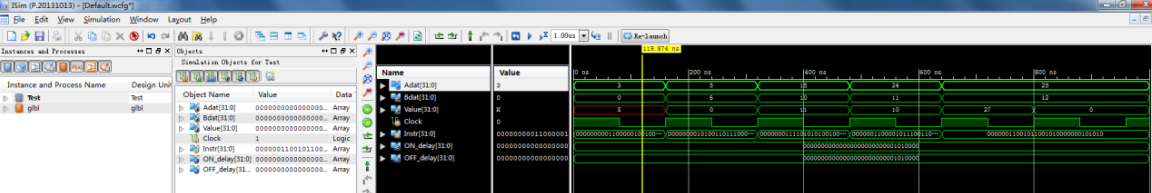

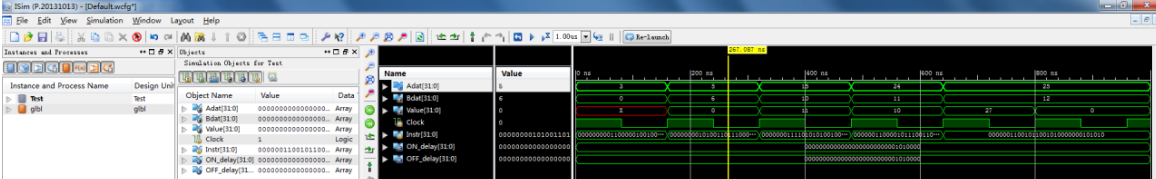

六、实验结果

与运算:

加运算:

要求实现3和0与运算;5和6加运算,因而只需修改前两个运算的机器码,第一个运算机器码的

r

s

改

为

0011

,

rs改为0011,

rs改为0011,rt改为0000并执行与运算;第二个运算机器码的

r

s

改

为

0101

,

rs改为0101,

rs改为0101,rt改为0110并执行加运算即可。

七、六、问题思考

1.该简化版ALU与全功能ALU还有那些区别?

简化版ALU只适用于数值小于16的逻辑运算与算术运算。

全功能ALU可以对处理器控制器、内存及输入输出设备的直接读入读出。

2.为何不将所有指令存放在CPU内部寄存器?

cpu 内部寄存器是直接与运算器、控制器直接相连接的,用作短暂的存储中 间过程的。由其作用就知道,内部存储器是用于运算的,而不是用于存储的,所以其大小远远小于 cache、内存的大小,放不下所有指令。并且,指令不都是顺序执行的,会有跳转。内部寄存器不具备寻址功能,所以不能存放所有的指令。

3.思考如何通过并行性提高指令的运行效率。

1.通过寄存器重命名技术,CPU 解码器把“其它”的寄存器名字变为 “通用”的寄存器名字,本质上是通过一个表格把 x86 寄存器重新映射 到其它寄存器,使实际用到的寄存器变多,提高效率。

2.流水线技术,不同寄存器存放对应的东西,提高并行性从而提高指令的运行效率。

613

613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?