知识零碎:

import ,定义表示这是一个外部变量的标号,不是在本程序定义的

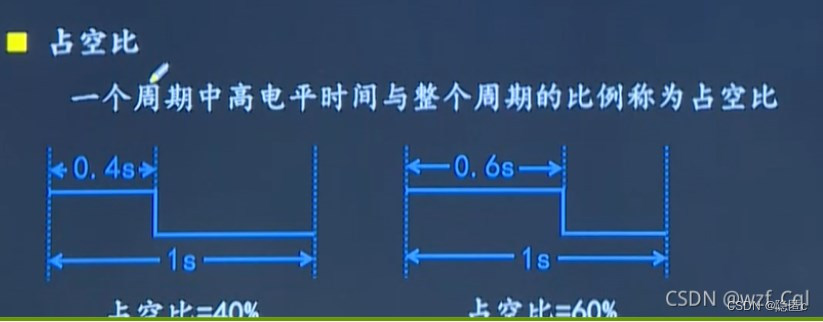

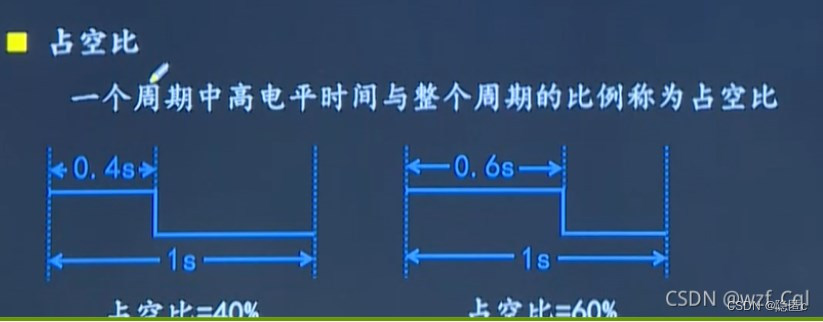

export ,表示本程序里面用到的变量提供给 其他模块 调用的。 占空比: 一个周期中高电平时间与整个周期的比例称为占空比

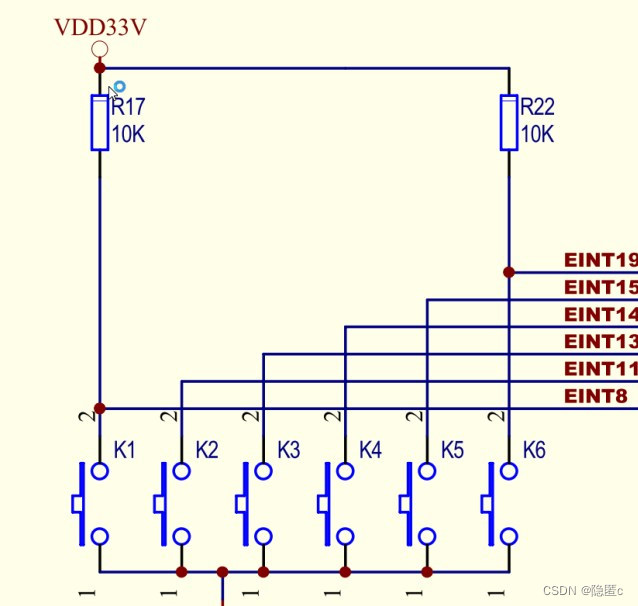

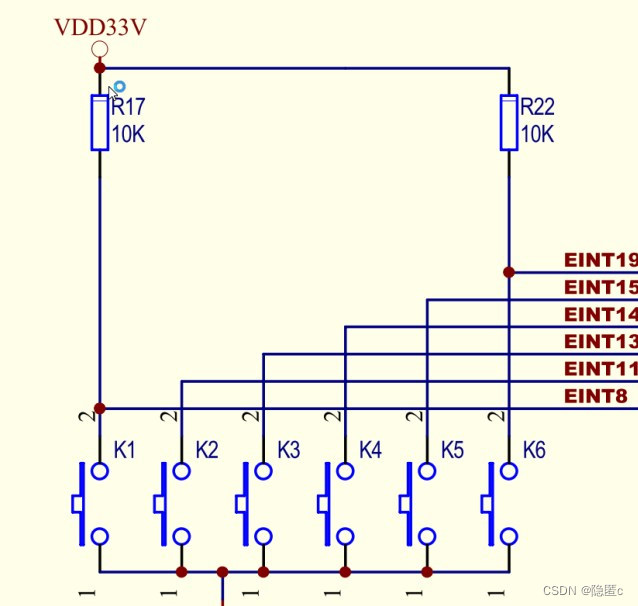

按键模块中,K1和K6所连接的高电阻,根据外部变化变化 连接电源时,为高电平状态 接地时,为低电平状态

S3c2440中断控制器

内部外设: DMA :(直接内存存取) Direct Memory Access UART :全称是通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),是一种双向、串行、异步的通信总线。

IIC:集成电路总线

IIC是 CPU与芯片之间 进行通信使用最多的协议,除去电源之外,需要使用的两根线是:SCLK或者SCL(时钟线)和SDA(数据线)。

- 数据线用来传输数据

- 时钟信号线用于产生时钟频率,控制时序,实现协议过程

S3C2440A

有两个中断挂起寄存器: 源挂起寄存器(

SRC

PND

) PND(悬挂,标记) 中断挂起寄存器(

INT

PND

)

这些挂起寄存器表明一个中断请求是否为挂起

中断控制器特殊寄存器

中断控制器中有 5 个控制寄存器: (SRCPND)

源挂起寄存器 (INTMOD) 中断模式寄存器 (INTMASK) 屏蔽寄存器 (PRIOR) 优先级寄存器 (INTPDN) 中断挂起寄存器

---------------------------------------------------------------------------------------------------------------------------------

时钟模块发生框图

S3C2440A

中的时钟控制逻辑可以产生必须的时钟信号: 包括

CPU

的

FCLK

,

AHB

总线外设的

HCLK

以及 APB 总线外设的

PCLK

。

S3C2440A

包含两个锁相环(

PLL

):一个提供给

FCLK

、

HCLK

和

PCLK

(MPLL)

另一个专用于 USB 模块(

48MHz)

时钟控制逻辑可以不使用

PLL

来减慢时钟,并且可以由软件连接或断开各外设模块的时钟, 以降低功耗。

(UPLL)

(2440)RISC微处理器 (背)

(CPU提供的时钟信号)

Fclk

ARM920T

400MHZ(工作频率)

(AHB总线提供的时钟信号

)

Hclk

AHB(高速外设总线)

100MHZ (摄像头)

(APB总线提供的时钟信号

)

Pclk

APB (低速外设总线)

50MHZ(时钟)

(倍频器)PLL(锁向环)

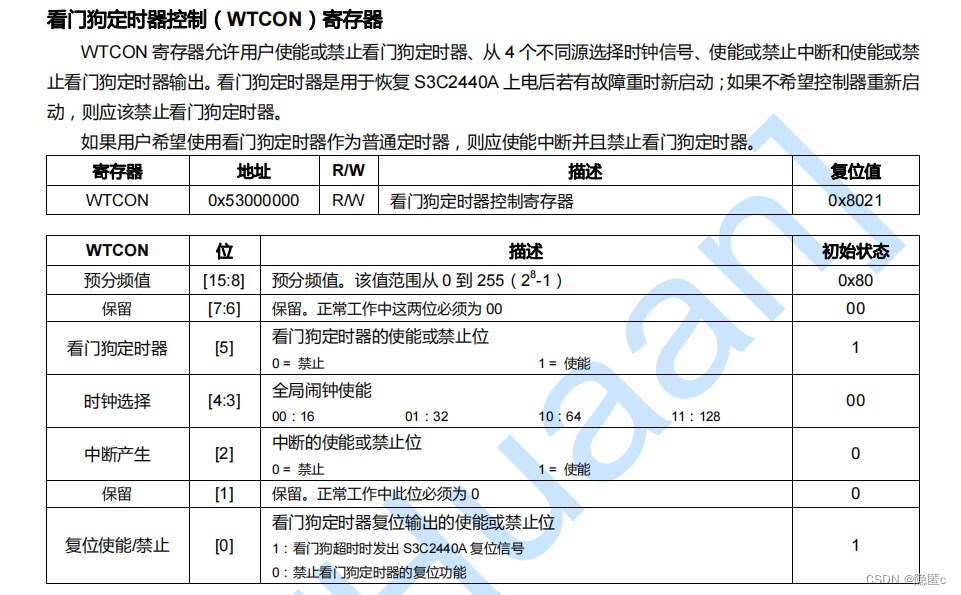

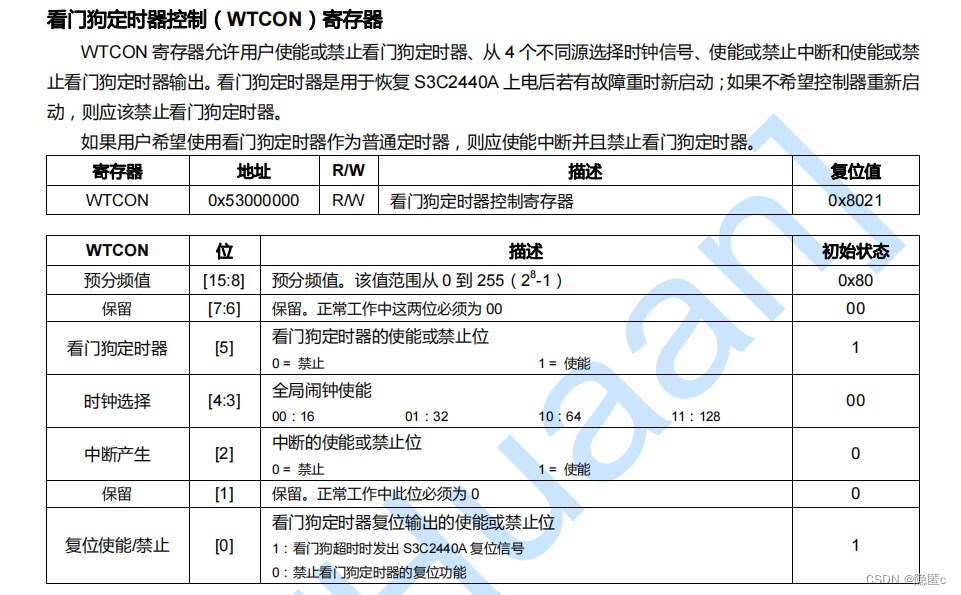

看门狗定

看门狗定时器

S3C2440A

的看门狗定时器是用于当其由于噪声和系统错误引起的故障干扰时恢复控制器的工作。

系统内部的看门狗定时器需要在 指定时间内向一个特殊的寄存器内写入一个数值,俗称

喂狗

。

如果喂狗的时间过了,那么看门狗定时器就会发出一个复位信号导致系统复位。为之后的学习 方便,在这里我们关闭这个看门狗定时器,让它不再咬人

很明显,这个看门狗定时器默认是使能的,我们只需将第

5

为清零即可!

WTCON &= ~(0x01 << 5);

本文详细介绍了S3C2440微处理器的中断控制器、DMA、UART/IIC通信接口,以及时钟模块(包括PLL和看门狗定时器),展示了该处理器的硬件特性及其在系统设计中的作用。

本文详细介绍了S3C2440微处理器的中断控制器、DMA、UART/IIC通信接口,以及时钟模块(包括PLL和看门狗定时器),展示了该处理器的硬件特性及其在系统设计中的作用。

5507

5507

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?