Quartus版本18.0,modelsim版本10.7。

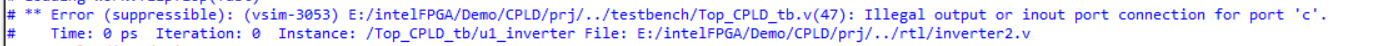

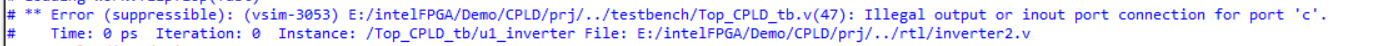

用modelsim进行功能仿真发现了上述错误。看到网上还没有相似的解释。所以开一帖来记录一下。

检查testbench代码之后发现原来是模块内部连线应该定义为wire型,不应该定义为reg型。

修改过后,经过测试功能仿真及时序仿真都可以正常运行。

Quartus版本18.0,modelsim版本10.7。

用modelsim进行功能仿真发现了上述错误。看到网上还没有相似的解释。所以开一帖来记录一下。

检查testbench代码之后发现原来是模块内部连线应该定义为wire型,不应该定义为reg型。

修改过后,经过测试功能仿真及时序仿真都可以正常运行。

8191

8191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?