使用安路TD联合modelsim做时序仿真的时候遇到了问题。modelsim error (suppressible): (vsim-SDF-3250)、(vsim-SDF-3445)

先放上能用的do脚本:

其中tb为仿真文件,top为加了sdc约束的文件。

要点:

sta.v(含时序信息)

phy_sim.v没有的话会导致某些warning(接口消失,我觉得应该没有问题)

vsim:(这个顺序最好不要更换,按上图的顺序比较好)

-novopt 禁止modelsim优化电路

-L 逻辑库的位置

-sdftyp tb/uut 。 tb应该换为顶层的仿真文件名字,uut是实例化模块的名字(而不是被调用的那个模块)

生成sdf

先生成sdf.

然后跑综合布局布线,会自动生成sdf。

如何描述调用sdf的do脚本。这个可以直接用TD软件生成do脚本(为什么要用TD生成,因为自己去百度抄的调用sdf的do脚本语句不好用)

在tools-simulate-post route simulation下直接生成do脚本。

(vsim-SDF-3250)

使用do脚本的时候报错,说找不到instance 的文件。

这个问题是调用库的时候命名错了。

这个问题是调用库的时候命名错了。

-sdftyp tb/uut=sdf文件的地址

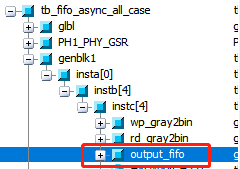

如果top模块是被generate for多次例化的时候,应该怎么约束呢?

如图要约束output_fifo。

-sdftyp tb_fifo_async_all_case/genblk1.insta\[0].instb\[4].instc\[4].output_fifo=$work_address/simulation/generic_async_fifo.sdf

如果没有反斜杠(转义符),0会被当成无效符号。

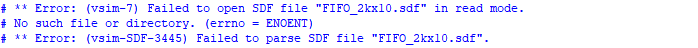

(vsim-SDF-3445)

读取sdf失败,为什么呢?

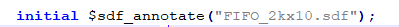

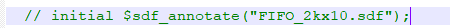

因为TD生成的sim_sta.v文件里指定了sdf文件的名字(默认为工程的名字)。

而我要约束的模块为generic_async_fifo实例化生成的output_fifo,所以我把FIFO_2kx10.sdf重命名为了generic_async_fifo.sdf。

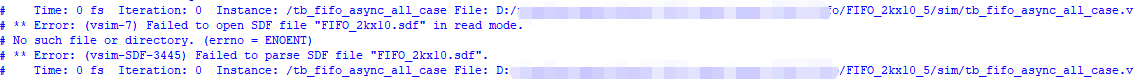

这导致do脚本执行的过程中找不到FIFO_2kx10.sdf(do脚本里写的是文件generic_async_fifo.sdf)(但是sta.v要调用的是FIFO_2kx10.sdf)。

并且!sta.v默认sdf和他在同一个文件夹下。

我推测是因为do脚本/tb的位置和sta.v的位置不一样,导致sta.v和sdf在一个文件夹下,还是报错:(尽管do里已经绝对路径指定了sdf的位置)

注释掉sta.v的sdf_annotate就能通过了!

1975

1975

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?