文章目录

本文根据博主设计的Prompt由CHATGPT生成,形成极简外设概念。

🚀 概念揭秘

SPI,全称为Serial Peripheral Interface,是一种串行设备间通信总线,最早由摩托罗拉公司开发。SPI是一种高速、全双工、同步的通信总线,主要用于微控制器和其各种外设之间的通信。

SPI有四种工作模式,分别是:模式0、模式1、模式2和模式3。这四种模式根据SCLK(时钟信号)的极性和相位的不同进行划分。

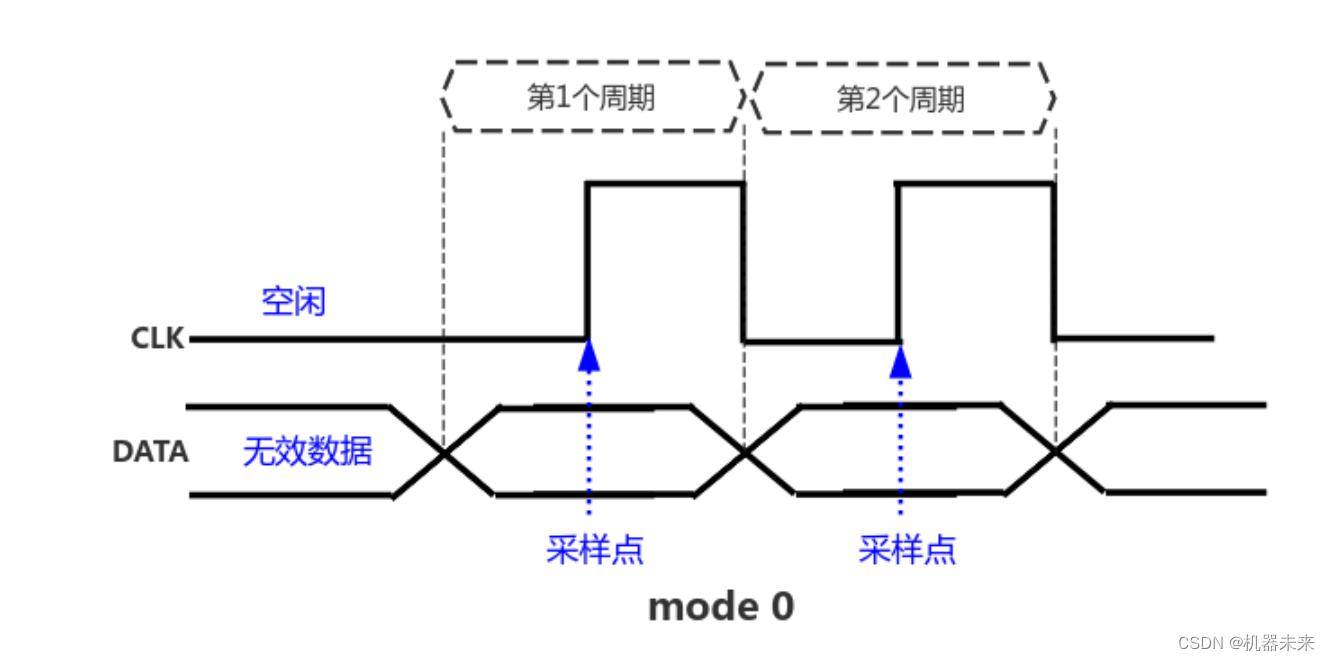

模式0: SPI模式0(CPOL = 0, CPHA = 0)

时钟极性(CPOL)为0:时钟信号在空闲状态时保持低电平。

时钟相位(CPHA)为0:数据采样发生在时钟信号的第一个边缘,即从低电平跳变到高电平的上升沿,而数据在时钟信号的下降沿变化;

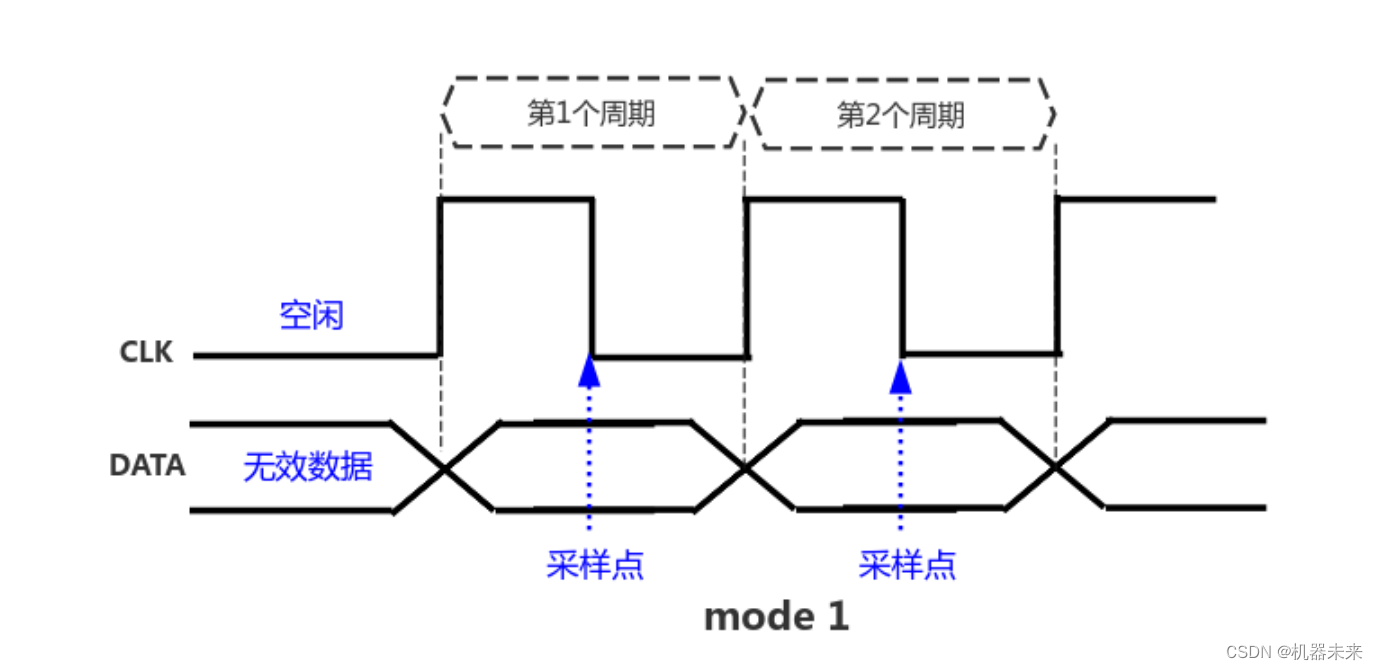

模式1: SPI模式1(CPOL = 0, CPHA = 1)

时钟极性(CPOL)为0:时钟信号在空闲状态时保持低电平。

时钟相位(CPHA)为1:数据采样发生在时钟信号的第二个边缘,即从高电平跳变到低电平的下降沿,而数据在时钟信号的上升沿变化。

在模式1中,数据通信开始于第一个下降沿,并在每个下降沿进行采样。

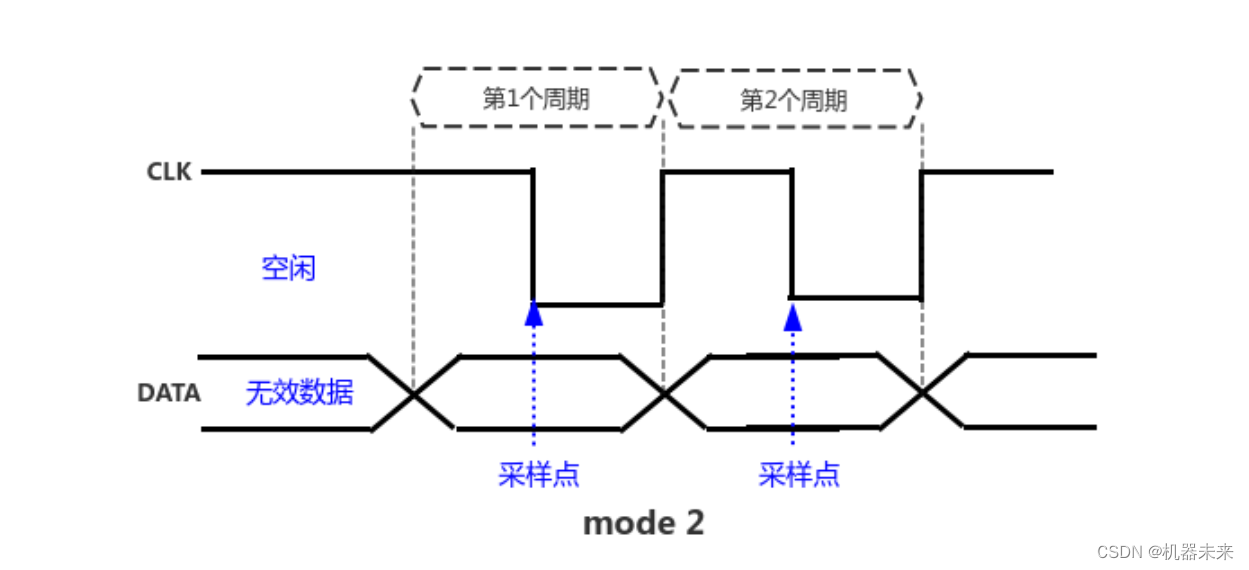

模式2: SPI模式2(CPOL = 1, CPHA = 0)

时钟极性(CPOL)为1:时钟信号在空闲状态时保持高电平。

时钟相位(CPHA)为0:数据采样发生在时钟信号的第一个边缘,即从高电平跳变到低电平的下降沿,而数据在时钟信号的上升沿变化。

在模式2中,数据通信开始于时钟的第一个下降沿,并在随后的每个下降沿进行采样。

模式3: SPI模式3(CPOL = 1, CPHA = 1)

时钟极性(CPOL)为1:时钟信号在空闲状态时保持高电平。

时钟相位(CPHA)为1:数据采样发生在时钟信号的第二个边缘,即从低电平跳变到高电平的上升沿,而数据在时钟信号的下降沿变化。

在模式3中,数据通信开始于第一个上升沿,并在每个上升沿进行采样。

本文详细介绍了SPI(SerialPeripheralInterface)的原理、工作流程、生活类比以及实战案例,包括模式选择、全双工通信、同步特性、微控制器与传感器通信的应用。同时讨论了SPI的优势和面临的挑战,如速度、距离限制和错误检测问题。

本文详细介绍了SPI(SerialPeripheralInterface)的原理、工作流程、生活类比以及实战案例,包括模式选择、全双工通信、同步特性、微控制器与传感器通信的应用。同时讨论了SPI的优势和面临的挑战,如速度、距离限制和错误检测问题。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3827

3827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?