[uOps]

Metric Description

uOp, or micro-op, is a low-level hardware operation. The CPU Front-End is responsible for fetching the program code represented in architectural instructions and decoding them into one or more uOps.

uOps

micro-ops,micro-operations,微指令,是一种底层硬件操作,CPU前端负责获取体系结构指令中表示的程序代码,并将其解码为一个或多个uops。

Pipeline Slots

Metric Description

A pipeline slot represents hardware resources needed to process one uOp.

The Top-Down Characterization assumes that for each CPU core, on each clock cycle, there are several pipeline slots available. This number is called Pipeline Width.

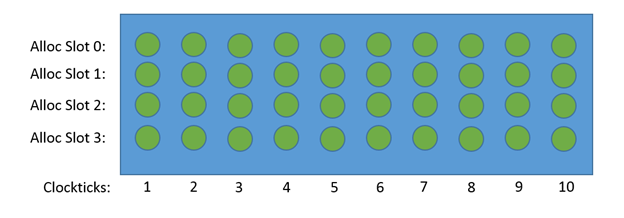

In the example below, there is a 4-wide CPU that executes code for 10 clock cycles:

In this example, there are 40 Pipeline Slots (4 * 10). If a Pipeline Slot does not retire, a uOp is attributed to a Stall.

In the next example, 20 out of 40 slots are stalled (did not retire a uOp). This means that the code efficiency from the microarchitecture perspective is only 50%:

The Top-Down metrics measured in Pipeline Slots, for example, Front-End Bound and Back-End Bound, measure a percentage of Pipeline Slots stalled due to the reason specified by the metrics such as Front-End issues and Back-End issues.

Pipeline Slots

一个pipeline slot 表示处理一个uOp需要的硬件资源。

Top-Down分析方法假定对于每个CPU核,在每个时钟周期,有多个可用的pipeline slots。这些Pipeline Slots的数量被称为Pipeline Width。

在下文的示例中,是用4-wide的CPU将代码执行10个时钟周期。

在该示例中,包含40个Pipeline Slots(4 * 10)。如果一个Pipeline Slot没有retire,则表示认为有一个uOp产生阻塞(Stall)。

在下个示例中,有20个slots产生阻塞(没有使一个uOp达到Retire)。这表示从该微架构的角度来看,代码的执行效率只有50%:

以Pipeline Slots测得的Top-Down度量,如Front-End Bound和Back-End Bound,表示因各种原因(如Front-End问题和Back-End问题)导致的Pipeline Slots 阻塞的百分比。

参考原文:

https://software.intel.com/en-us/vtune-help-uops

https://software.intel.com/en-us/vtune-help-pipeline-slots

2000

2000

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?