目录

1.uvm_driver内有两个参数,但一般只需要声明REQ即可

1.sequence不能自启动,必须通过相关联的sqr启动并自动执行其中的body方法,在某一环境中sqr管理多个sequence,仲裁某一个时刻传递哪个sequence的数据。

2.sqr从uvm_sequencer派生,定义时要指定传递的transaction类型;

1.monitor 将信号转化为transaction级的数据包,可以在其中进行function coverage的收集,通过TLM-port机制与其他组件相连。

1.建议所以phase都使用super.phase去调用父类的phase方法,虽然目前除了build_phase大部分都没有区别,但是不保证之后的uvm版本中不会更新,建议养成代码规范;

1.uvm_driver

class uvm_driver #(

type REQ = uvm_sequenve_item,

type RSP = REQ

) extends uvm_component1.uvm_driver内有两个参数,但一般只需要声明REQ即可

2.主要方法

get_next_item

try_next_item

通过以上两个方法之一,实现driver向sqr的请求。driver为initiator,sqr为target。

get为阻塞方法,try为非阻塞。

当driver内除了获取数据还需要进行其他处理,例如未获取数据时将接口初始化,则必须使用try

item_done

3.代码示例

`ifndef _GUARD_HELLO_DRIVER_SV_

`define _GUARD_HELLO_DRIVER_SV_ //两句连用,防止重复编译(C语言内容)

class hello_driver extends uvm_driver #(hello_transaction)

virtual hello_if vif;

`uvm_component_utils(hello_driver) //uvm 工厂机制 宏注册

extern function new(string name,uvm_component parent);

extern virtual function void build_phase(uvm_phase phase);

extern virtual task main_phase(uvm_phase phase);

//new、build_phase、main_phase是一个component必须的

extern task xxx

//不同的component里面有各自完成独特功能的函数,属于用户自定义

endclass

function hello_driver::new(string name,uvm_component parent)

super.new(name,parent);

endfunction

//执行uvm_driver的new函数

function hello_driver::build_phase(uvm_phase phase)

super.build_phase(phase);

if(!uvm_config_db#(virtual hello_if)::get(this,"","vif",vif))begin

`uvm_fatal(get_full_name(),"Error in Geting interface");

end

endfunction

//interface只在top中实例化.软件域中均使用vif

task hello_driver::main_phase(uvm_phase phase);

hello_transaction req;

super.main_phase(phase);

vif.data <= 0;

vif.valid<= 1'b0;

//初始化

while(!vif.rst_n)

@(posedge vif.clk)

while(1) begin

seq_item_port.get_next_item(req); //通过driver与sqr之间的port,获取一个req

drive_one_pkt(req); //用户自定义函数,通常用来处理transaction并驱动DUT

seq_tiem_port.item_done(); //通知sqr该transaction已经处理完毕

end

endtask

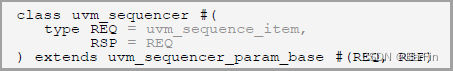

2.uvm_sequencer

1.sequence不能自启动,必须通过相关联的sqr启动并自动执行其中的body方法,在某一环境中sqr管理多个sequence,仲裁某一个时刻传递哪个sequence的数据。

2.sqr从uvm_sequencer派生,定义时要指定传递的transaction类型;

3.代码示例

`ifndef _GUARD_HELLO_DRIVER_SV_

`define _GUARD_HELLO_DRIVER_SV_ //两句连用,防止重复编译(C语言内容)

class hello_sequencer extends uvm_sequencer #(hello_transaction)

`uvm_component_utils(hello_driver) //uvm 工厂机制 宏注册

extern function new(string name,uvm_component parent);

extern function void build_phase(uvm_phase phase);

//new、build_phase、main_phase是一个component必须的

endclass

function hello_sequencer::new(string name,uvm_component parent)

super.new(name,parent);

endfunction

//执行uvm_sequencer的new函数

function void hello_sequencer::build_phase(uvm_phase phase)

super.build_phase(phase);

endfunction3.uvm_monitor

![]() \

\

1.monitor 将信号转化为transaction级的数据包,可以在其中进行function coverage的收集,通过TLM-port机制与其他组件相连。

2.代码分析

`ifndef _GUARD_HELLO_MONITOR_SV_

`define _GUARD_HELLO_MONITOR_SV_ //两句连用,防止重复编译(C语言内容)

class hello_driver extends uvm_monitor #(hello_transaction)

virtual hello_if vif;

uvm_analysis_port #(hello_transaction) ap;

`uvm_component_utils(hello_monitor) //uvm 工厂机制 宏注册

extern function new(string name,uvm_component parent);

extern virtual function void build_phase(uvm_phase phase);

extern virtual task main_phase(uvm_phase phase);

//new、build_phase、main_phase是一个component必须的

extern task xxx

//不同的component里面有各自完成独特功能的函数,属于用户自定义

endclass

function hello_monitor::new(string name,uvm_component parent)

super.new(name,parent);

endfunction

//执行uvm_driver的new函数

function void hello_driver::build_phase(uvm_phase phase)

super.build_phase(phase);

if(!uvm_config_db#(virtual hello_if)::get(this,"","vif",vif))begin

`uvm_fatal(get_full_name(),"Error in Geting interface");

end

ap = new("ap",this);

endfunction

//interface只在top中实例化.软件域中均使用vif

task hello_monitiro::main_phase(uvm_phase phase);

logic valid;

logic [7:0] data;

hello_transaction tr;

super.main_phase(phase);

while(1) begin

tr = new();

receive_one_pkt(tr);

ap.write(tr);

end

endtask

680

680

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?