FPPGA基于Avalon协议的SDRAM读写控制

概述

通过串口模块发送数据,并将数据写入SDRAM中,然后通过按键读取SDRAM中的数据。对于SDRAM复杂的控制逻辑操作,可以交给IP核实现,这里只需要简单设置接口传入的数据,就能实现对SDRAM的读写控制。

SDRAM简介

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(asynchronous DRAM)相比,可以有一个更复杂的操作模式。

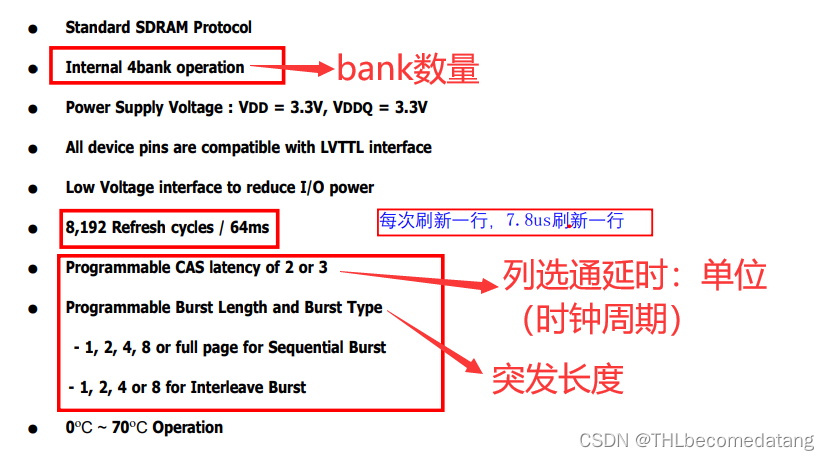

这里采用的256M (16Mx16bit) Hynix SDRAM Memory。

SDRAM容量的计算

容量的计算: 对SDRAM的读写是针对储存单元进行的,一个存储单元的容量等于数据线总线的位宽,单位是bit;

SDRAM总的存储容量:L_Bank的数量x行数x列数x存储单元容量(数据线的位宽)

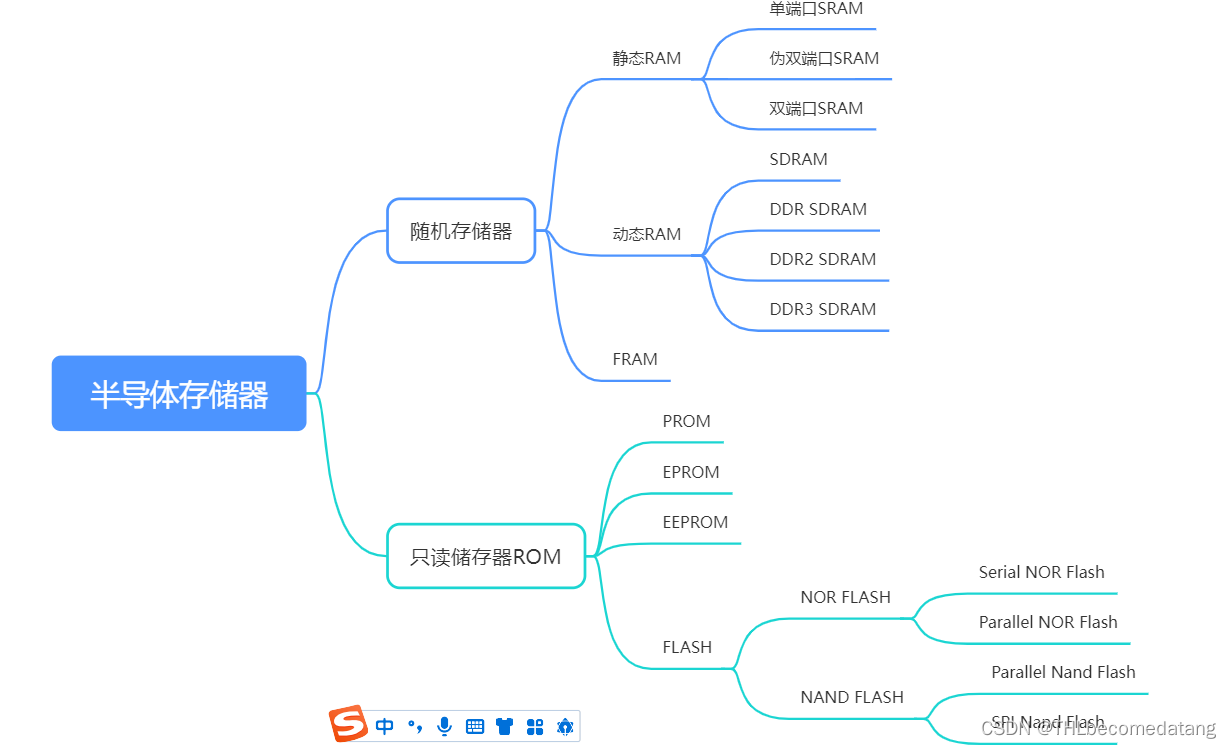

存储器的一些分类

结构特性

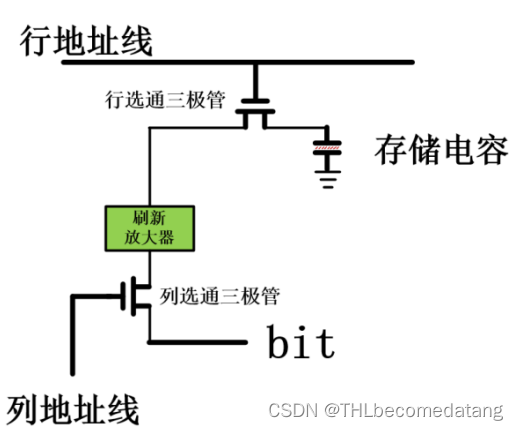

SDRAM 的基本存储单位是存储单元,而一个存储单元的容量为若干个 Bit,对于SDRAM 而言就是芯片的位宽,每个 Bit 存放于一个单独的存储体中,存储体是利用电容能够保持电荷以及可充放电的特性制成,主要由行选通三极管、列选通三极管、存储电容以及刷新放大器构成。电容所存储的电荷会随时间慢慢释放,这就需要不断刷新为电容充电,以保证存储数据可靠性。其存储体示意图如下所示:

器件特性如下:

寻址方式

- SDRAM的地址分为列地址(column address)和行地址(row address)。

- 分时复用技术,可以减少芯片的引脚。用SDRAM的RAS(RowAddressStrobe,行地址信号)和CAS(ColumnAddressStrobe,列地址信号)加以区分,在RAS引脚使能时地址线传输的是行地址,在CAS引脚使能时地址线传输的是列地址。

引脚说明

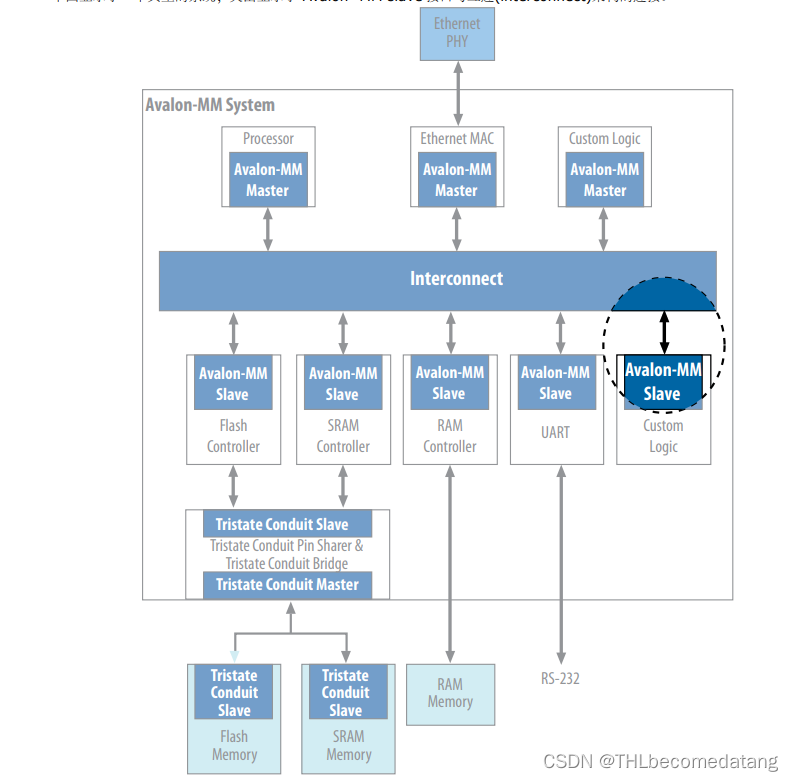

Avalon接口协议简介

Avalon® 接口使您能够轻松连接 Intel® FPGA 中的各个组件,从而简化了系统设计。 Avalon 接口系列对应用于流式传输高速数据,读写寄存器和存储器以及控制片外器件的接口进行了定义。Platform Designer 中的组件采用这些标准接口。此外,您可以在自定义组件中使用 Avalon 接口,以增强设计的互操作性。

常用的接口类型

- Avalon Streaming Interface ( Avalon -ST)—支持单向数据流的接口,包括多路复用流,数据包和 DSP 数据。

- Avalon Memory Mapped Interface ( Avalon -MM)—一种基于地址的读/写接口,是主–从连接的典型接口。

- Avalon Conduit Interface—一种接口类型,适用于那些不适合任何其他 Avalon 类型的单个信号或信号组。您可以在一个 Platform Designer 系统内部连接管道接口(conduitinterface)。或者,您可以将它们导出以连接到设计中的其他模块或者连接到 FPGA 管脚。

- Avalon Tri-State Conduit Interface ( Avalon -TC) —支持与片外(off-chip)连接的接口。多个外设可以通过信号多路复用(signal multiplexing)来共享管脚,从而减少 FPGA 的管脚数和 PCB 上的走线数量。

- Avalon Interrupt Interface—允许组件向其他组件发送事件信号的接口。

- Avalon Clock Interface—驱动或接收时钟的接口。

- Avalon Reset Interface—提供复位连接的接口。

在本次设计中采用的是第二种,Avalon -MM內型的接口,一种基于地址读写的主从內型的接口,用户根据自己的需求选择其他类型的接口。

Avalon读写的控制(Avalon -MM)

Avalon -MM 接口,通过 slave 控制的 waitrequest 来支持读写传输。通过置位 waitrequest 信号,slave 能够将互连暂停所需的周期。如果一个 slave 将waitrequest 用于读传输或者写传输,那么该 slave 必须对两者都使用 waitrequest。

典型的数据读写

这里用的是这种內型的,其他內型的这里就不在介绍,如果想要了解更多的,可以点击:Avalon接口官方手册进行查看。

嵌入式IP核

由于在Quartus中没有内置的SDRAM的ip核,所以这里我们需要自己配置IP核,具体如何配置,我会在下一期讲,这里大家可以看intel 嵌入式ip核官方文档

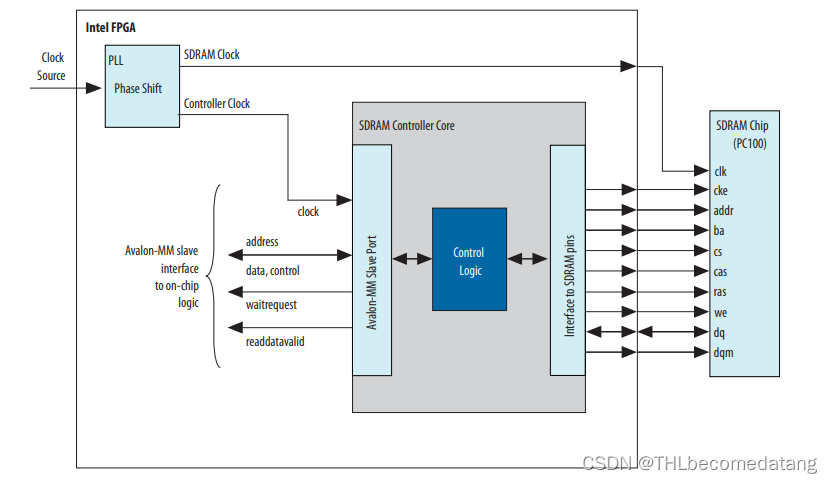

这里我整理一些重要的结构图如下所示:

模块整体设计

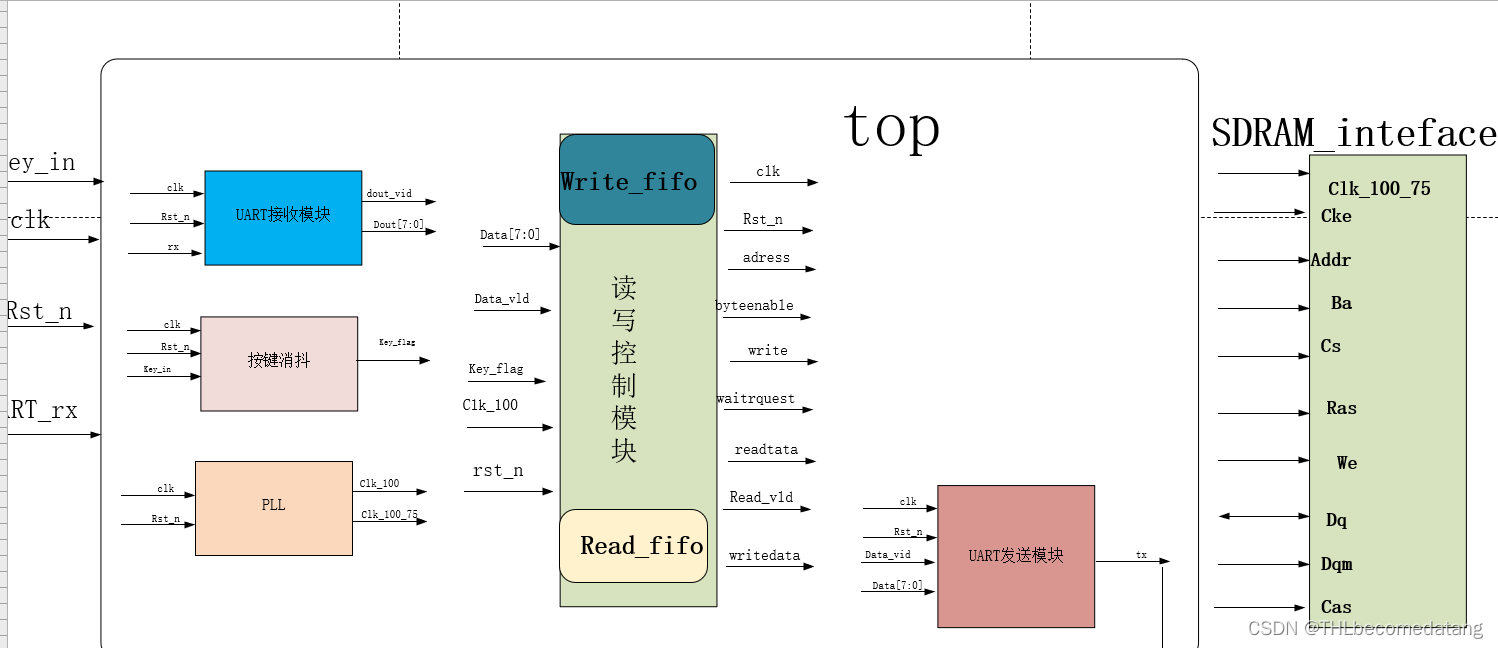

根据上面的接口以及嵌入式ip的控制,就可以进行设计了,下面是我画的简单的模块框图:

- 串口模块接收来自上位机的数据

- PLL实现是时钟的偏移和倍频,产生控制模块驱动时钟100Mhz以及SDRAM接口的驱动时钟100Mhz(偏移75);

- 按键模块接收读数据请求信号

- 读写控制模块是重点,这里讲按键信号和上位机的数据进行控制,来控制读写。输出SDRAM所需要的接口信号;

- Write_fifo接收串口发过来的数据,这里采用的是异步fifo,写的时钟周期为系统时钟50Mhz,读Write_fifo的数据为100Mhz的时钟周期,因为串口发过来的数据是8位宽的,而SDRAM的数据地址是16位的,时钟周期也不一样,所以需要用到异步fifo

- Read_fifo同理,接收来自SDRAM的数据,然后将数据发给串口,16位->8位。

- 串口发送模块 接收来自Read_fifo的数据,并通过RS232协议发给上位机。

- 对于输入接口的与读写控制的时钟不一样,根据手册要求,他两有相位偏移,具体是多大,可以自己试试合适的值,我这里采用的75%,效果还可以

结果分析

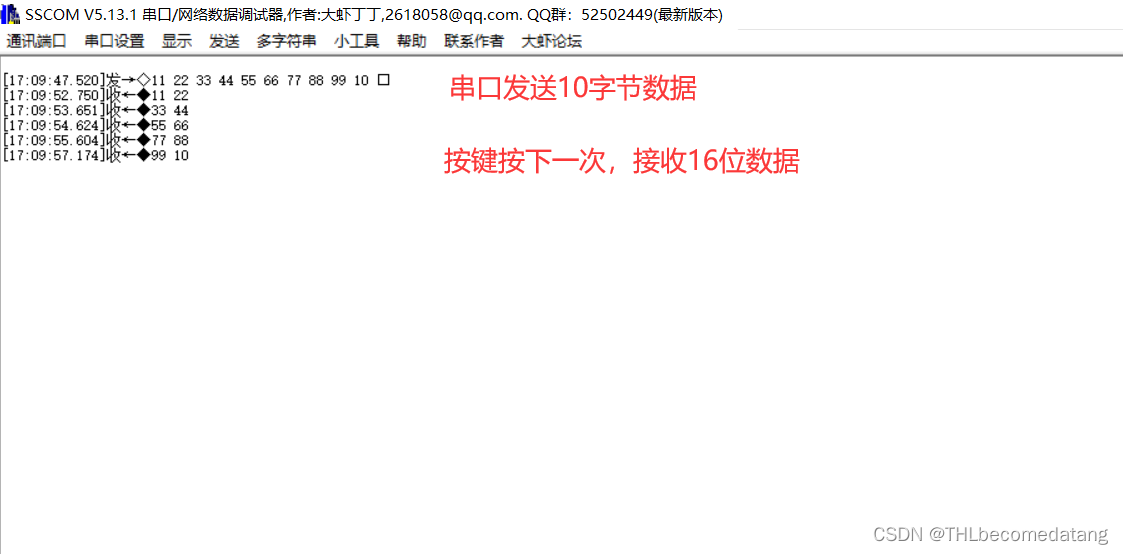

版级验证,按键按一下,从SDRAM读取一个地址的数据(16位),然后通过串口发送模块将其发送到上位机,实验成功。

总结

在本次实验中,只讲了大致的方法和原理,如果大家需要的话,我在下期把代码进行讲解。

通过本次的实验,采用调用IP来对SDRAM进行读写控制,省去了许多的麻烦,对于那些SDRAM的指令和状态跳转,时序,不需要我们特别关心,只需要控制Avalon的接口,就可以简单的实现,唯一的难点就是手册的阅读,对于读写控制模块的逻辑稍微有点复杂,但仔细思考,发现其实也不是很难。通过本次实验可以掌握PLL锁向环的调用,FIFO,以及配置嵌入式IP。在控制模块中要注意跨时钟域的处理(同步打拍和异步FIFO)。

2414

2414

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?