大纲

1.PCIE的链路训练和电源管理、流量控制和MSI中断机制

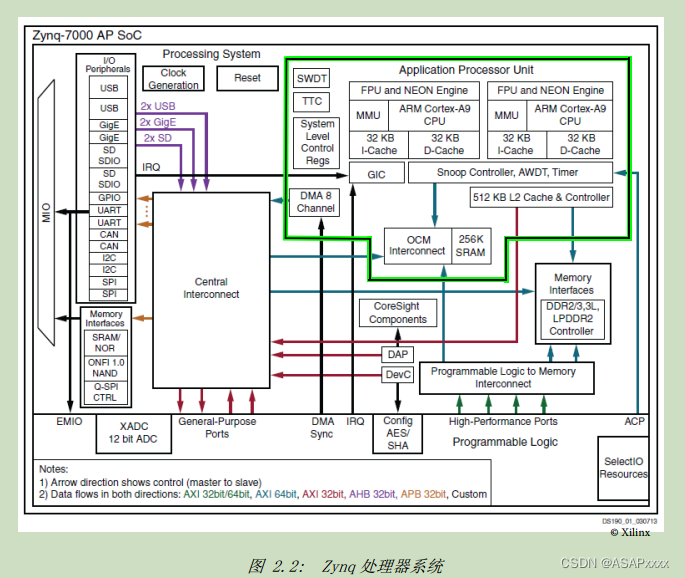

2.Zynq的基本框架

要点简介

1.PCIE的链路训练

LTSSM状态机,由11个状态组成

2.流量控制

主要有两种方法,分为“Rated-base”和“Credit-base”,分别适用于可预知带宽和突发带宽的情况

3.MSI中断机制

在Power PC和x86上有明显区别的,这种中断机制是通过写存储器来中断,中断信号为上升沿触发,在PwerPC中要记住MSIIR,在x86中中断信息和中断向量同时到达,比PowerPC的时间效率更高。

4.PowerPC的MSI中断运行机制

PCIE设备的报文其目的地址为中断控制器的MSIIR寄存器,当这个寄存器被PCie写入后,中断控制器向处理器提交中断请求,处理器再读取中断控制器中的ACK寄存器获得中断向量号,进行相应的处理(延时会较大)

5.ps与pl的互联

通过axi,zynq中有三种axi(hp gp acp),hp是高速接口,连接存储器互联;gp是通用接口,连接到主机或者从机互联;acp是缓存一致性接口,连接到一致性控制单元SCU。存储器互联、主机、从机互联最终都会连接到中心互联。

6.一致性控制单元

连接了两个处理器核的一级缓存、片上存储器以及共享二级缓存

7.SRAM与DRAM的区别

DRAM是动态RAM,它是由电容来存储的,电容会漏电,所以要不断刷新才行,速度慢;SRAM不用动态刷新,速度快,但是它的成本高,一般是小规模的。

8.EMIO

可以直接连接到PL的外部引脚,也可以连接到PL端的IP核

9.可编程逻辑

其中可配置逻辑块CLB的左右两边都是开关矩阵,里面有两个Slice,上下连接进位逻辑链,每个slice里面有若干个LUT和FF

![![[Pasted image 20230203194158.png]]](https://img-blog.csdnimg.cn/cbf5d36cf0484b22b2eb518cbad44a8c.png)

10.块RAM

大小可变化,它可以存放DSP运行中的数据,这些数据也可以用分布式RAM来存储,分布式RAM是由CLB中的RAM构成的,它的优点是灵活、距离近,缺点是耗费资源大,适合小容量的存储。

11.Zynq处理器系统全局架构

参考文献

1.PCI EXPRESS 体系结构导读

2.The_Zynq_Book_ebook_chinese

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?