概述

Initial lane synchronization(初始通道同步)的目的就是实现204B系统中一组link之间的lane与lane之间的同步和对齐。

初始通道同步

在真正传输用户有效负载数据之前,需要完成初始通道同步过程。初始通道同步程序遵循其他标准的原则,例如 XAUI 标准,参考204B标准协议中的文献 6,第 48.2 条。

如下图所示,在明确定义的时间点,所有transmitters都会发出专用Lane对齐字符 /A/= /K28.3/。由于不同Lane的延迟也会不同,receivers可能会在不同的时间接收这些对齐字符。接收 /A/ 后,每个receivers将后续数据存储在缓冲区存储器中,并向其他接收器指示一个标志(“ready”),指示缓冲区包含有效的对齐起点。当所有接收器都发出其“对齐接收”标志时,它们开始“在同一时间点”将接收到的数据传播到后续数据处理逻辑,其中,“在同一时间点”基于公共信号(定义为‘start’)。

对于支持确定性延迟(deterministic latency)的JESD204B设备,此‘start’信号在 6.1 中定义,即通过LMFC获得start。如果其他receivers在自己的缓冲区中找不到对齐字符,而发出错误信号指示时,该规范同样允许在指定时间内接收到对齐字符的receiver完成同步过程(例如,FPGA作为RX时,实例化了4个RX serdes,但实际只使用了2个lane的serdes)。

Initial lane synchronization是通过初始通道对齐序列(ILA)实现的,在代码组同步后(Code Group Sync)立即开始。ILA序列不进行加扰(Scramble)。

(1)ADC发送的ILA对齐序列由4个多帧(multiframe)组成。

(2)子类 1 和 2 模式下的DAC ILA也由 4 个多帧组成。

(3)具有多个子类 0 模式下的DAC 器件的配置可能需要额外的multiframes才能实现通道对齐。因此,在逻辑器件中,ILA的长度应可编程为4到至少256个多帧。

(4)多帧定(multiframe)义为一组 K 个连续的frames帧,其中 K 介于 1 和 32 之间,使得每个多帧的八位字节数介于 17 和 1024 之间:

ceil(17/F) ≤ K ≤ min(32, floor(1024/F))

在JESD204发射(TX)设备中,K 的值应该是可编程的。在JESD204接收(RX)设备中,建议 K 的值是可编程的。JESD204接收(RX)设备应明确说明其对发射设备中系数 K 设置的要求或建议。

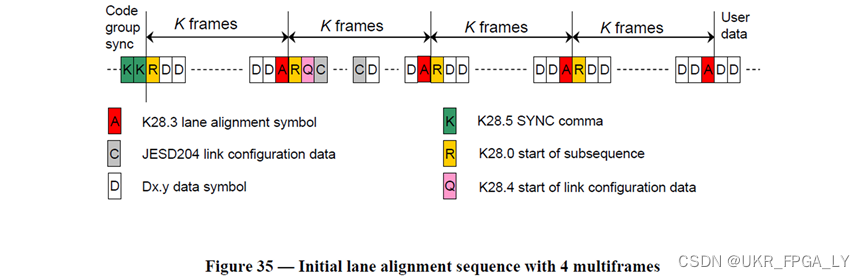

ILA序列的结构如图 35 所示。每个multiframe都以 /R/= /K28.0/ 开头,以 /A/ 结尾。/R/ 向receiver指示multiframe是ILA序列的一部分。/A/ 标记多帧的结束,用于lane和frame同步。第二个multiframe应包含有关从transmitter到receiver的JESD204链路的配置信息,从第三个符号开始。第二个符号中的固定传输代码 /K28.4/ 是对接收方配置数据将要启动的额外确认。ILA序列的内容在 8.2 和 8.3 中进一步指定。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?