不管是什么语言,如果大家都用同一套的代码风格,那么交流起来就非常方便。除此之外,好的代码风格,还能让你的工作变得轻松一些。(使用sublime的代码补全功能,就无需担心这些复杂的变量名)。

如果你只使用Verilog,那么建议用匈牙利命名法。如果是Verilog和VHDL混用,则建议用传统命名法。因为VHDL不区分大小写,用传统命名法,有利于移植代码。

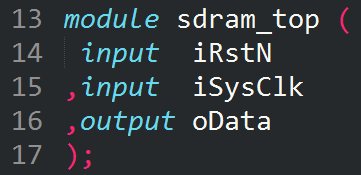

1、模块名跟文件名相同,都用小写,顶层文件要加上_top后缀。而testbench文件则加上_tb后缀。

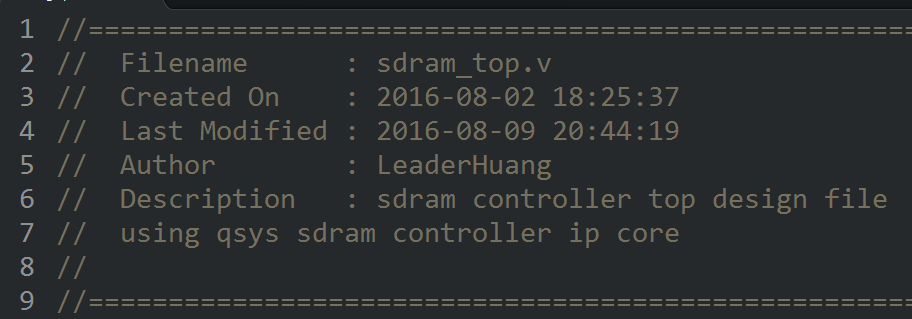

2、每个文件的开头,都要加注释头,并说明该文件的作用。

3、模块内部,除了第一行,其它行都以逗号开头并对齐端口名,调试时可以避免注释某端口时带来不必要的麻烦。

1比特的输入端口以i开头,1比特的输出端口以o开头,1比特的双向端口以io开头。

多比特的输入端口以iv开头,多比特的输出端口以ov开头,多比特的双向端口以iov开头。要跟邻近的端口名对齐。(v是vector的意思)

4、1比特的reg型变量以r开头,1比特wire变量以w开头。

多比特的reg型变量以rv开头,多比特的wire型变量以rw开头。要跟邻近的变量名对齐。

reg变量都要赋初值'b0,包括端口名(如 output reg oData='b0)。

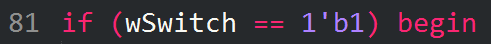

5、if、while语句中必须指明条件中的值,不允许写成if(wSwitch)begin。

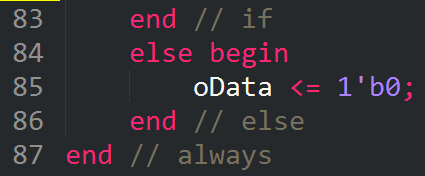

6、所有的end后面都要加上注释,以标明是哪个关键词的结束。

endcase和endmodule可以不加。

7、如果是低电平有效,就在变量名后面加上大写N。

8、所有的begin和左括号(,都要跟对应的关键词一行。(在同样的面积下,能阅读更多的代码)。

9、就算只有一行代码,都必须加上begin end。

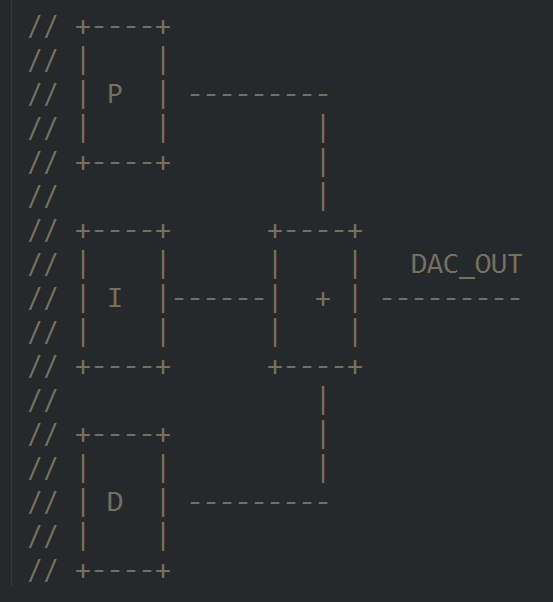

10、如果用到元件例化,要用AsciiArtStudio,画好连接图,转成Ascii码,放在对应的地方。

如果有状态机,也要画状态转换图。

11、使用parameter或localparameter替代`define来定义常量,常量名全部都要大写。

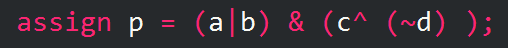

12、不依赖Verilog默认的优先级,每个运算都加括号。

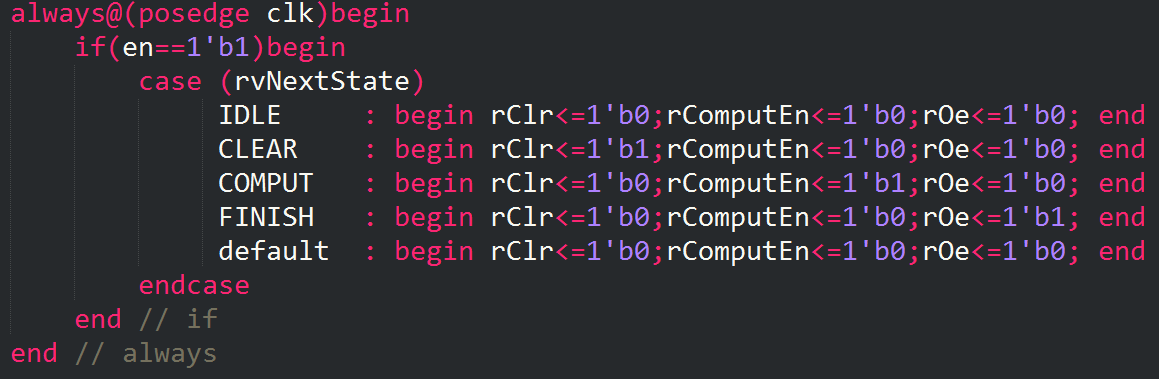

13、case语句下的分支要排列整齐。

14、always不要过于复杂,一个输出就写一个always,除非是关联性很大的几个输出,可以写在一起。

15、不使用隐式元件例化,在端口映射中,不加其它逻辑,如:AND、OR等。元件例化只完成接线的功能,加了其它逻辑,会影响分析代码。

16、做好缩进。

17、命名不使用拼音,要简单易懂。

232

232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?