-

概述

本文档以ZYNQ7000平台为例,详细介绍如何去修改ZYNQ的时钟频率。

-

时钟频率修改流程

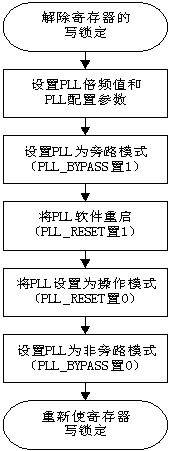

ZYNQ7000的时钟频率修改流程,如图 2.1所示。具体步骤如下:

步骤一:解除ZYNQ7000的寄存器写锁定;

步骤二:向对应寄存器写入我们需要设置的PLL倍频值和PLL配置参数;

步骤三:进行PLL的旁路模式转换和软件重启,使我们刚刚设置的PLL倍频值和PLL配置参数生效;

步骤四:重新使寄存器处于写锁定状态。

图 2.1 ZYNQ7000的时钟频率修改流程图

ZYNQ7000的ARM_PLL_CLK时钟频率修改的具体的代码实现如程序清单 2.1所示。不同平台的解除和锁定写锁定的方式可能不同,对于ZYNQ7000平台,需要写入0xDF0D到SLCR_UNLOCK寄存器解除写锁定,写入0x767B到SLCR_LOCK寄存器可以使相关寄存器的写操作无效。

SylixOS 基于ZYNQ的时钟频率修改详解

最新推荐文章于 2024-06-27 10:14:46 发布

本文档详细介绍了如何修改ZYNQ7000平台的时钟频率,包括解除寄存器写锁定、设置PLL倍频值和配置参数、进行PLL模式转换及软件重启等步骤,并提供了具体的代码实现。

本文档详细介绍了如何修改ZYNQ7000平台的时钟频率,包括解除寄存器写锁定、设置PLL倍频值和配置参数、进行PLL模式转换及软件重启等步骤,并提供了具体的代码实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5744

5744

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?