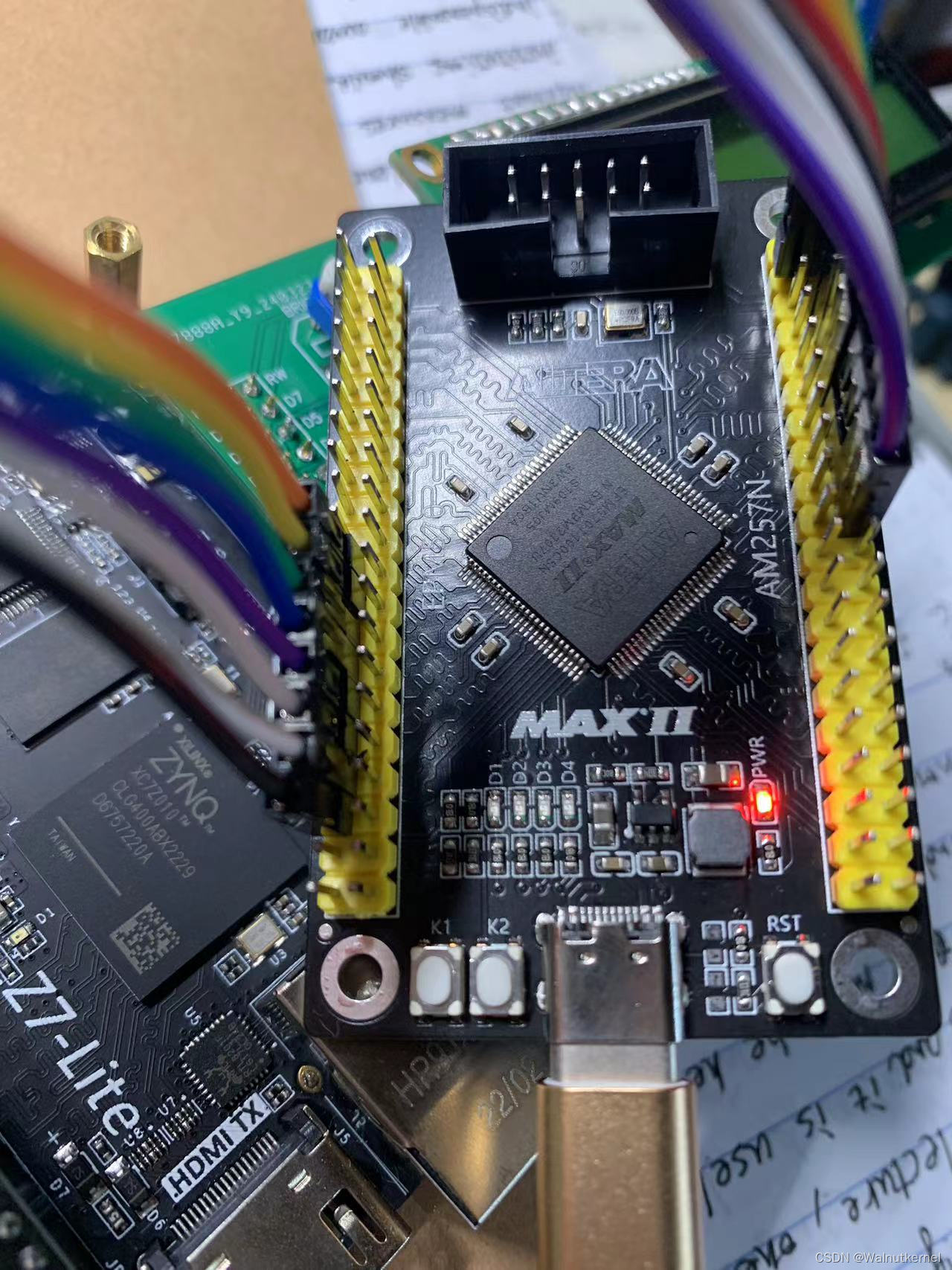

新买了一块CPLD板子,型号是EPM570T100C5N,第一次玩CPLD记录一下,顺便也可以为其他第一次用CPLD的朋友们指指路。

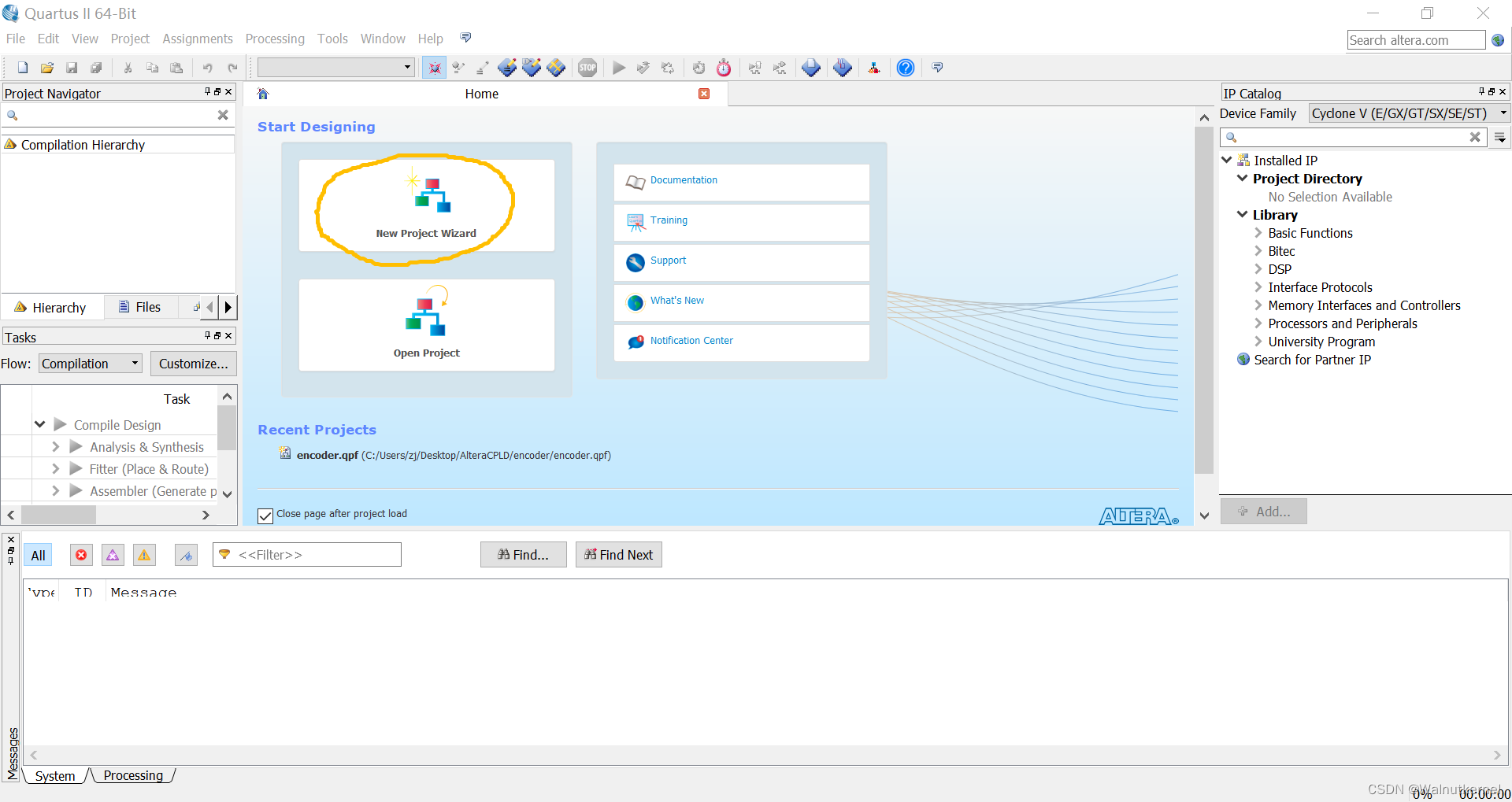

Altera的这款CPLD和Cyclone IV FPGA一样可以用Quartus来开发,前提是要安装MAX II的器件库。我用的是Quartus II 15.0。

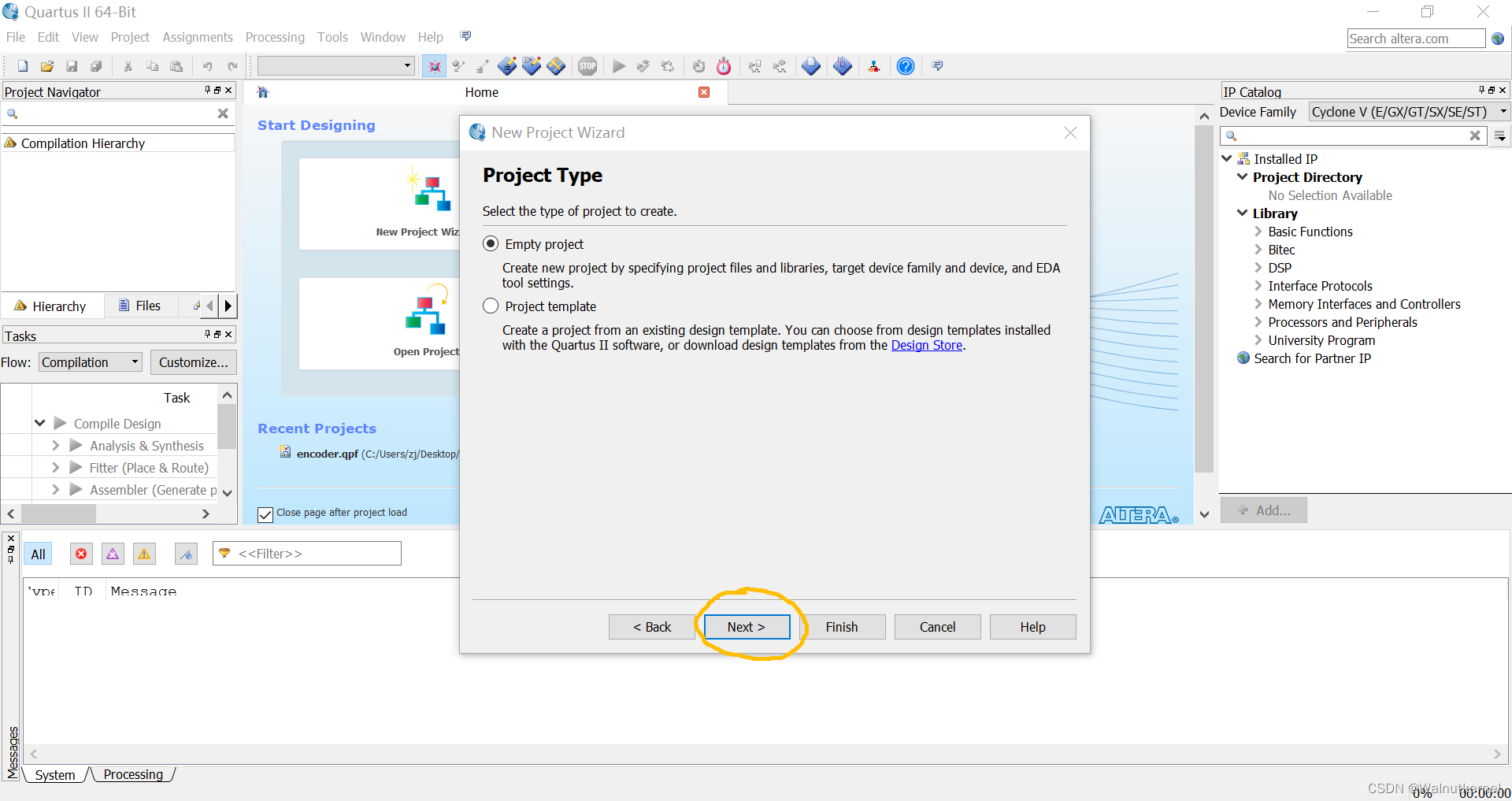

双击打开Quartus,点击New Project Wizzard开始新建工程。

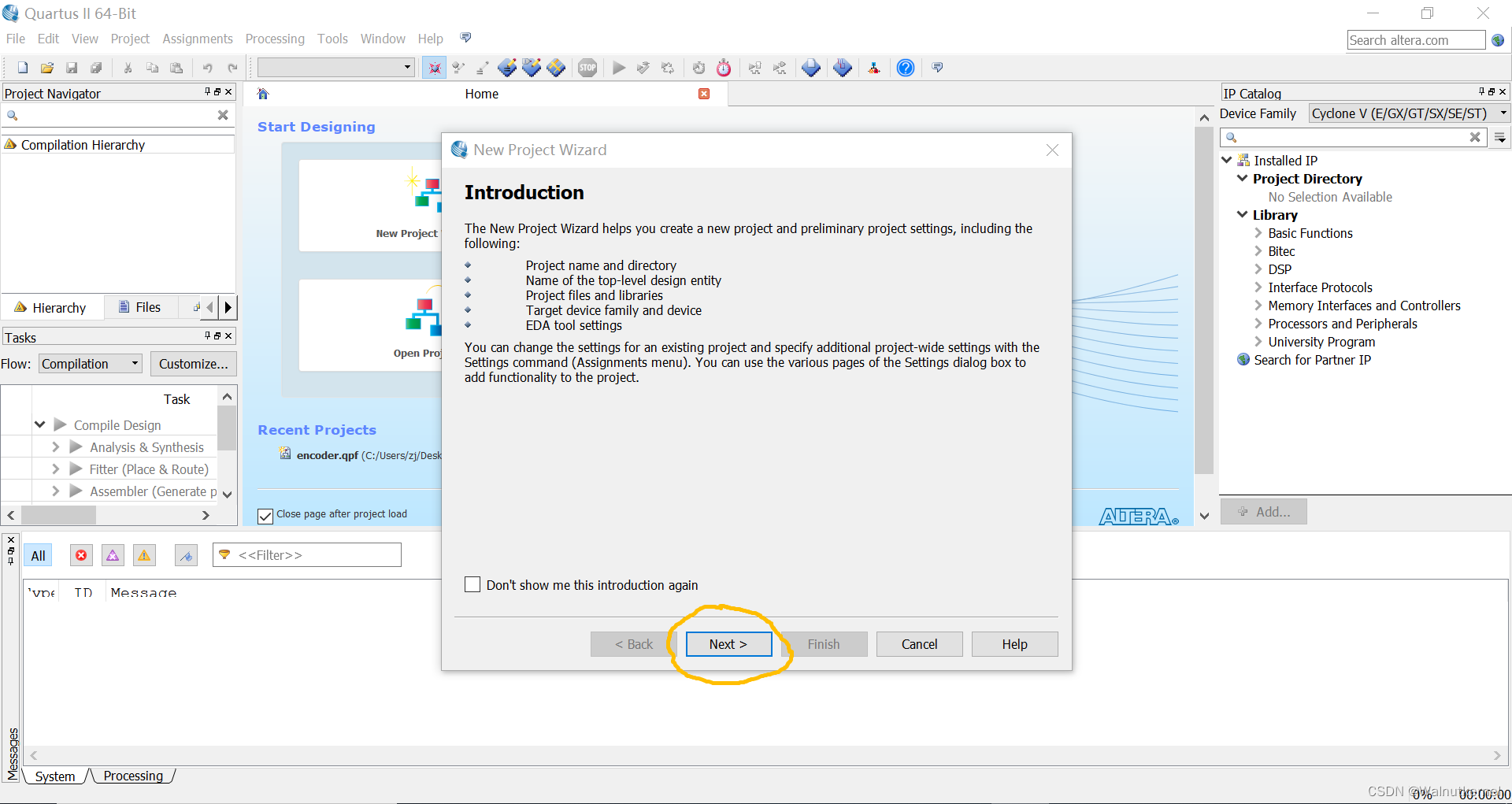

点击next

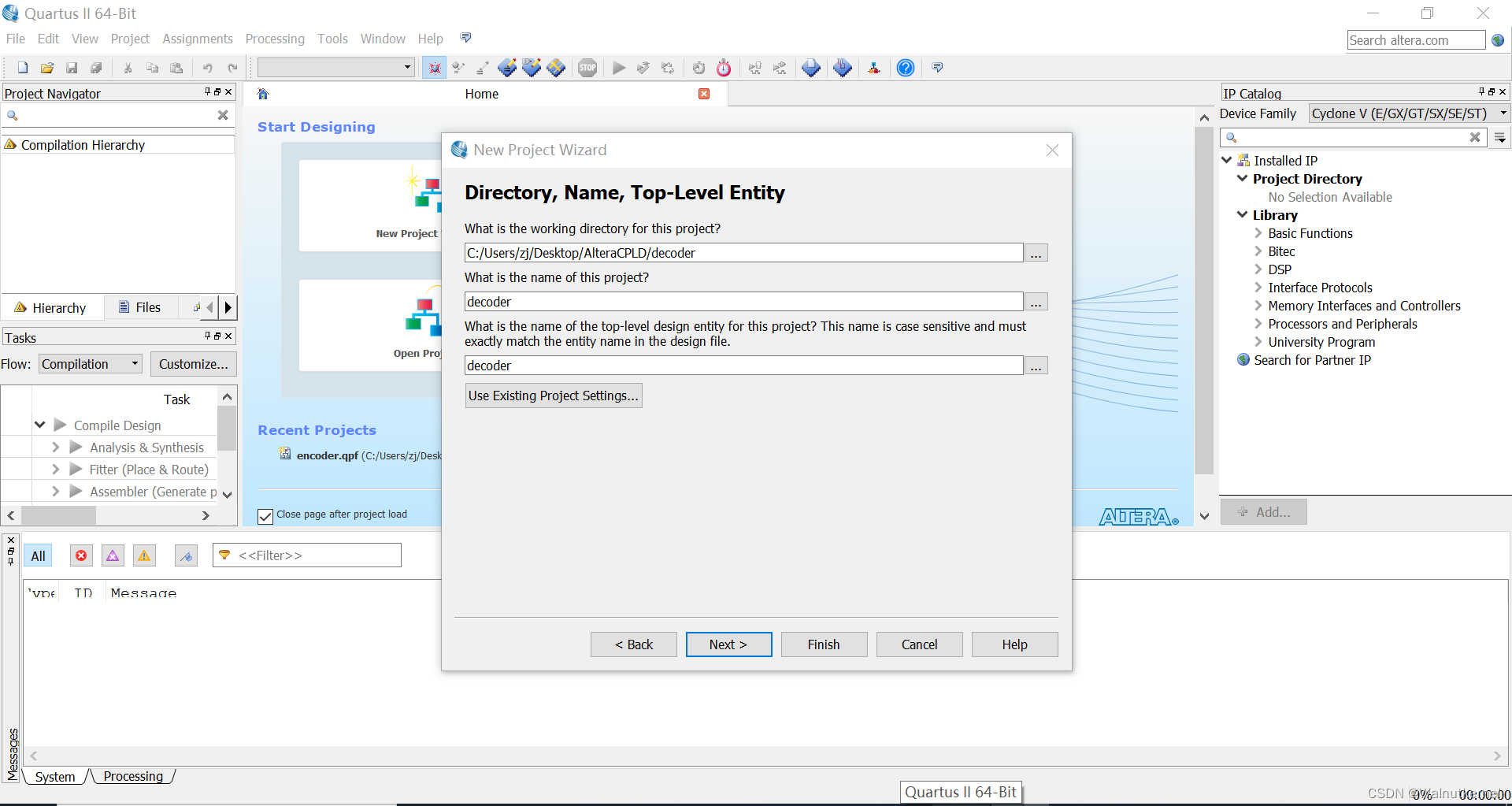

先为要建立的工程建一个文件夹,文件夹路径中不能有中文,新建的工程就放到这个文件夹里,我这里要做的是译码器,所以我建了名为decoder的文件夹,工程名也叫做decoder。

点击next

这里不用添加文件,还是点next

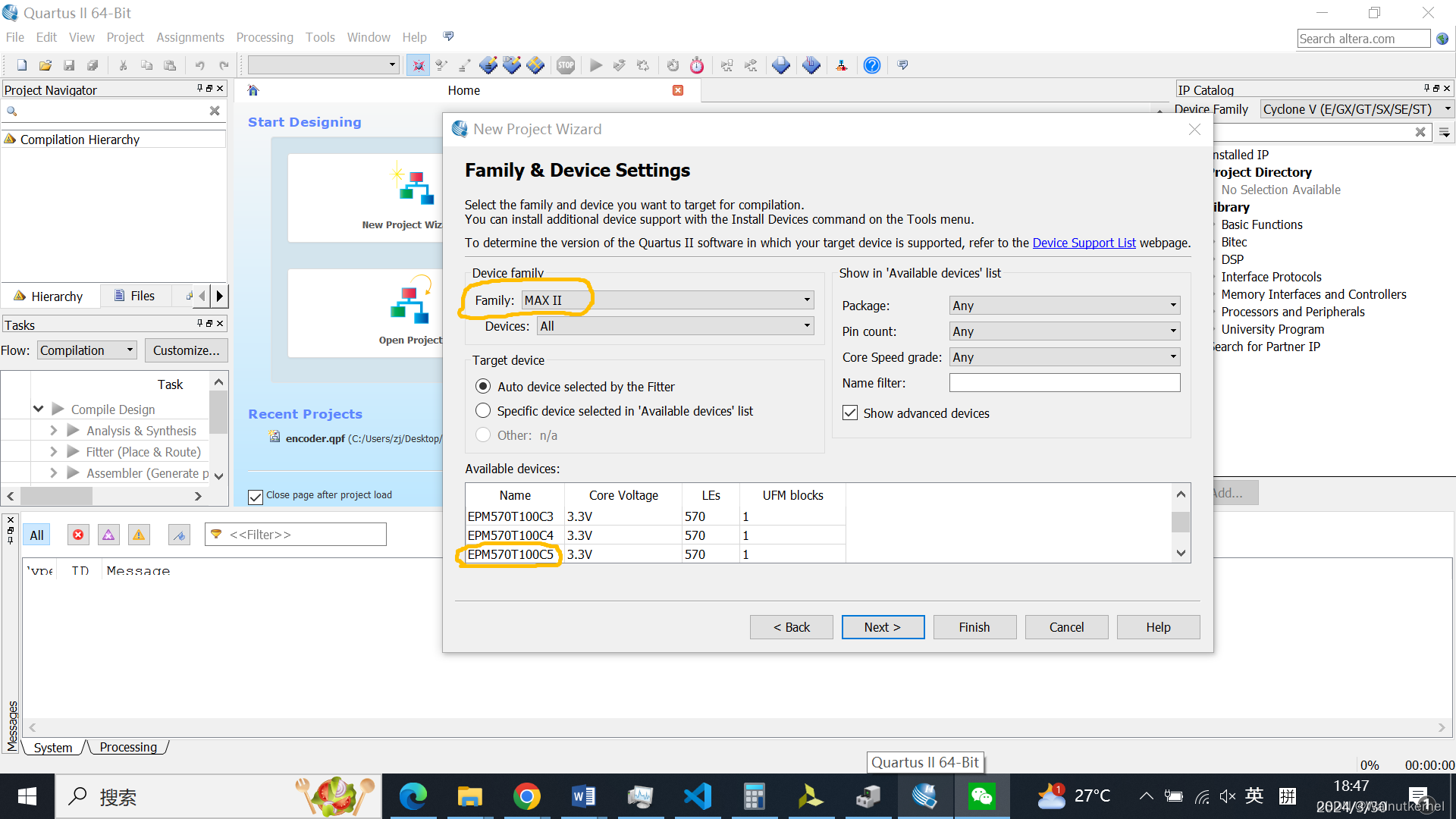

Family选择MAX II,Available devices选择EPM570T100C5

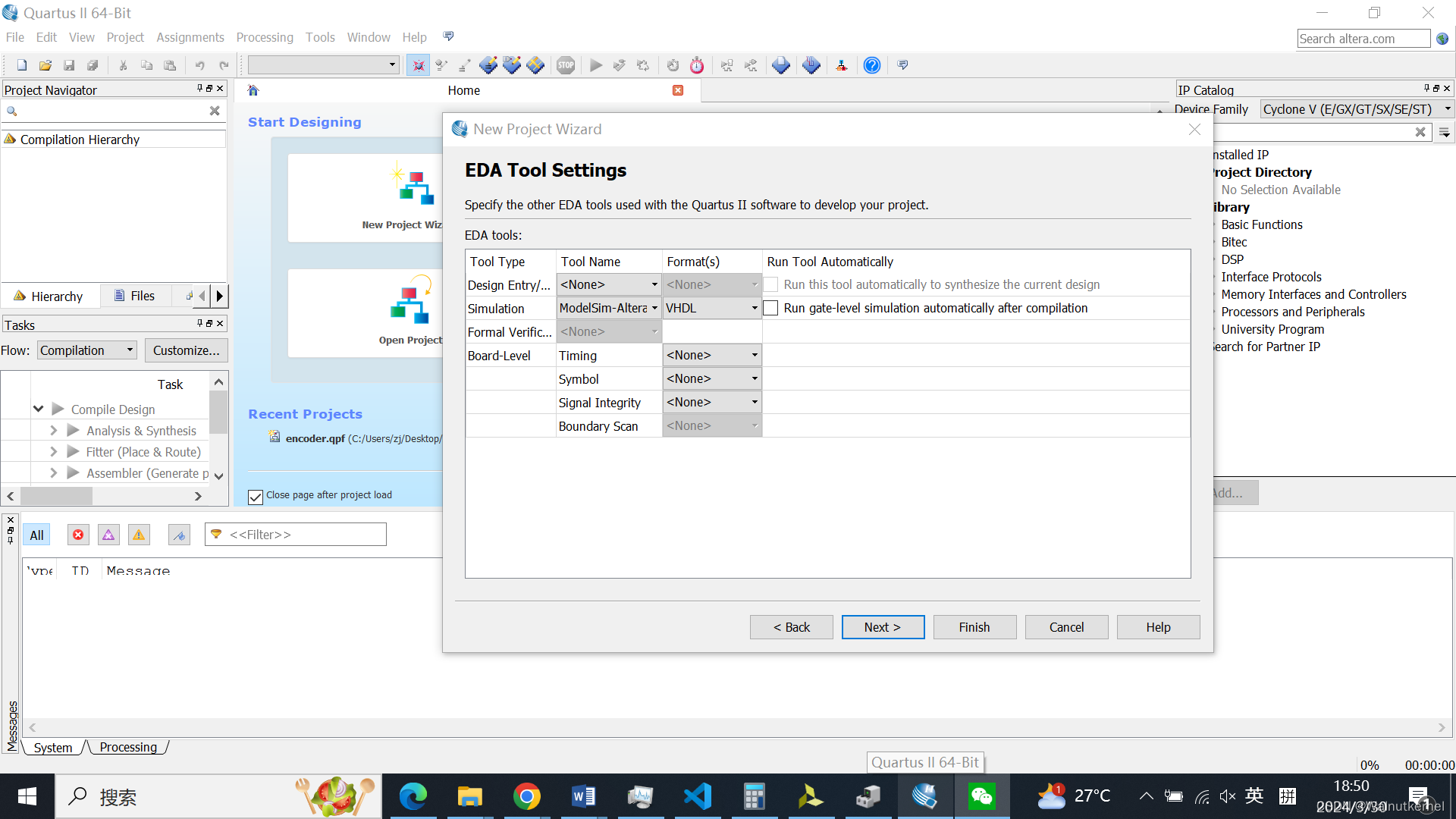

EDA Tool Settings这里点击next

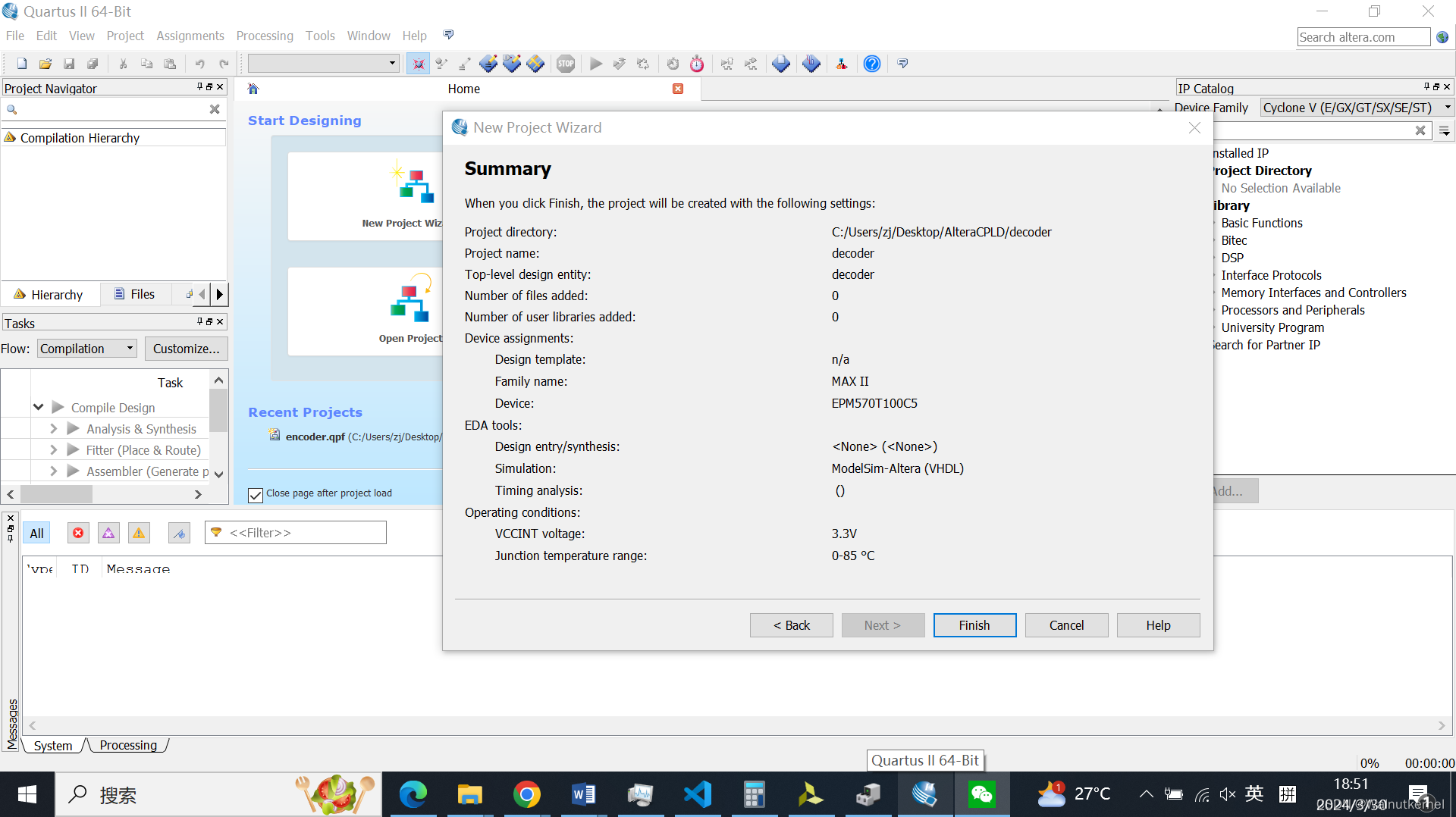

完成新建工程,点击Finish

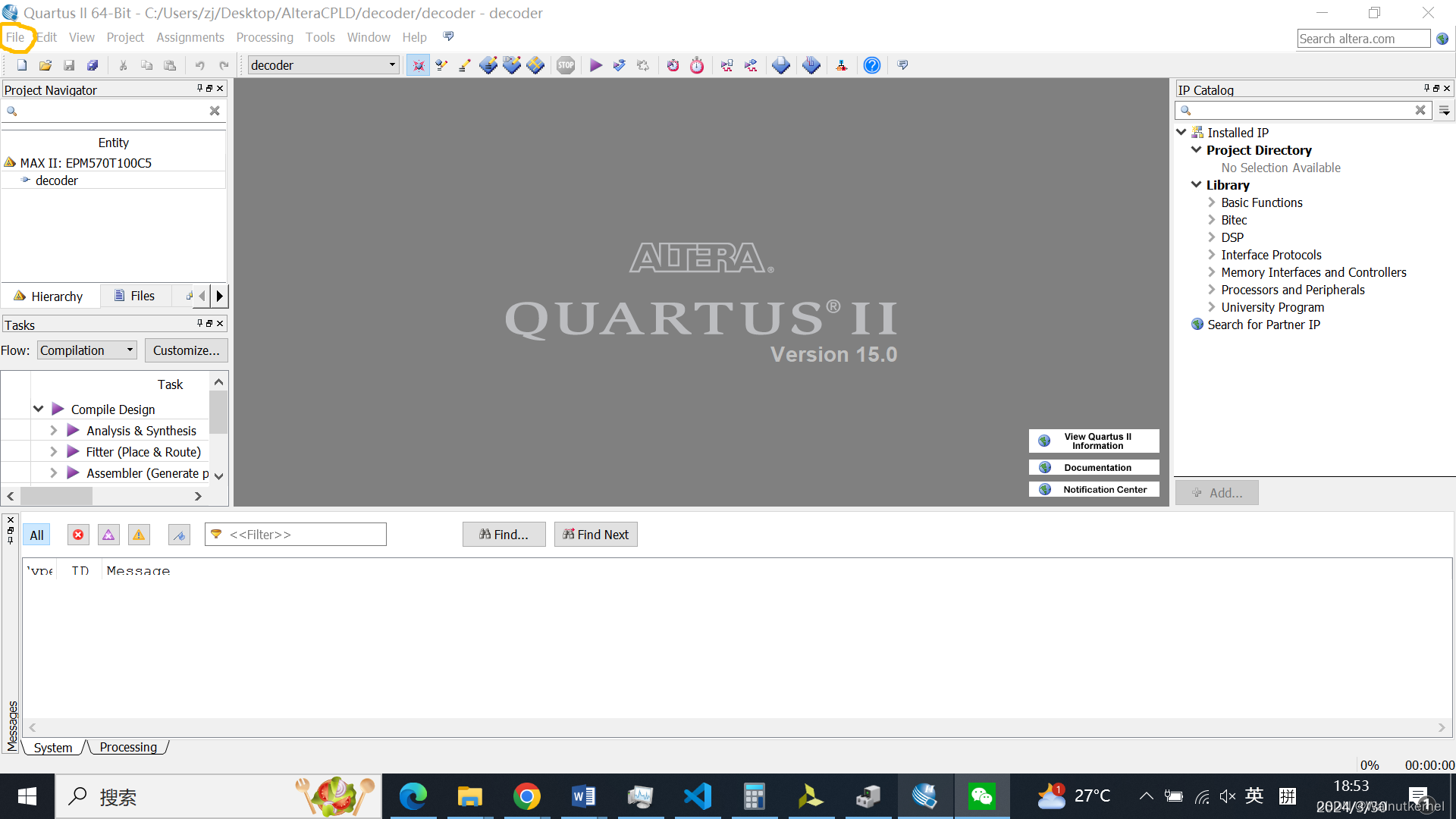

进到这个页面,点击左上角File,然后点击new新建文件

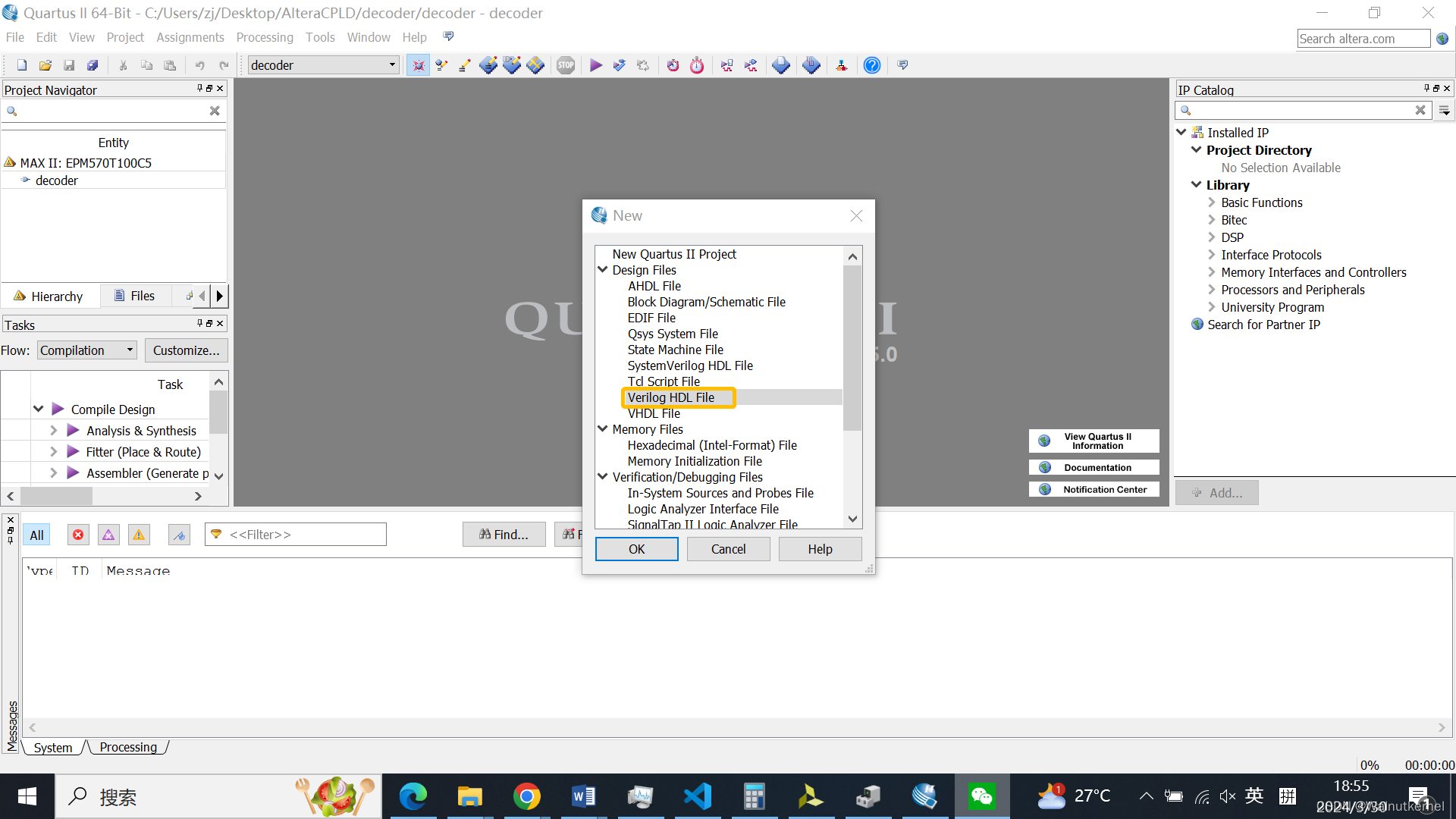

选择Verilog HDL File,然后点击ok

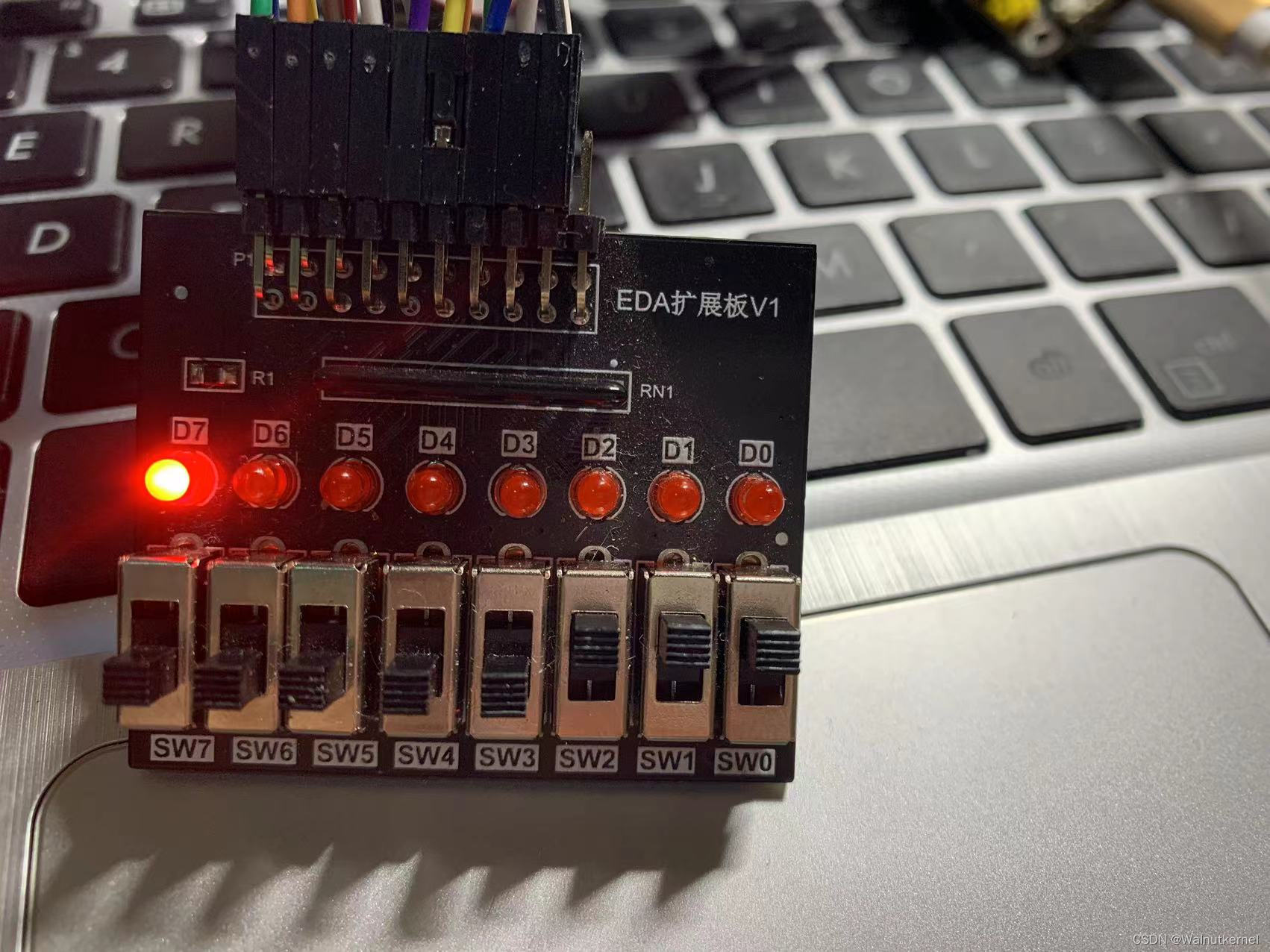

之后会生成一个名为Verilog1的文件,简单写一个3-8译码器,使用三个拨码开关作为输入,8个LED作为输出

module decoder (

clk,

sw,

led

);

input clk;

input [2:0]sw;

output reg [7:0]led;

always @(*)

case (sw)

3'b000 : led = 8'b0000_0001;

3'b001 : led = 8'b0000_0010;

3'b010 : led = 8'b0000_0100;

3'b011 : led = 8'b0000_1000;

3'b100 : led = 8'b0001_0000;

3'b101 : led = 8'b0010_0000;

3'b110 : led = 8'b0100_0000;

3'b111 : led = 8'b1000_0000;

default: led = 8'b0000_0000;

endcase

endmodule然后必须将文件名Verilog1改为与module后的名字相同,这里改为decoder,保存

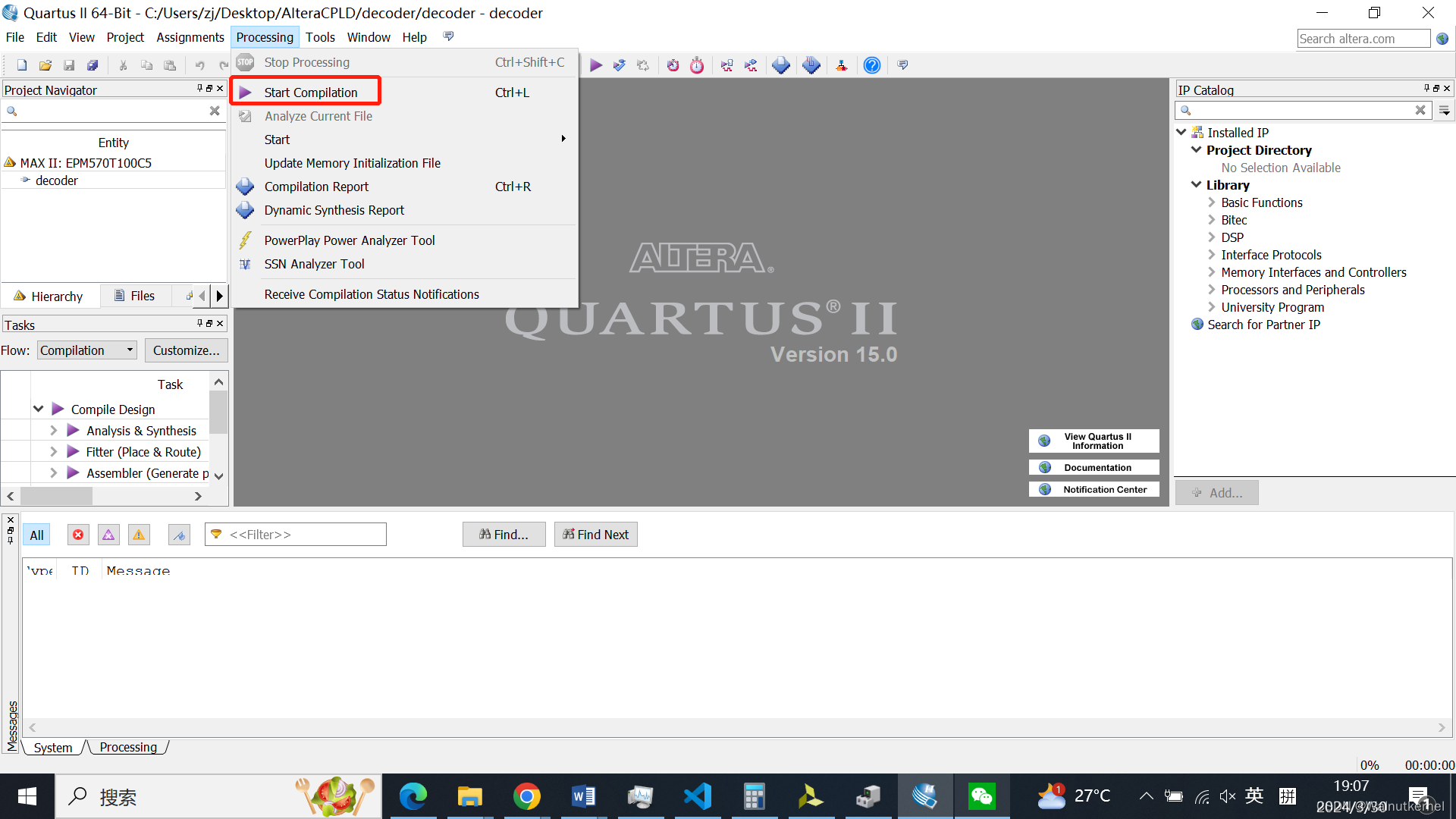

然后Processing/Start Compilation,综合一次

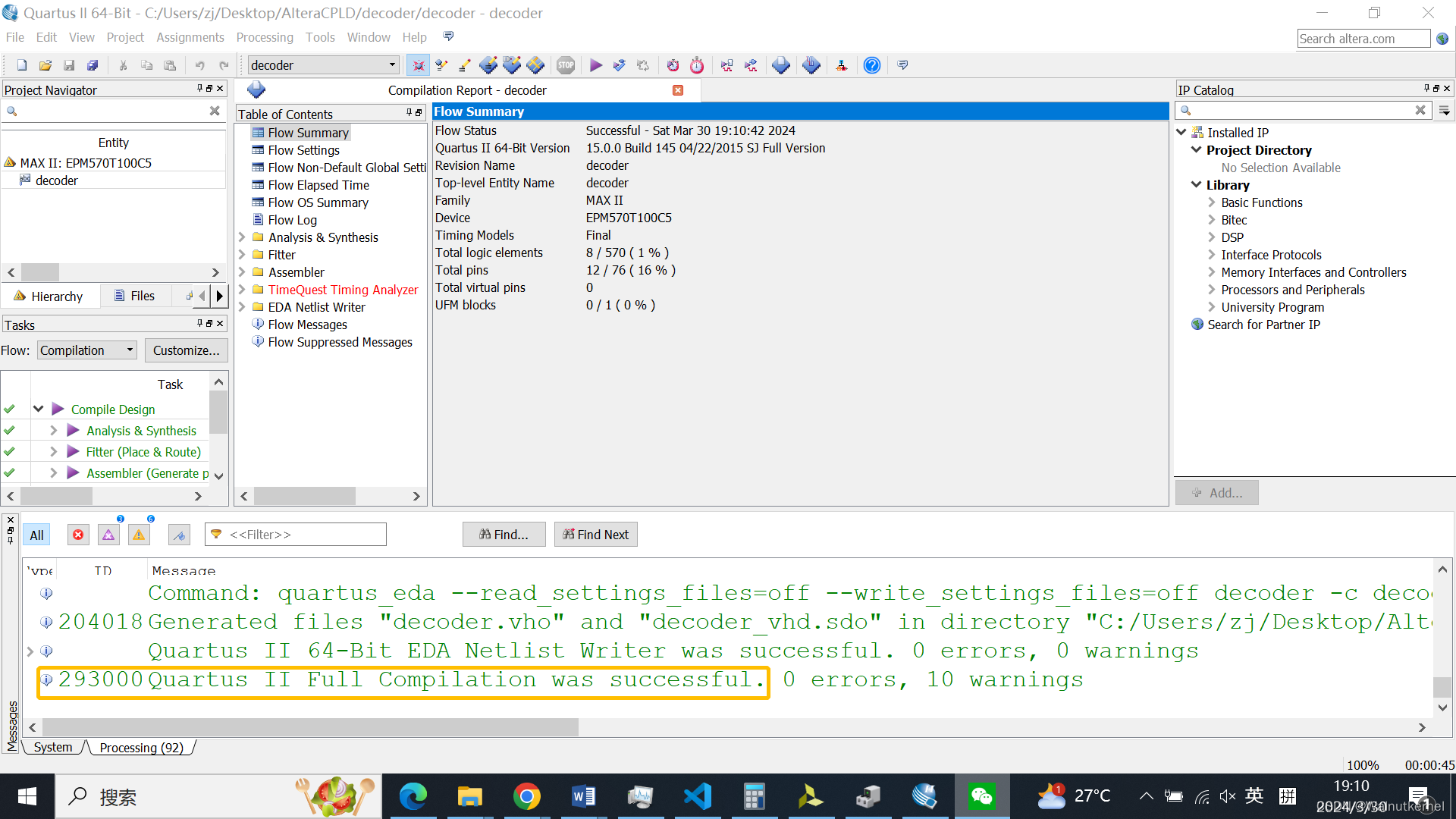

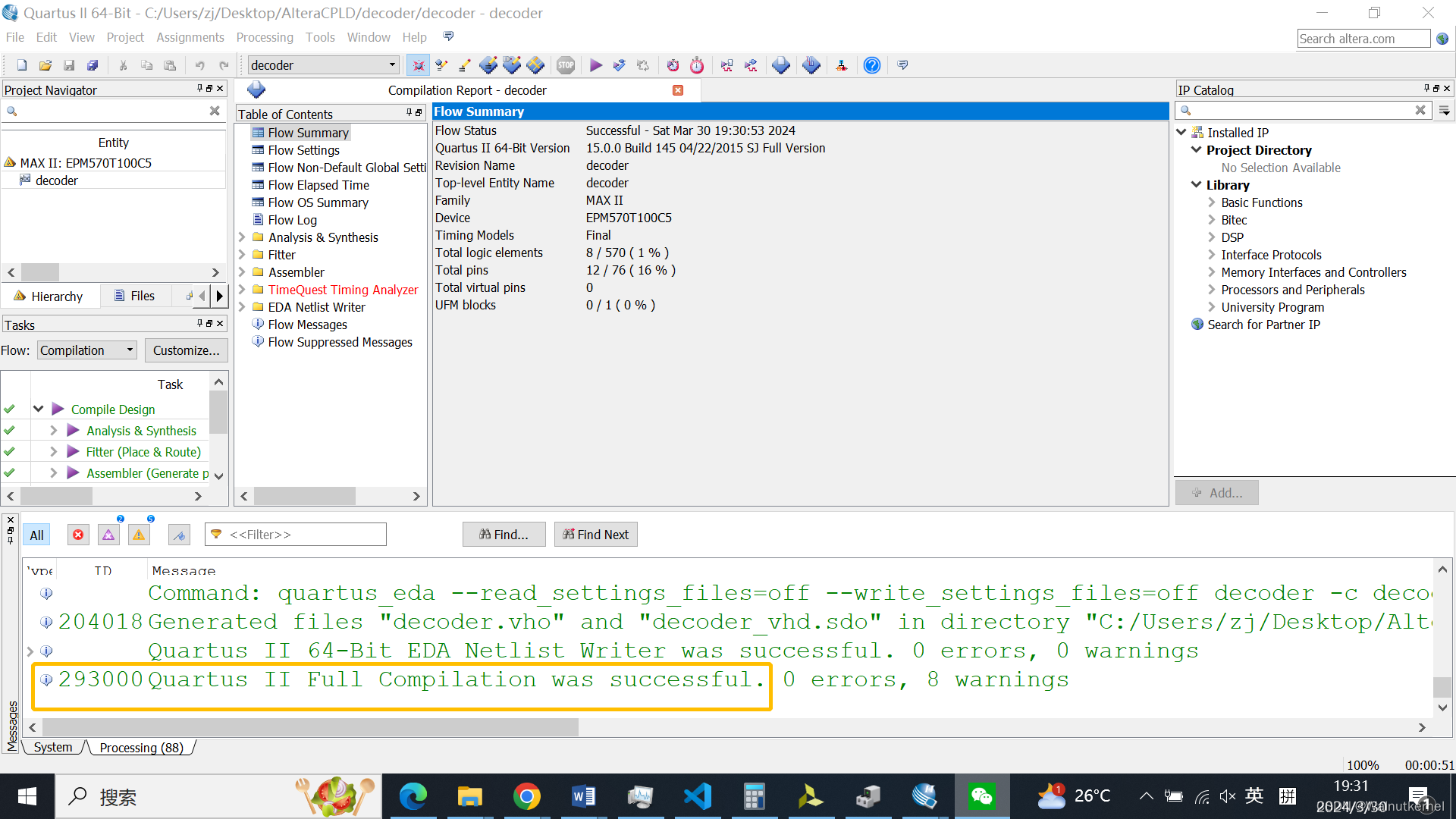

完成综合汇编,出现框中的提示代表综合成功

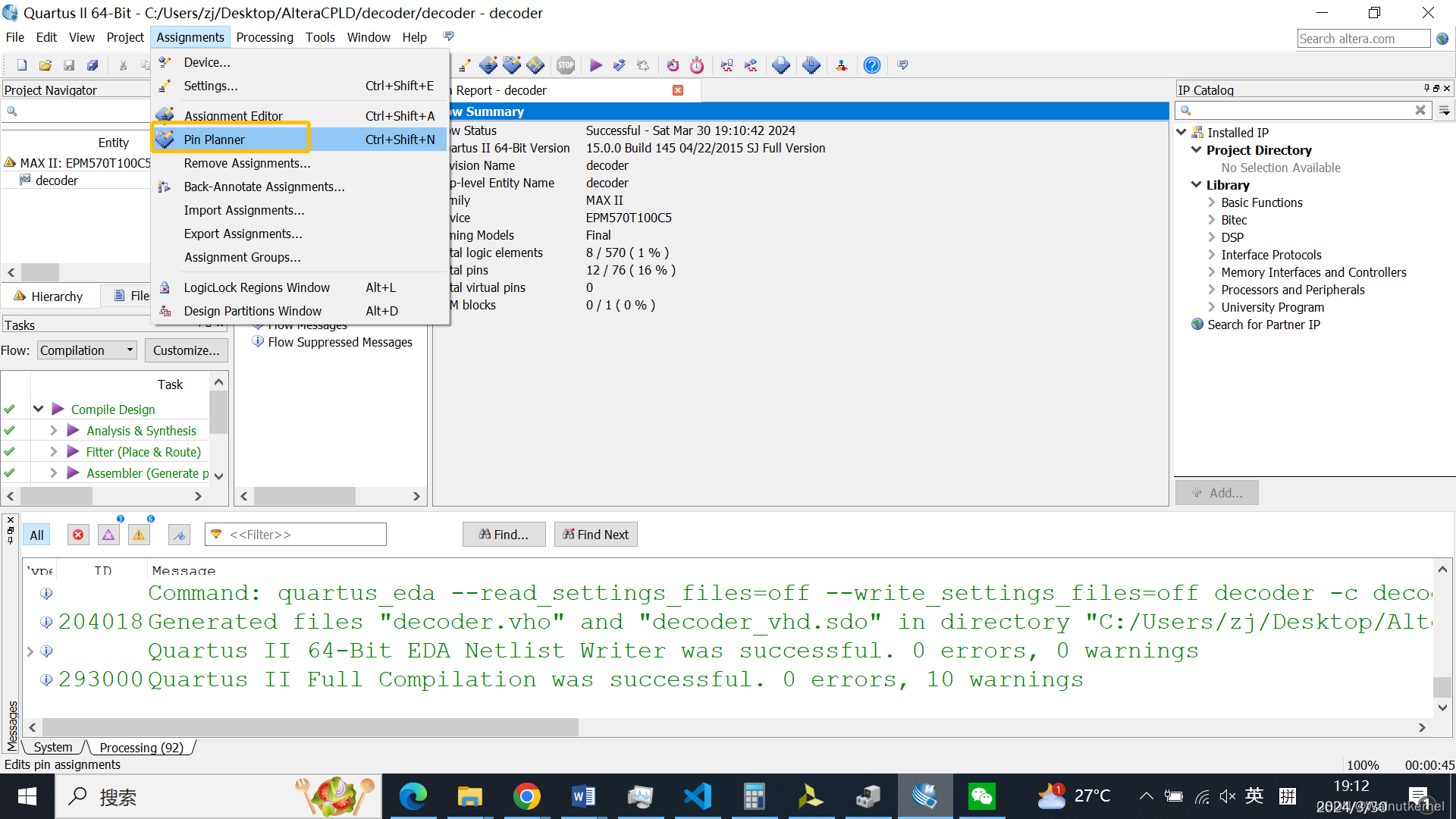

之后进行管脚分配,Assignment/Pin Planner

在这里按照自己的LED和拨码开关连接的引脚填入Location中 ,保存

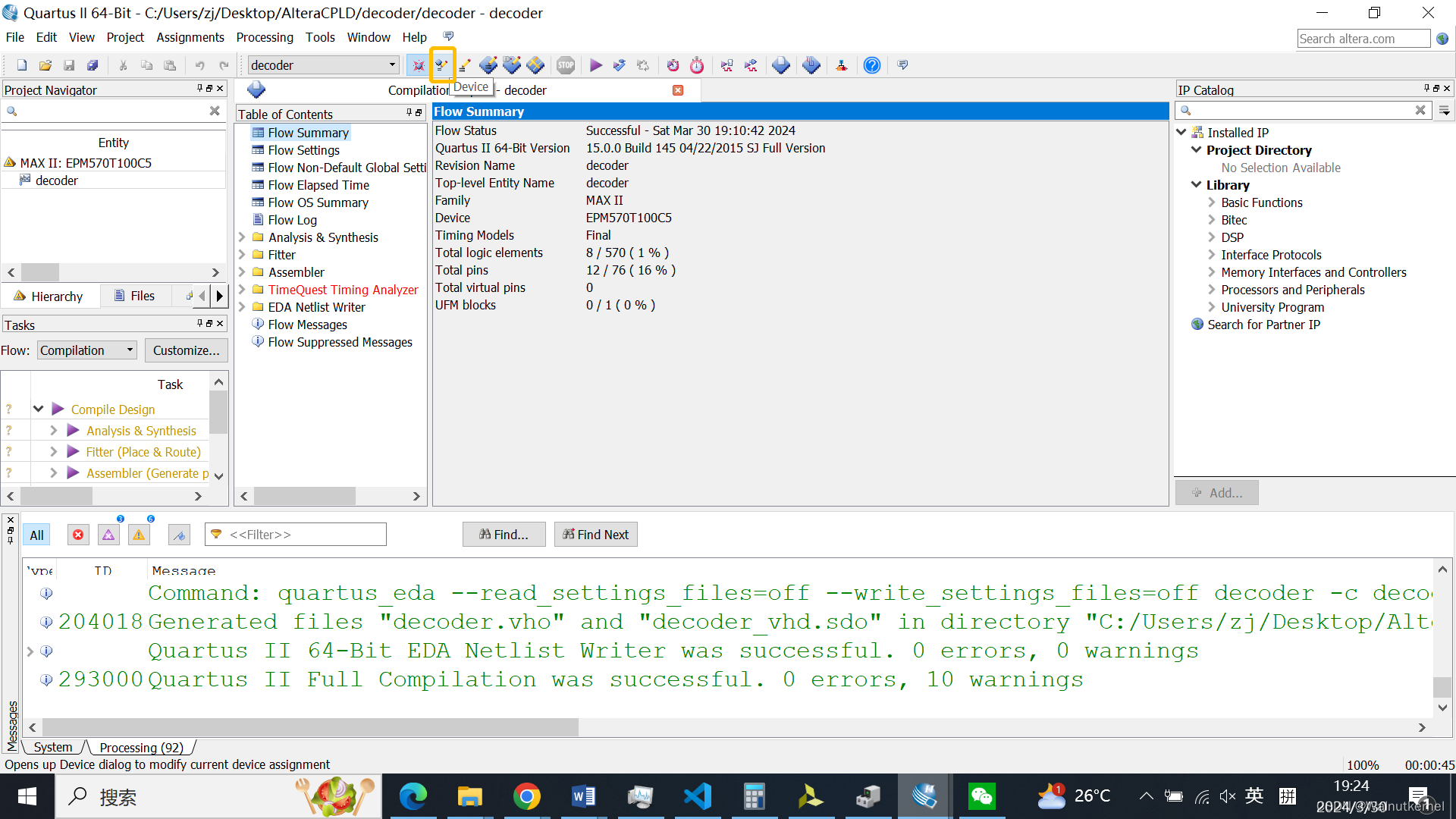

然后回到主界面,点击Device

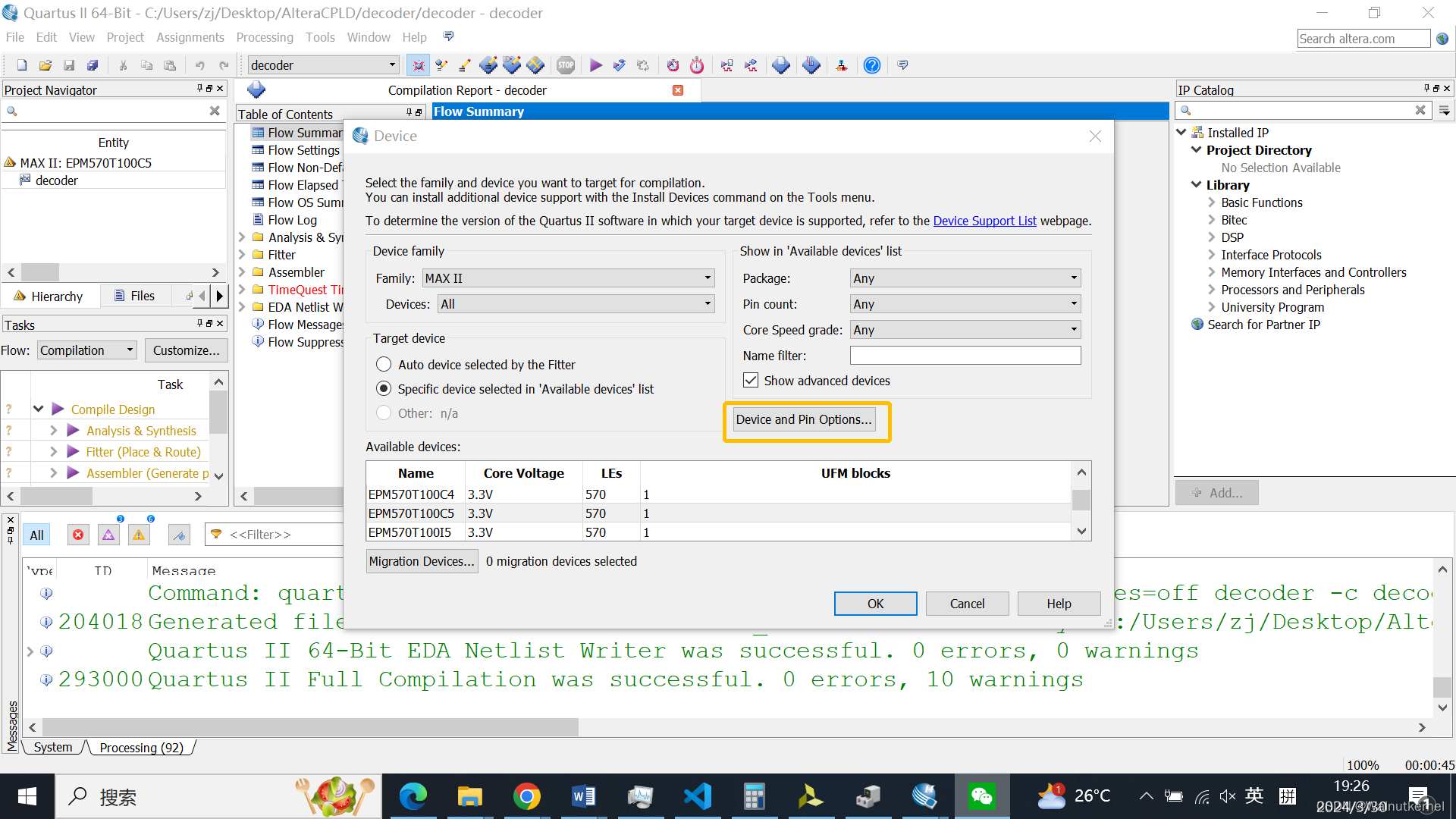

选Device and pin options

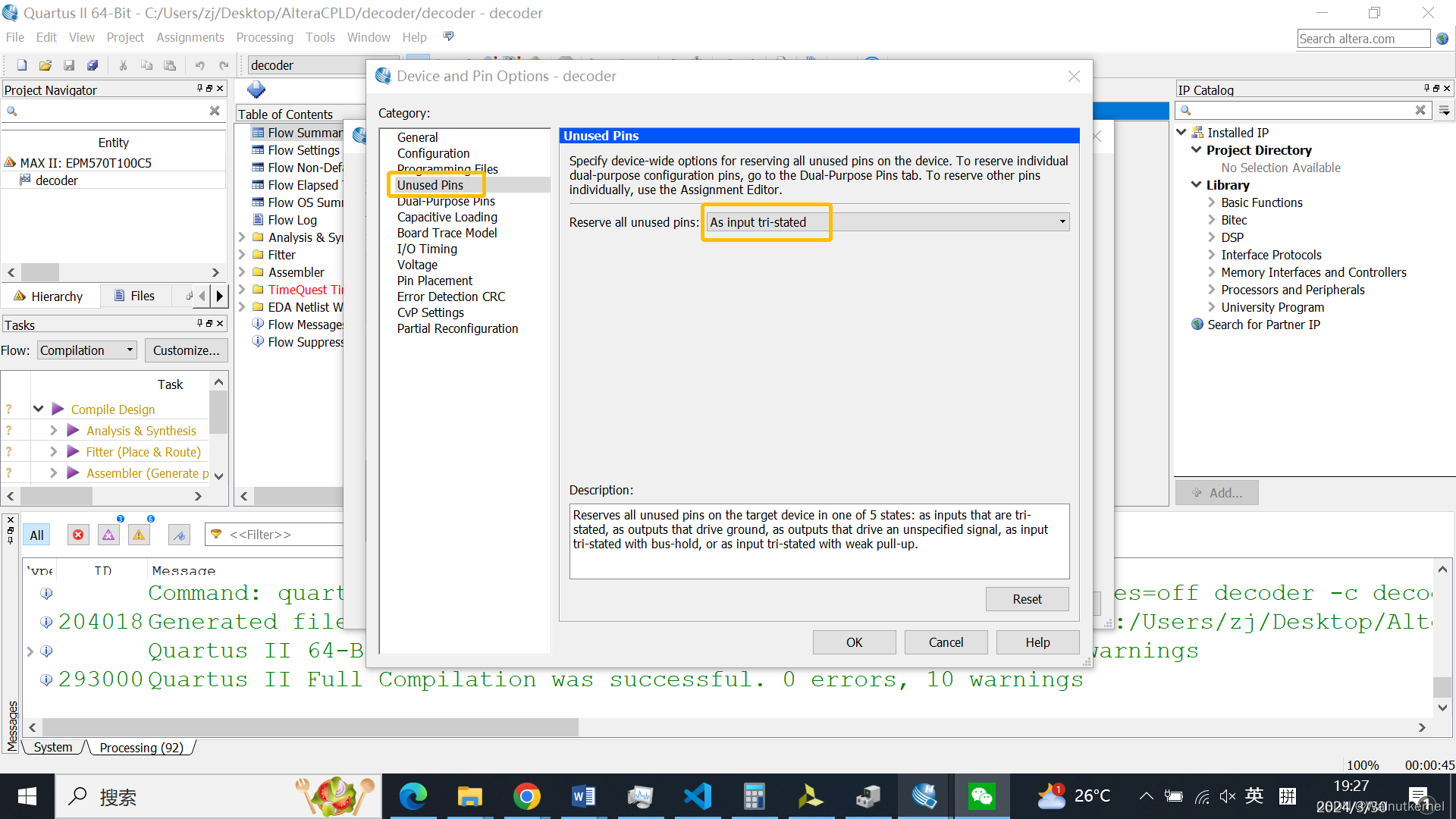

把未使用的引脚(Unused Pins)设为三态输入(input tri-stated),点击ok

然后重新Start Compilation综合一次,使前面的引脚分配和设置生效

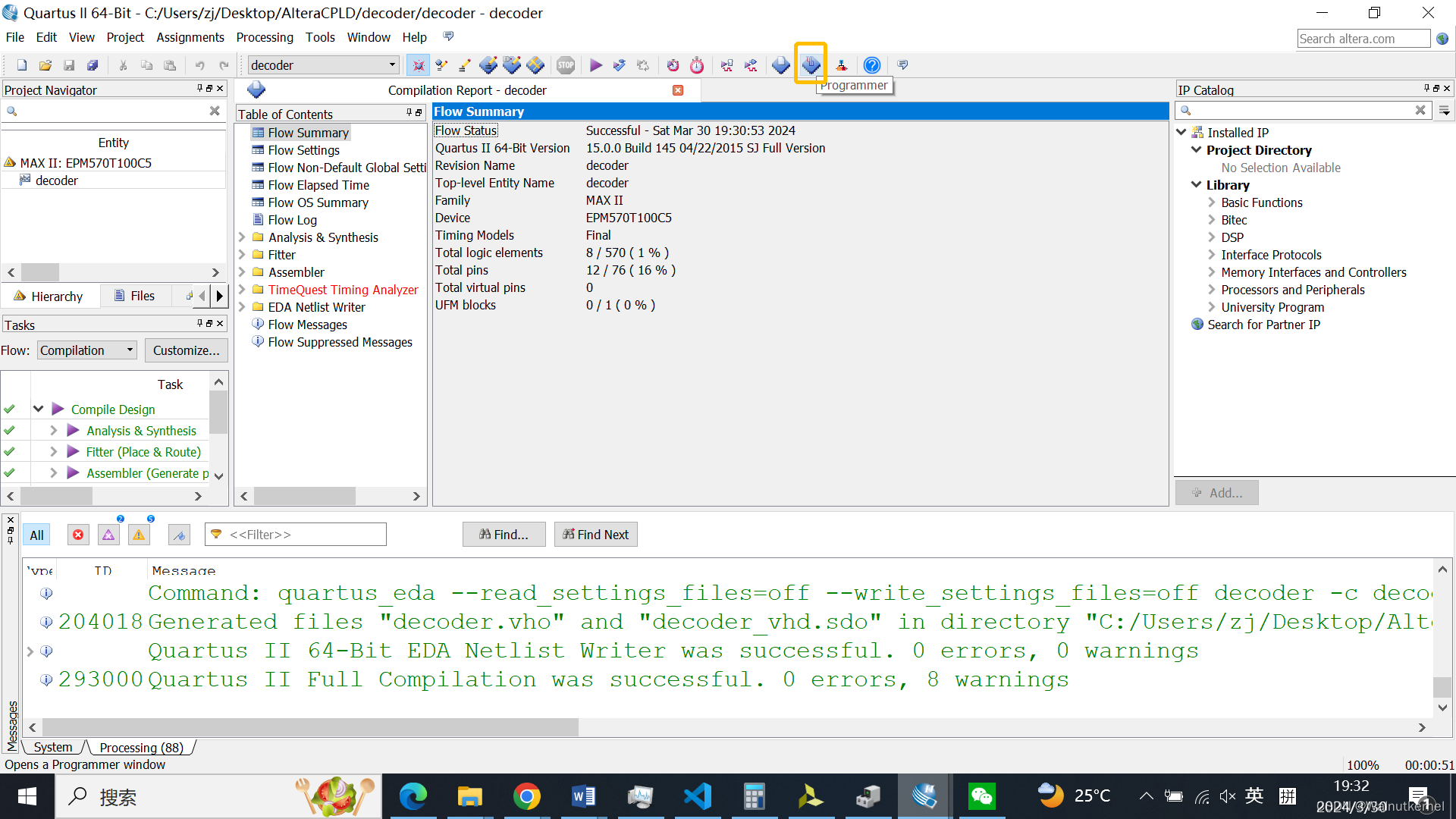

然后可以准备下载了,点击Programmer

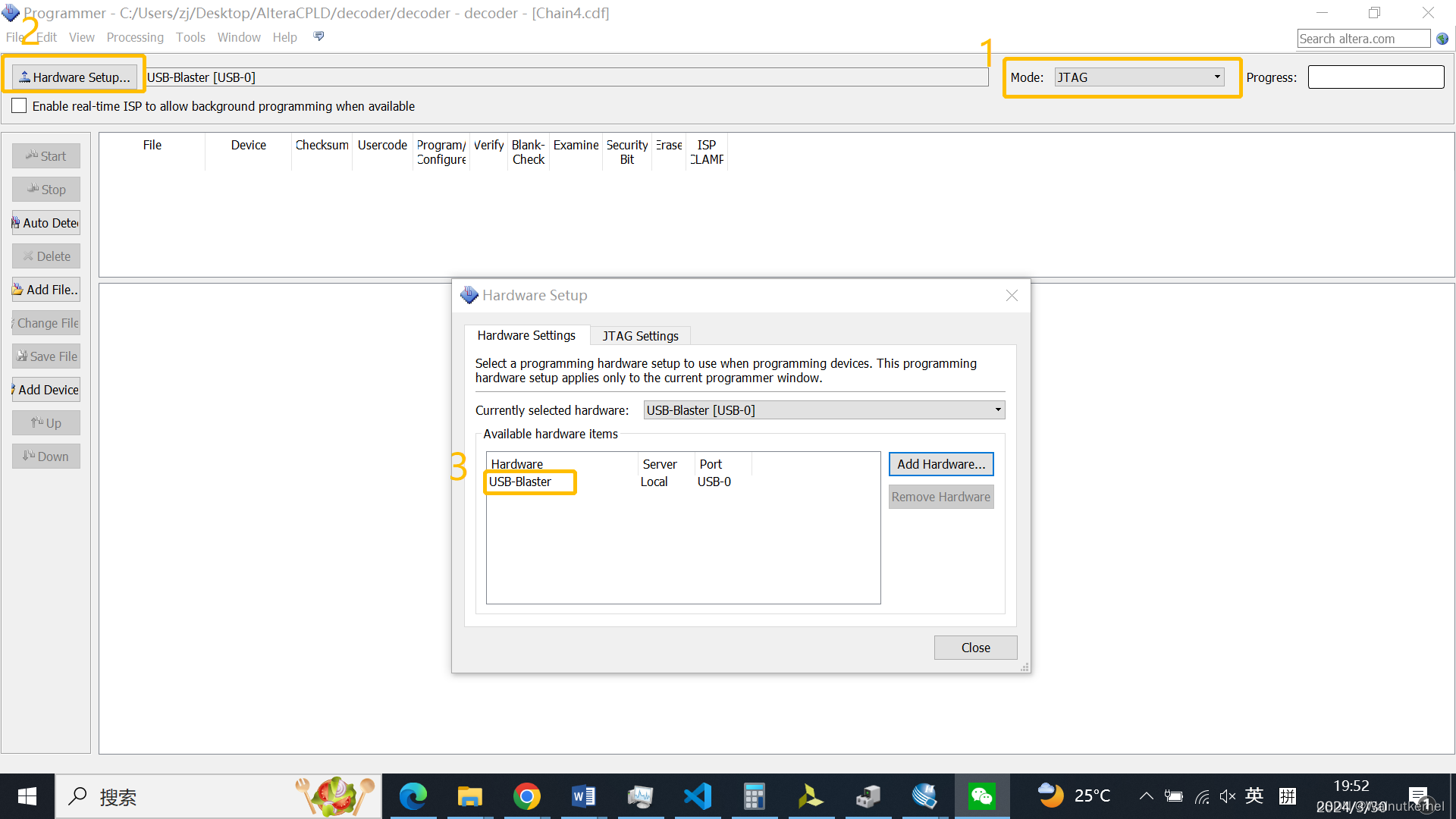

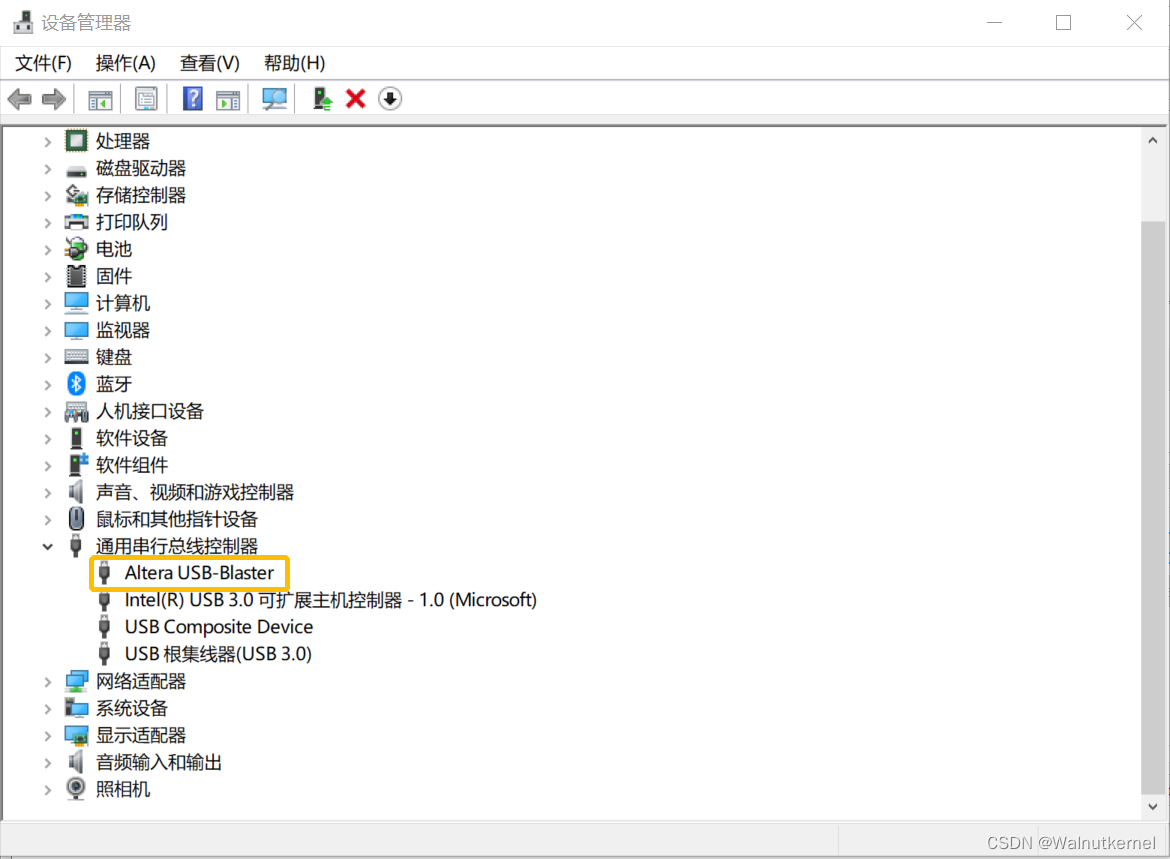

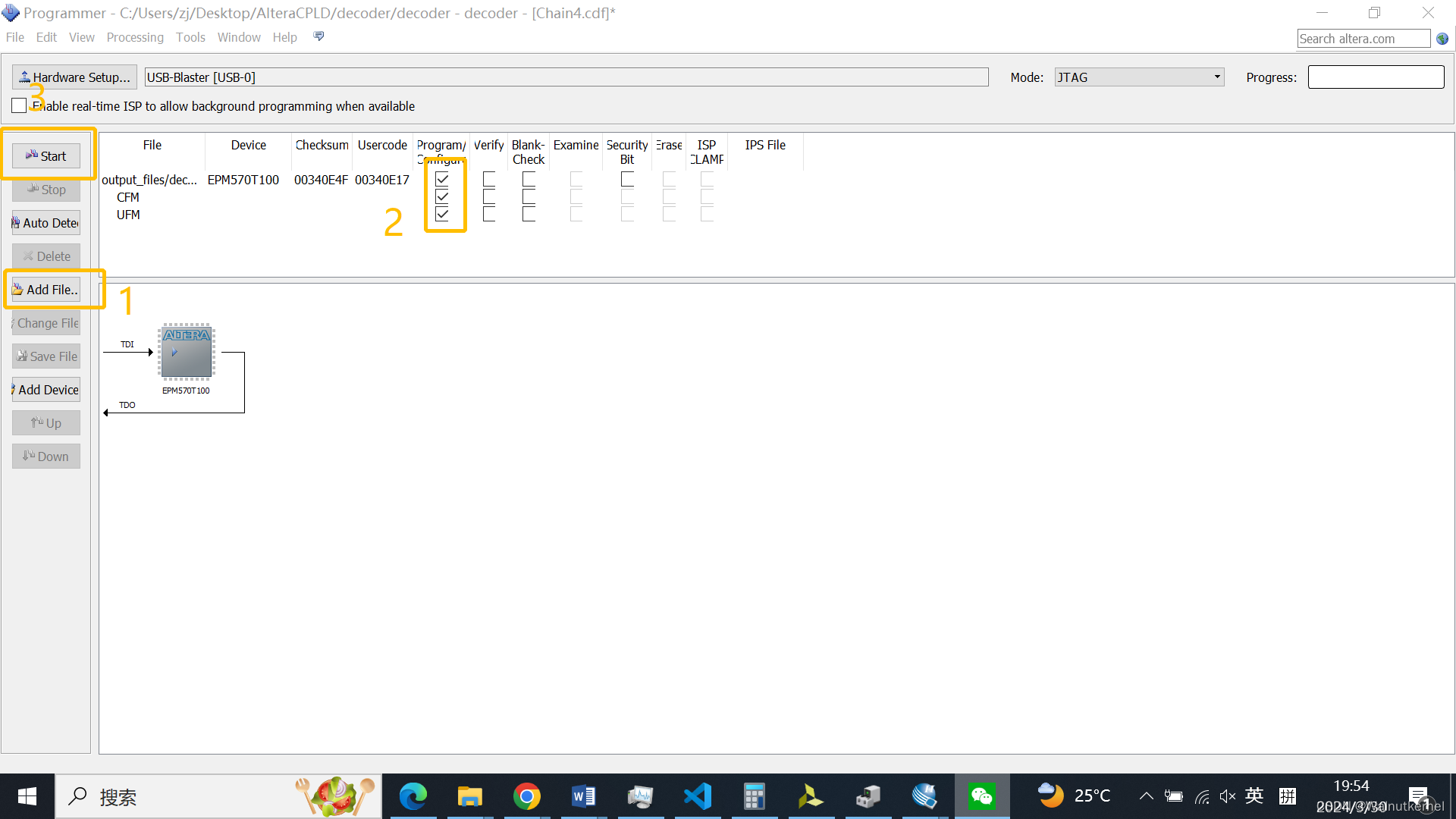

将USB Blaster连接到开发板,Mode设为JTAG,点击Hardware Setup,选择USB Blaster,如果没有USB Blaster,则要去设备管理器中看USB Blaster前是否有感叹号,如果是的话要装USB Blaster的驱动。

然后点击 Add File,在工程的文件夹目录下的output_file文件夹,把里面的.pof文件添加进来,打勾,然后start,就开始下载了,右上角可以看到下载进度

实现3-8译码器功能

本文详细描述了作者首次使用EPM570T100C5NCPLD在QuartusII15.0环境下创建并实现3-8译码器的过程,包括工程新建、文件编写、编译、管脚分配和下载步骤。

本文详细描述了作者首次使用EPM570T100C5NCPLD在QuartusII15.0环境下创建并实现3-8译码器的过程,包括工程新建、文件编写、编译、管脚分配和下载步骤。

394

394

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?