MSI:medium-scale integration

目录:

加法器

半加器:不考虑前面前一位是否有进位

输入:

输出:

本位和:

,模拟加法

本位仅为

,同为1即进位

全加器

输入:

输出:

本位和:

,模拟加法

本位进位:

,三个输入有任意两个为1即进位

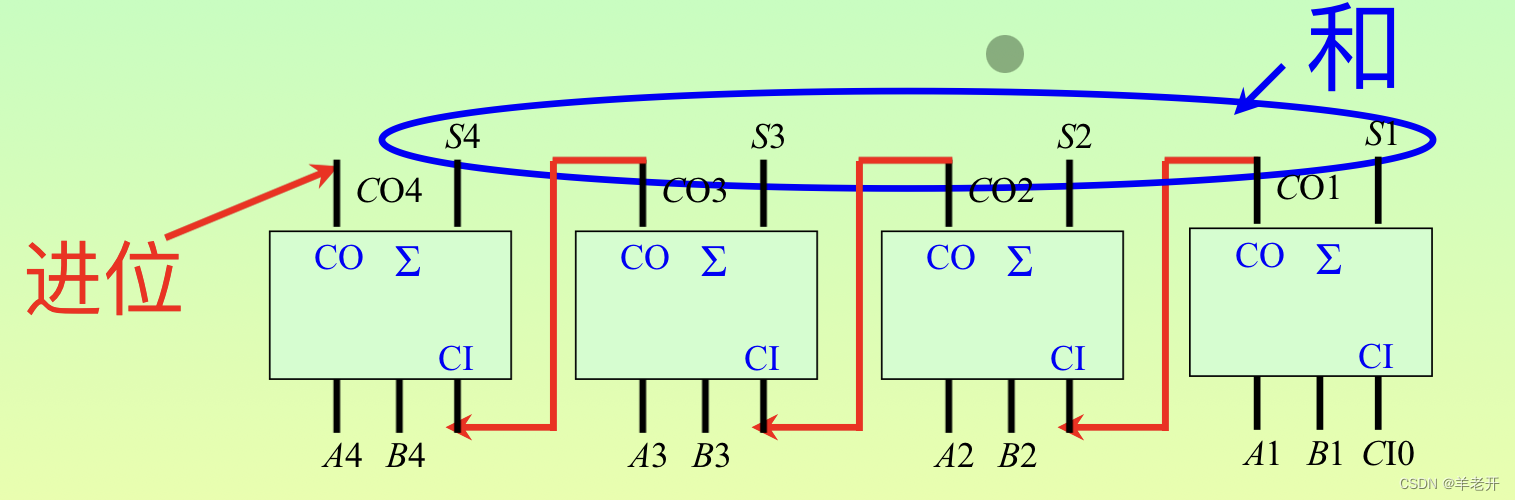

全加器实现四位二进制加法

超前进位加法器(4位超前进位加法器74LS283)

原理:

,输入一个1且进位为1的情况+ 输入为两个1的情况,可以往下推,最终化为AB、C的逻辑表达式

输入:

、

输出:

、

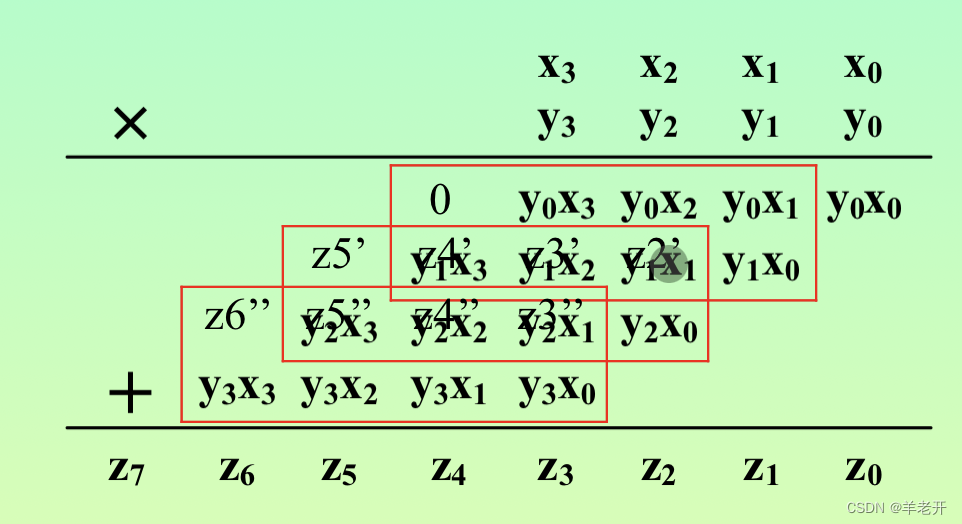

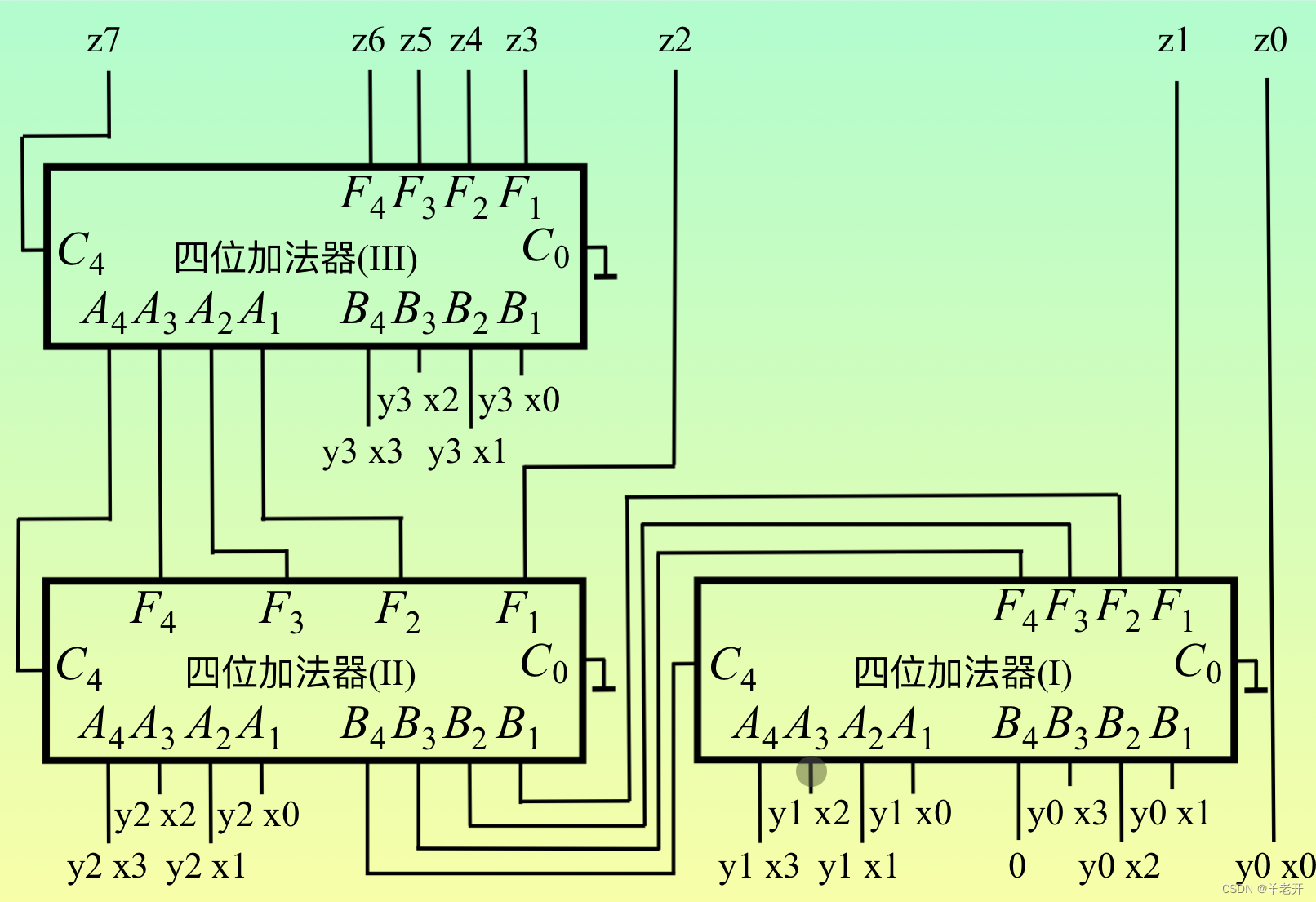

超前进位加法器实现四位数乘法

设计电路:

电路实现:

数值比较器

一位数值比较器

输入:

输出:

本文详细介绍了MSI(中规模集成电路)中的各种数字逻辑器件,包括加法器(如半加器和全加器)、超前进位加法器的应用,数值比较器的一位和多位实现,二进制和二-十进制译码器的功能,以及编码器的基本模型和优先编码器的工作原理。此外,还讨论了多路选择器和数据分配器在实现组合逻辑函数和数据传输中的作用。

本文详细介绍了MSI(中规模集成电路)中的各种数字逻辑器件,包括加法器(如半加器和全加器)、超前进位加法器的应用,数值比较器的一位和多位实现,二进制和二-十进制译码器的功能,以及编码器的基本模型和优先编码器的工作原理。此外,还讨论了多路选择器和数据分配器在实现组合逻辑函数和数据传输中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2574

2574

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?