目录

1、状态图模型要素

状态图中最关键的模型元素是状态和转移。状态是指在对象的生命周期中满足某些条件、执行某些活动或等待某些事件的条件或状况。有两类特殊的状态:起始状态和终止状态。 一个对象从一个状态改变成另一个状态称为状态转移,在状态图中用带箭头的连线表示。利用工具条中的按钮可以为状态图添加相应的状态和状态转移。

2、 几种类型

2.1初态(start state)

➢

显示状态图中状态机执行(

execution

)的开始

➢

一个状态机

只能有一个

初态,因为每一个执行都是从相同的地方开始的。如果一个状态机用多张状态图描述,则多张图用一个初态, Rose 中只允许画一个初态,其它地方拖动使用

➢

嵌套状态中可以使用新的初态

2.2终态 (end state)

➢

表示最后的或者终端状态;

➢

终态

数目可以不确定,也可以没有。

➢

电扇 坏了

/

没坏,但拆下闲置

➢

音乐,刘德华

/

体育,姚明

2.3 中间状态

中间状态的组成

(除初态终态外,最常见的状态)

➢

状态名(

name

)

◼

是可以把该状态和其他状态区分开的字符串

;

状态也可能是匿名的,即没有名称。(状语 在上课 灯亮着 门关着)

➢

入口

/

出口动作(

entry/exit action

)

➢

内部转换(

internal transition

)

◼

不导致状态改变的转换,不会执行

entry

和

exit

动作

◼

内部转换和自转换的区别:

➢

前门-入口,后门-出口

➢

不出去,只在内部发生的转换-内部转换

➢

从后门出去,又从前门进来-自转换,自转换会引起

entry

和

exit

动作的执行

➢

子状态(

substate

)

◼

嵌套在另外一个状态中的状态

◼

空调:停止、运行状态,运行状态中可嵌套制冷、制热、除湿等子状态

➢

延迟事件(

deferred event

)

◼

是指在该状态下暂不处理,但将推迟到该对象的另一个状态下排队处理的事件

2.4组合状态

◼含有子状态的状态被称为组合或嵌套状态

◼两种表示方法

➢顺序子状态

◼

如果一个组成状态的子状态对应的对象在其生命期内的任何时刻都只能处于一个子状态,即多个子状态之间是互斥的,不能同时存在,这种子状态称为顺序子状态。

➢

并发子状态

◼

有时组合状态有两个或者多个并发的子状态机,此时称组成状态的子状态为并发子状态。

◼

顺序子状态与并发子状态的区别在于后者在同一层次给出两个或多个顺序子状态,对象处于同一层次中来自每个并发子状态的一个时序状态中。

2.5历史状态(History state)

➢

使用历史状态,可以存储目前退出组合状态时所处的子状态,则返回组合状态时可以直接回到相应的子状态。

3、状态图建模步骤

➢

寻找主要的状态

➢

确定状态之间的转换

➢

细化状态内的活动与转换

➢

用组合

/

嵌套状态来展开细节

4、几种状态图举例

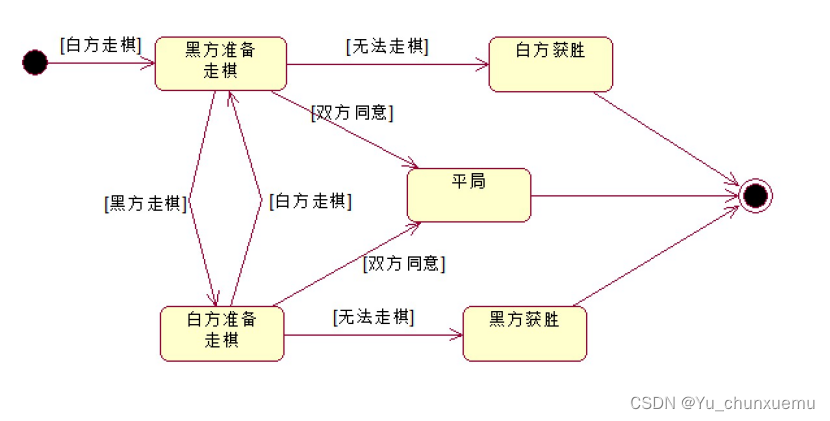

- 绘制黑白棋游戏状态图。游戏双方称为黑方和白方白方首先走第一步,然后黑白双方轮流走棋如果有一方不能继续走棋,则另一方获得胜利,游戏结束如果双方同意平局,则游戏结束

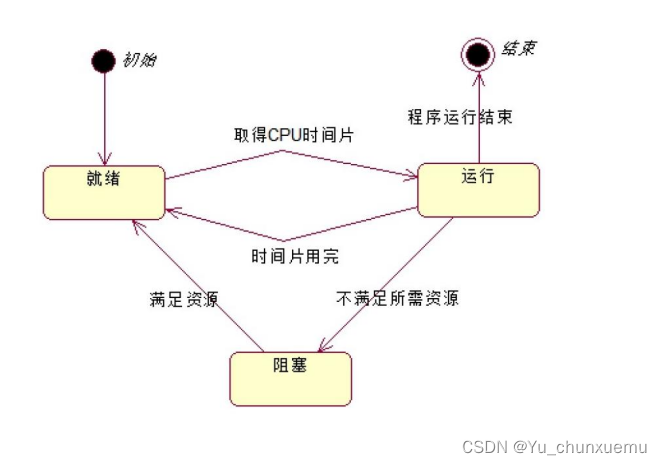

2.绘制进程状态图。操作系统-进程,就绪 运行 阻塞三个状态,初态就绪; 程序运行结束后终态,就绪态获得CPU时间片转为运行态;运行态时间片用完转为就绪态;运行态不满足所需资源转为阻塞态,阻塞态若资源满足则回到就绪态

3.对用户使用手机拨打电话的过程建立状态模型。手机开机时,处于空闲状态,当用户开始使用电话呼叫某人时,手机进入拨号状态。如果呼叫成功,即电话接通,手机就处于通话状态;如果呼叫不成功,如对方线路问题、关机、拒接等,这时手机停止呼叫,重新进入空闲状态。手机在空闲状态被呼叫。如果用户接听电话,用户处于通话状态;如果用户未做出任何反应,可能他没有听见铃声,手机一直处于空闲状态。

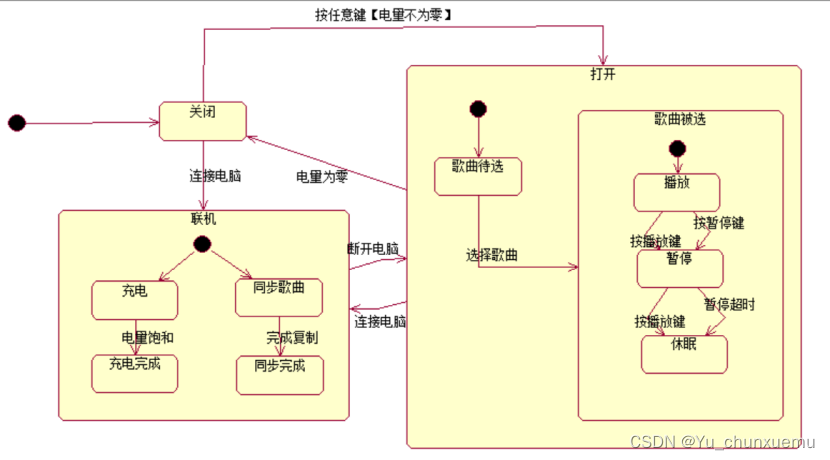

4.绘制CD播放器的状态图。关闭,打开(选曲 播放 暂停 休眠),联机(充电 同步歌曲)

5.图书管理系统状态图的绘制。

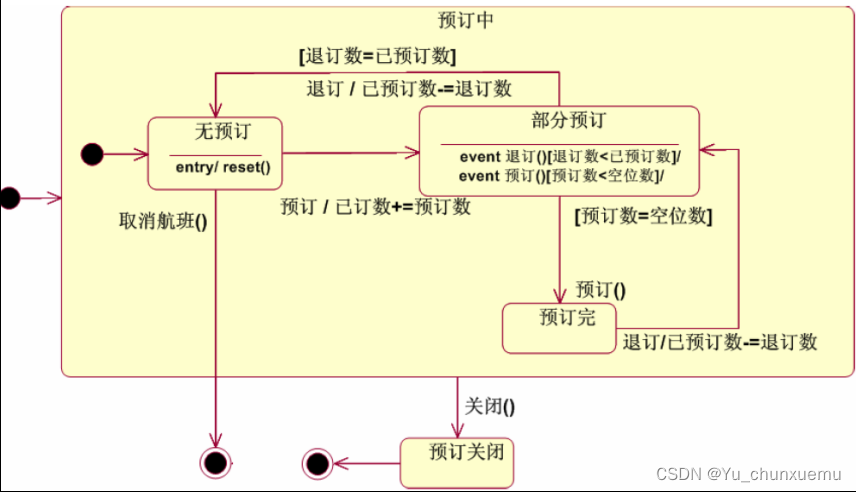

6.航班座位预定状态图

1881

1881

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?