spectre(cadence的仿真器)是在spice基础上进行扩展和延申,在仿真的过程中,也是提取spice网表,再进行计算和分析。HSpice(synopsys)的图形界面不够完备。

MOS管等分立器件的Spice模型+仿真条件+仿真类型。

Spertre仿真缺点:

1、速度慢;

2、难以用vpulse、vpwl等各种模拟信号发生器部件来生成数字电路用的复杂数据流;

3、难以获得时序信息(spertre+Verilog)混合模式的仿真器。

Hspice:

可以仿真模拟电路、混合信号电路、精确数字电路、建立Soc的时许及工号单元库、分析系统级的信号完整性。仿真速度快。

缺点:没有图形化界面。

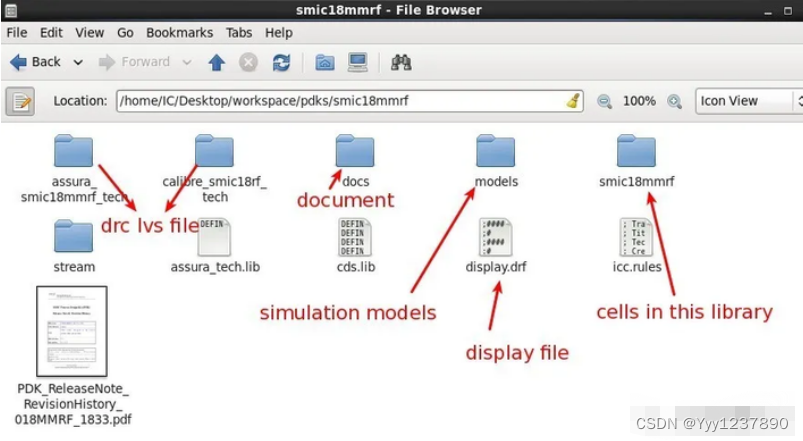

PDK:procss design kit

仿真模型在model下面(会同时提供spectre model、spice model)

Cadence help-ADE L中cadence手册

Virtuoso Spertre Circuit Simulator and Accelerated Parallel Simulator User Guide.

如何用Hspice仿真?

- 绘制完原理图后,抽取CDL网表。File-export-CDL inv.cdl

- 添加信号源(source)、仿真模型(库、工艺角)、HSPICE的仿真设置(仿真类型)。(学习语法) inv_sim.sp

- 电路网表和激励源保存在不同的文件中,实用include将电路网表调入激励文件

- 运行仿真:将文件放在一个目录下,打开终端,hspice inv_sim.netlist > inv_sim.outlog(如果CDL网表和激励源在不同文件,netlist改成sp)

netlist :运行HSPICE并仿真

sp:将仿真信息保存到inv_sim.log文件中,查看文件了解仿真器的输出信息,以及详细的工作状态。

- Wave viewer (终端输入wv启动 File-import waveform File,查看波形)

(50 封私信 / 59 条消息) 吉吉福唧唧 - 知乎 (zhihu.com)

1758

1758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?