一、什么是PLL IP核?

PLL:Phase Locked Loop,即锁相环。是最常用到的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望的时钟。

二、PLL IP核有什么作用?

对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望的时钟。

三、PLL基本工作原理

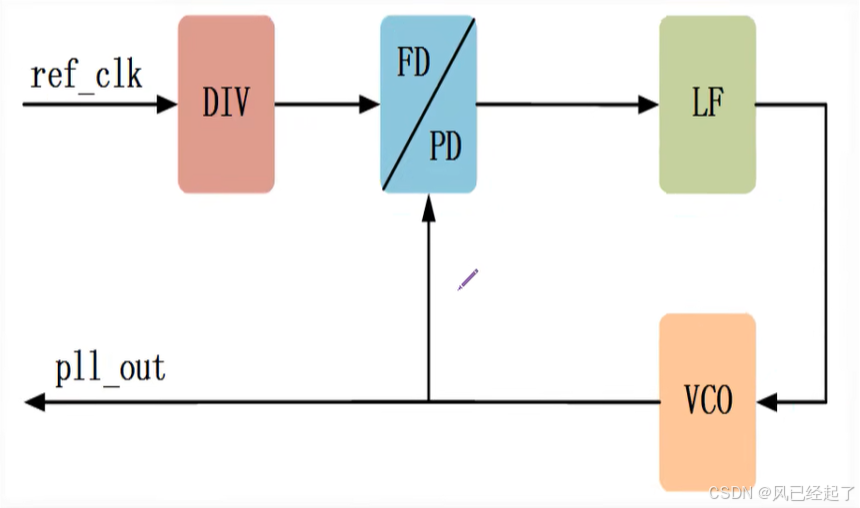

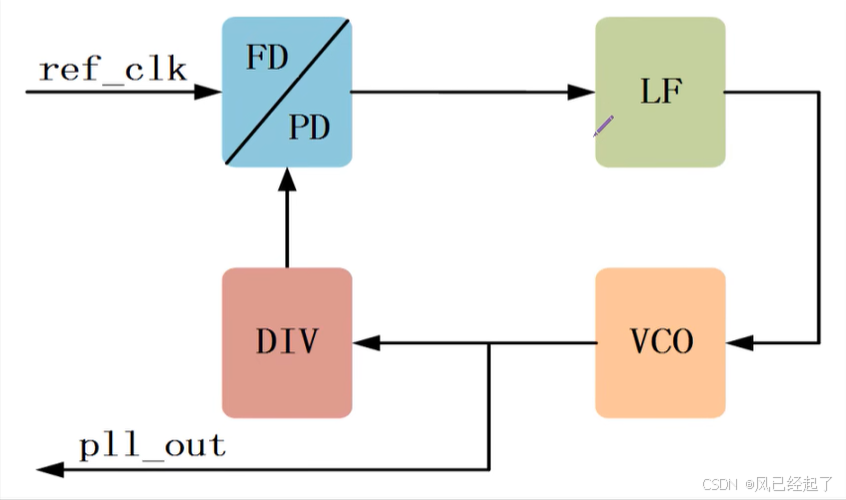

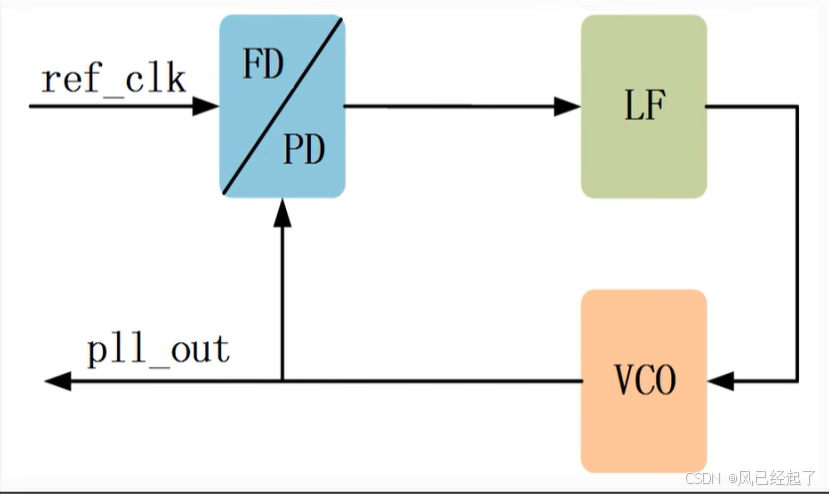

PLL是一个反馈系统,FD/PD是鉴频鉴相器,LF是环路滤波器,VCO是压控振荡器;

VCO会输出一个到FD/PD的比较时钟com_clk,FD/PD会把ref_clk和com_clk进行比较,如果输出的值为0,则说明ref_clk和com_clk的频率相同;如果ref_clk大于com_clk则输出一个变大的成正比的值;如果ref_clk小于com_clk则输出一个变小的成正比的值。将这个值传入到LF中,然后输出不同电压幅值的信号,这个又会传入到VCO,输入到VCO的电压越高,VCO输出的频率越高。

1.分频

举个例子:输入的是50MHz,也就是ref_clk是50MHz,要进行一个二分频,输出的pll_out是25MHz,那么DIV就是2。因为要稳住输出的25MHz,所以FD/PD要等于0。

分频的DIV就是除。

2.倍频

举个例子:输入的是50MHz,也就是ref_clk是50MHz,要进行一个二倍频,输出的pll_out是100MHz,那么DIV就是2。因为要稳住输出的100MHz,所以FD/PD要等于0。

倍频的DIV就是乘。

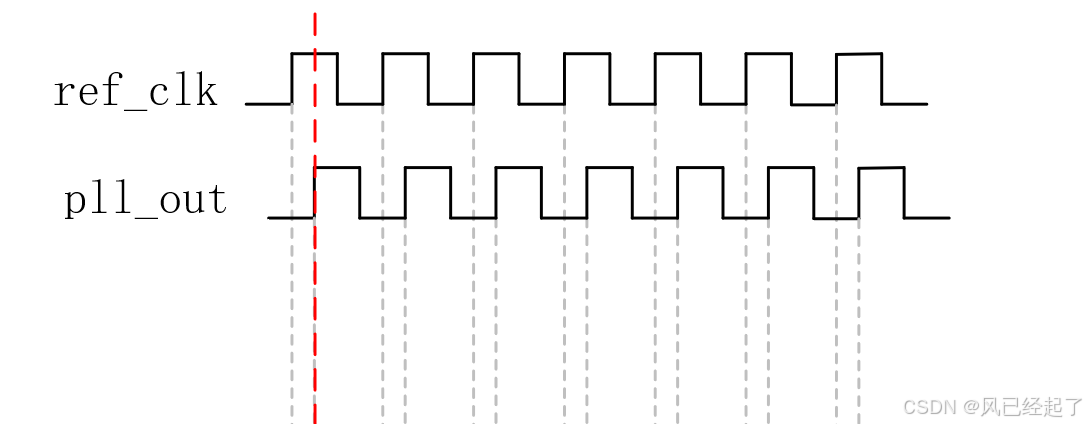

3.相位调整

相位调整可以从图形上直观的看出,相位是已经超前或者滞后了的。

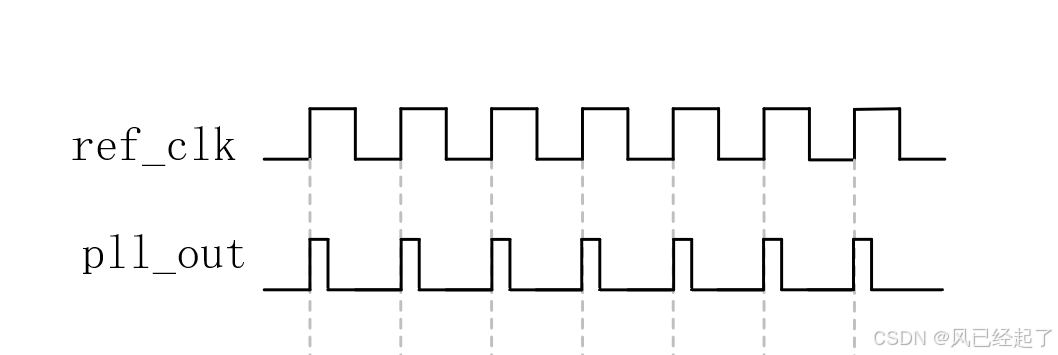

4.占空比调整

占空比调整可以直观的从图形上面看出来,占比是进行了一个调整的。

四、配置

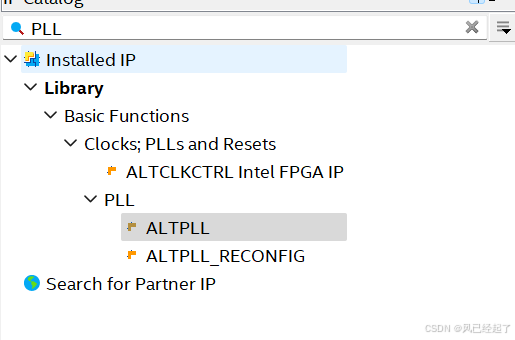

新版的在Tools里的IP Catalog,这个界面在右上角。

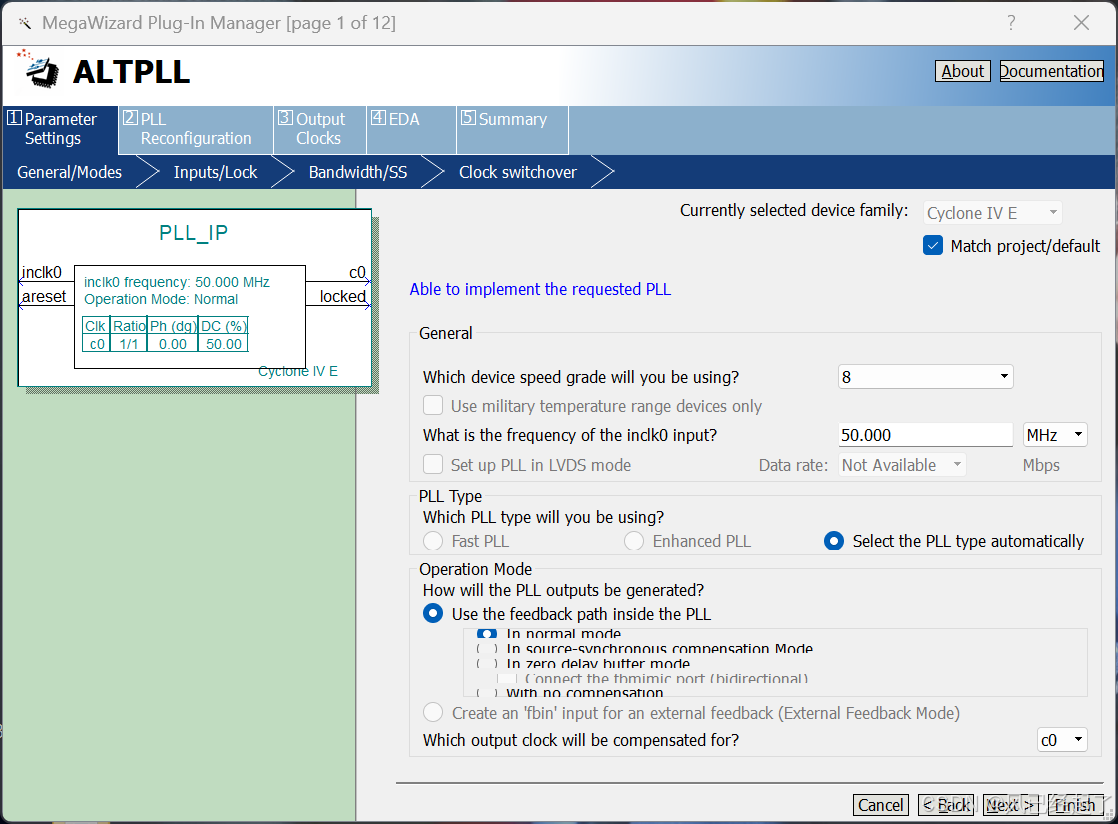

接下来就是选项了,这里选的标准模式的。

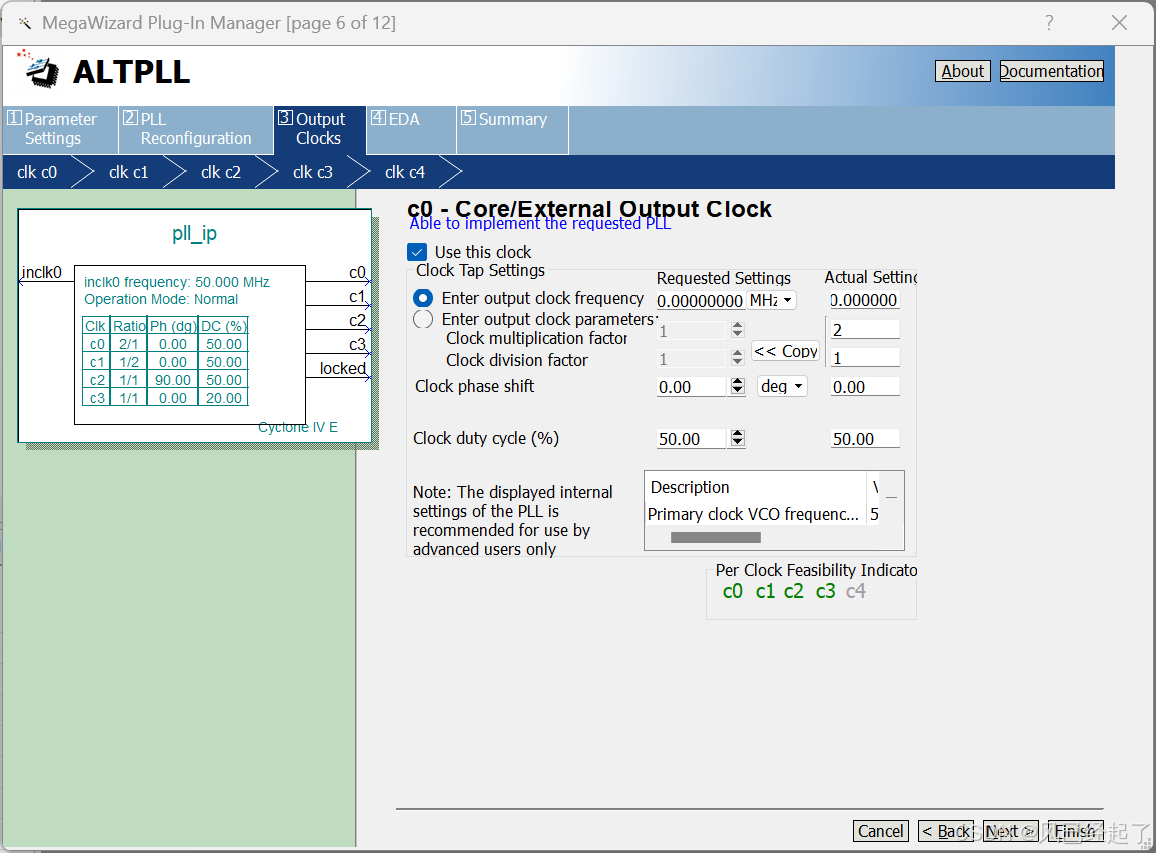

这里我配置的四个输出:clk0是二倍频

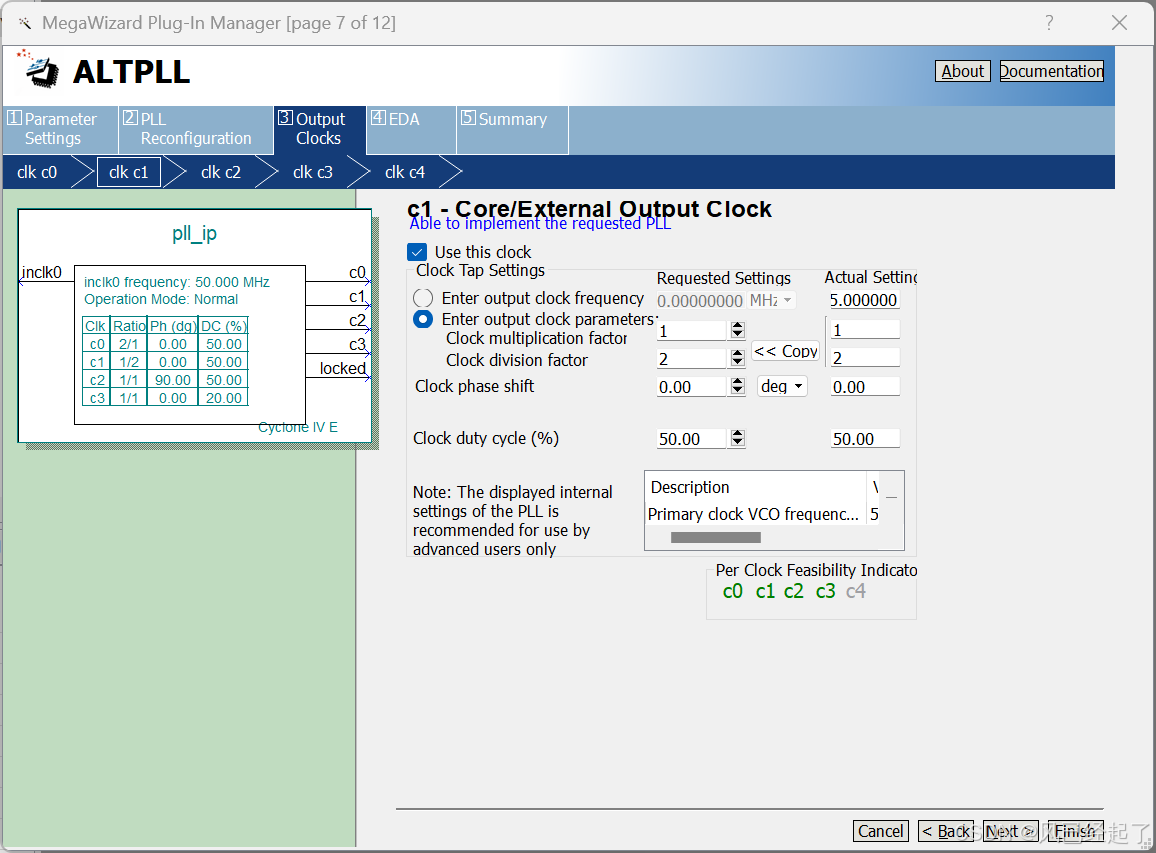

clk1是二分频

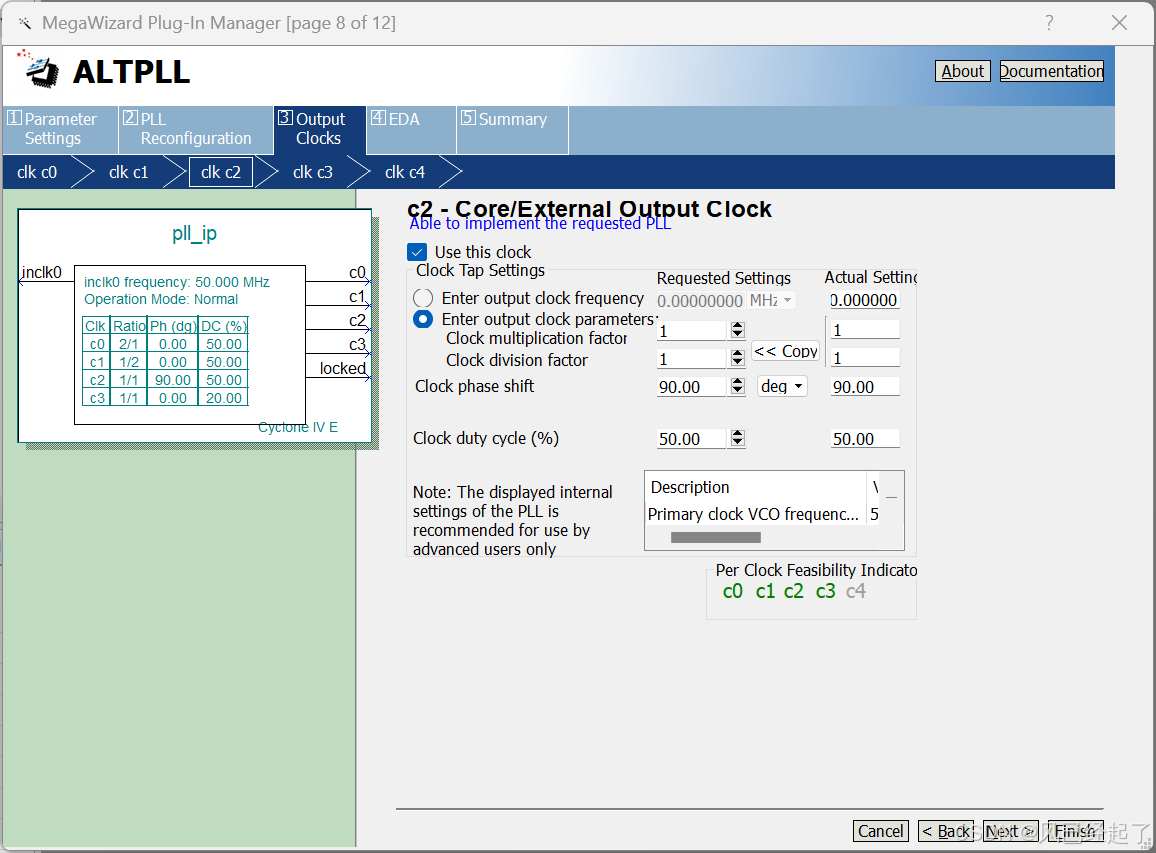

clk2是相位调整

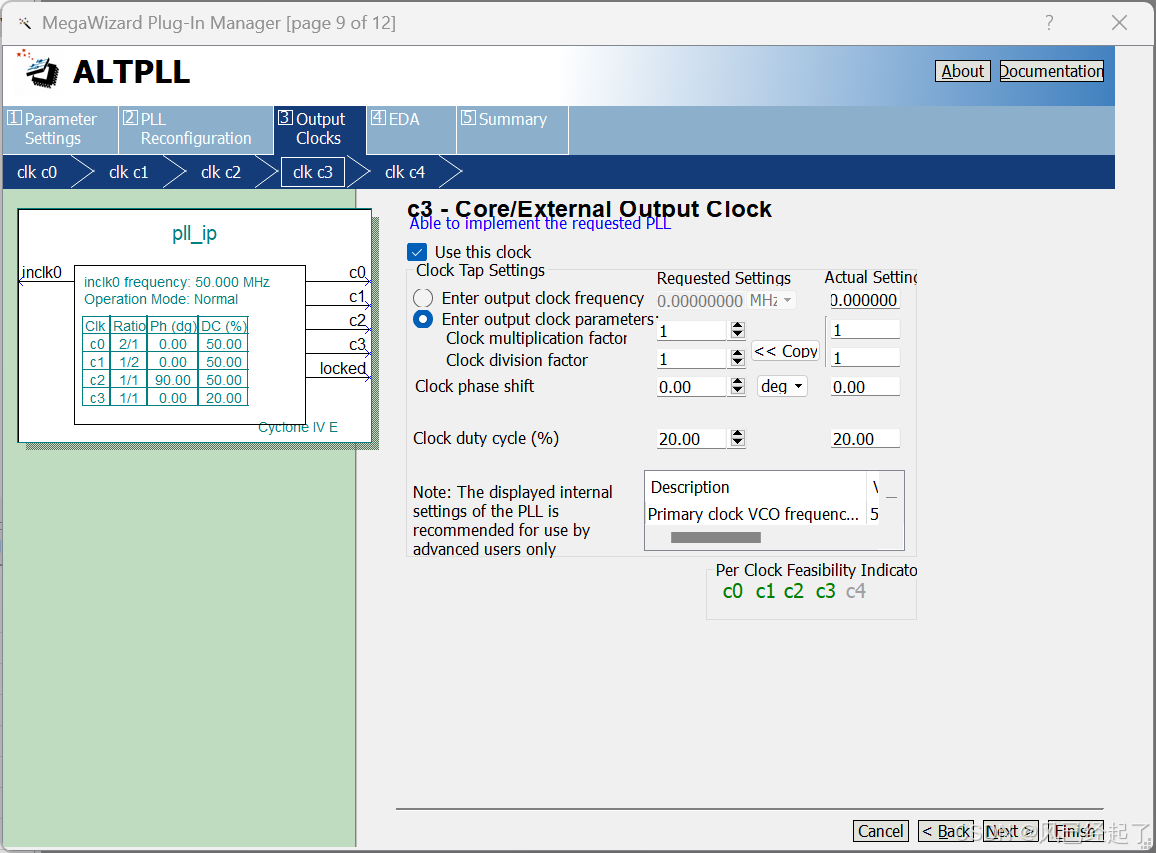

clk3是占空比调整

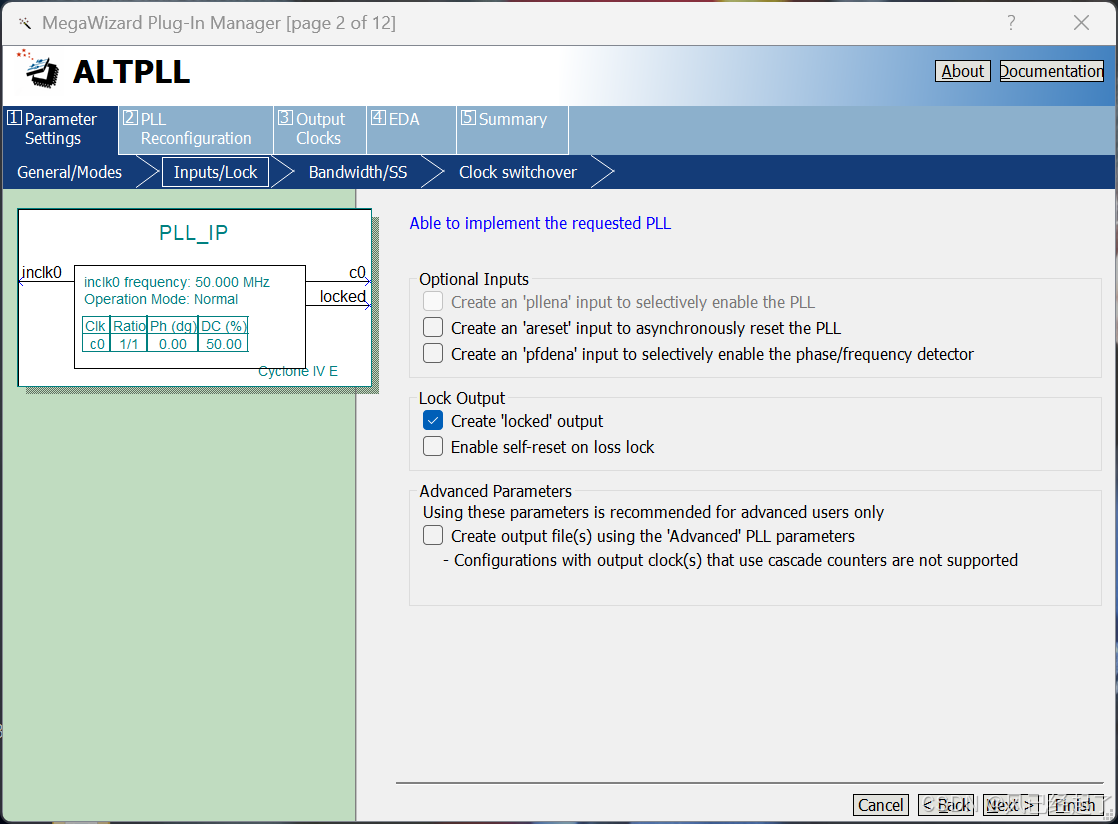

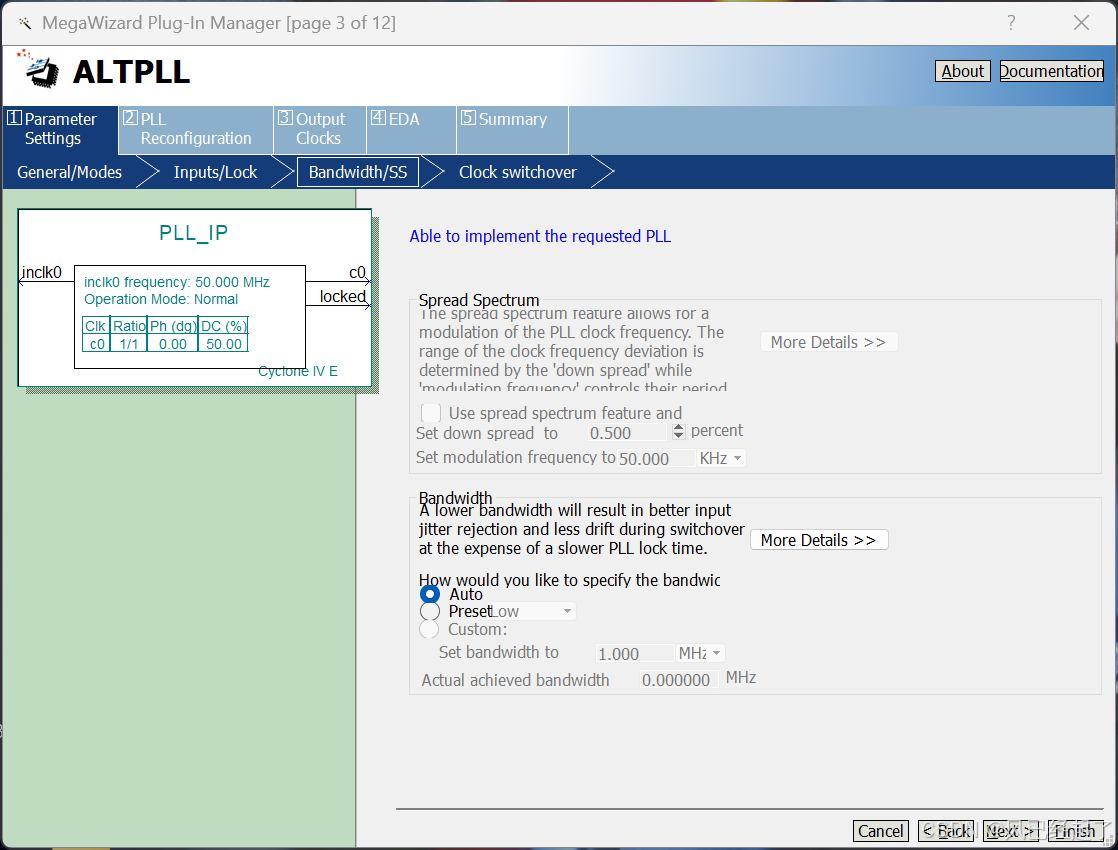

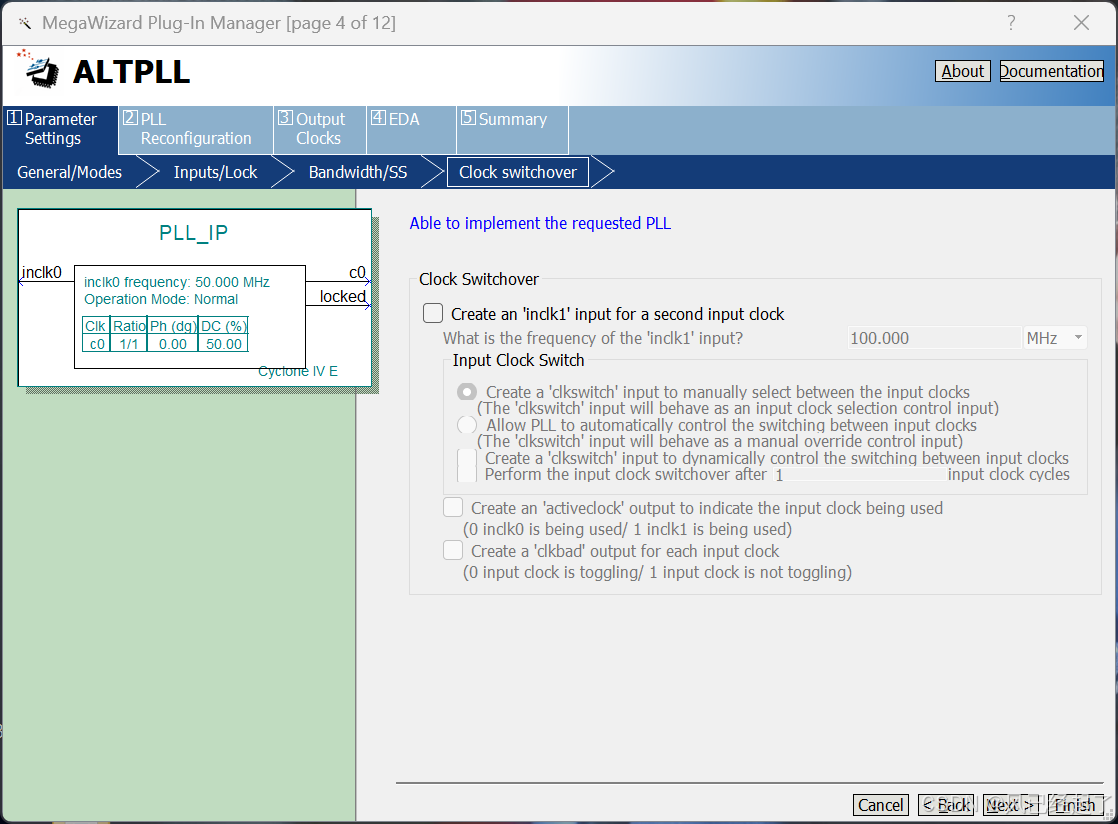

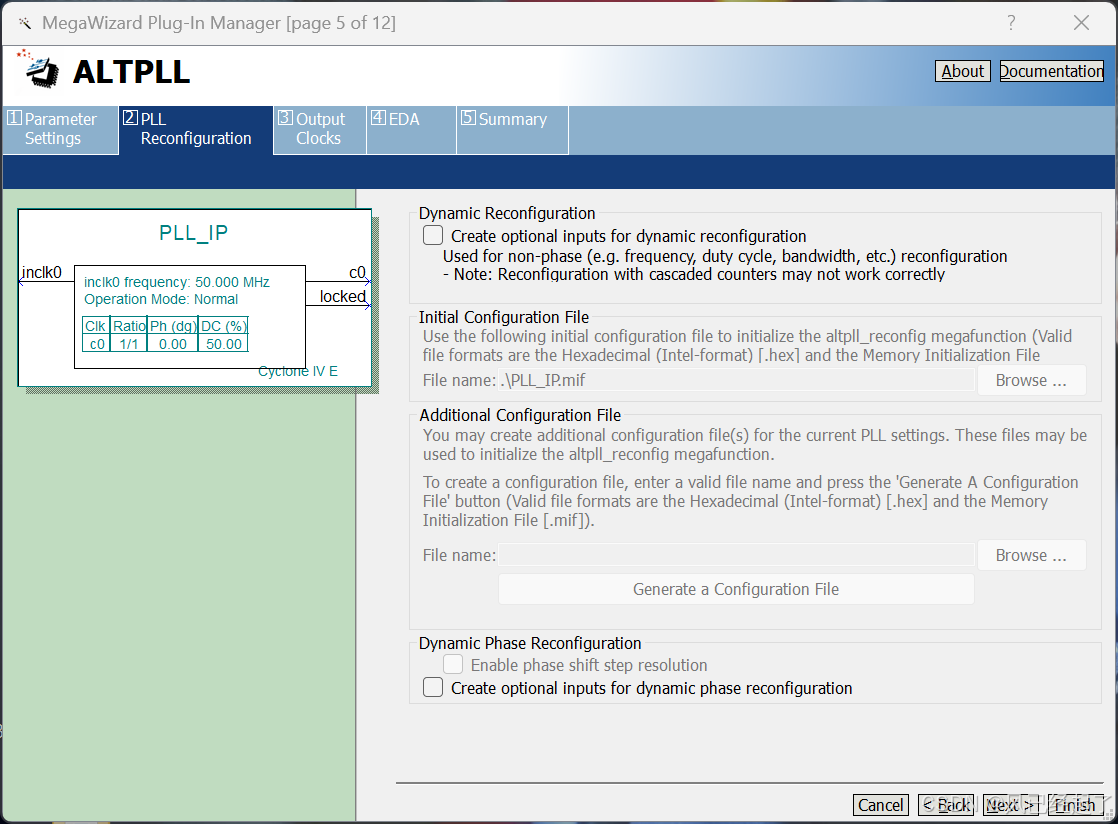

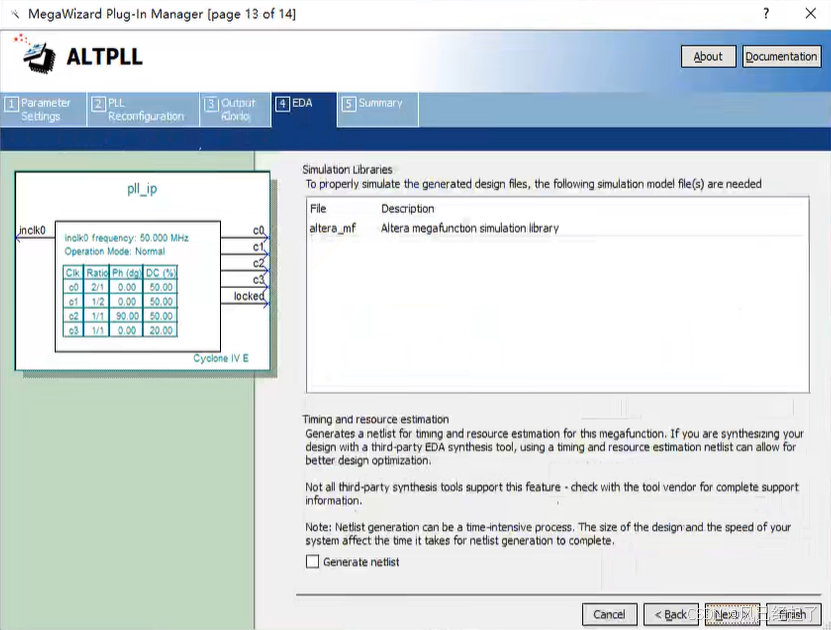

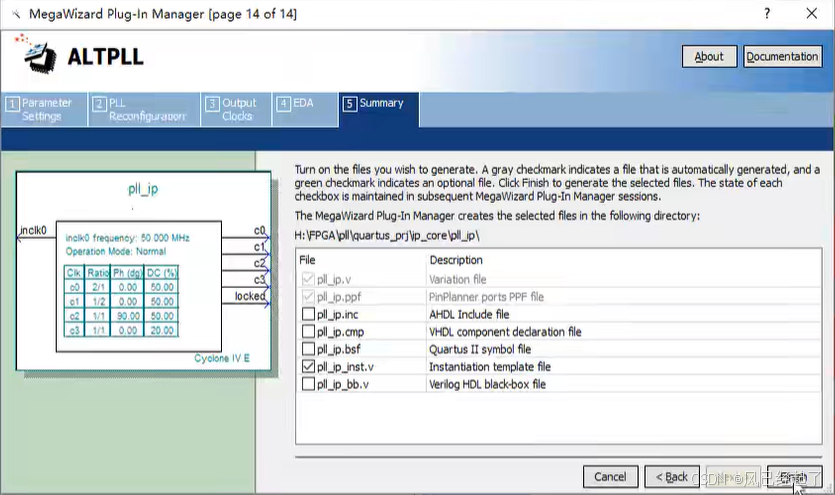

接下来是最后几步。

这样就配置完成了。

五、代码

module PLL

(

input wire sys_clk ,

output wire clk_mul_2 ,

output wire clk_div ,

output wire clk_pha_90 ,

output wire clk_duc_20 ,

output wire locked

);

pll_ip pll_ip_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div ),

.c2 ( clk_pha_90 ),

.c3 ( clk_duc_20 ),

.locked ( locked_sig )

);

endmodule到这里就是我学习PLL的所有笔记了,如果有不对的地方还请大家指出,谢谢。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?