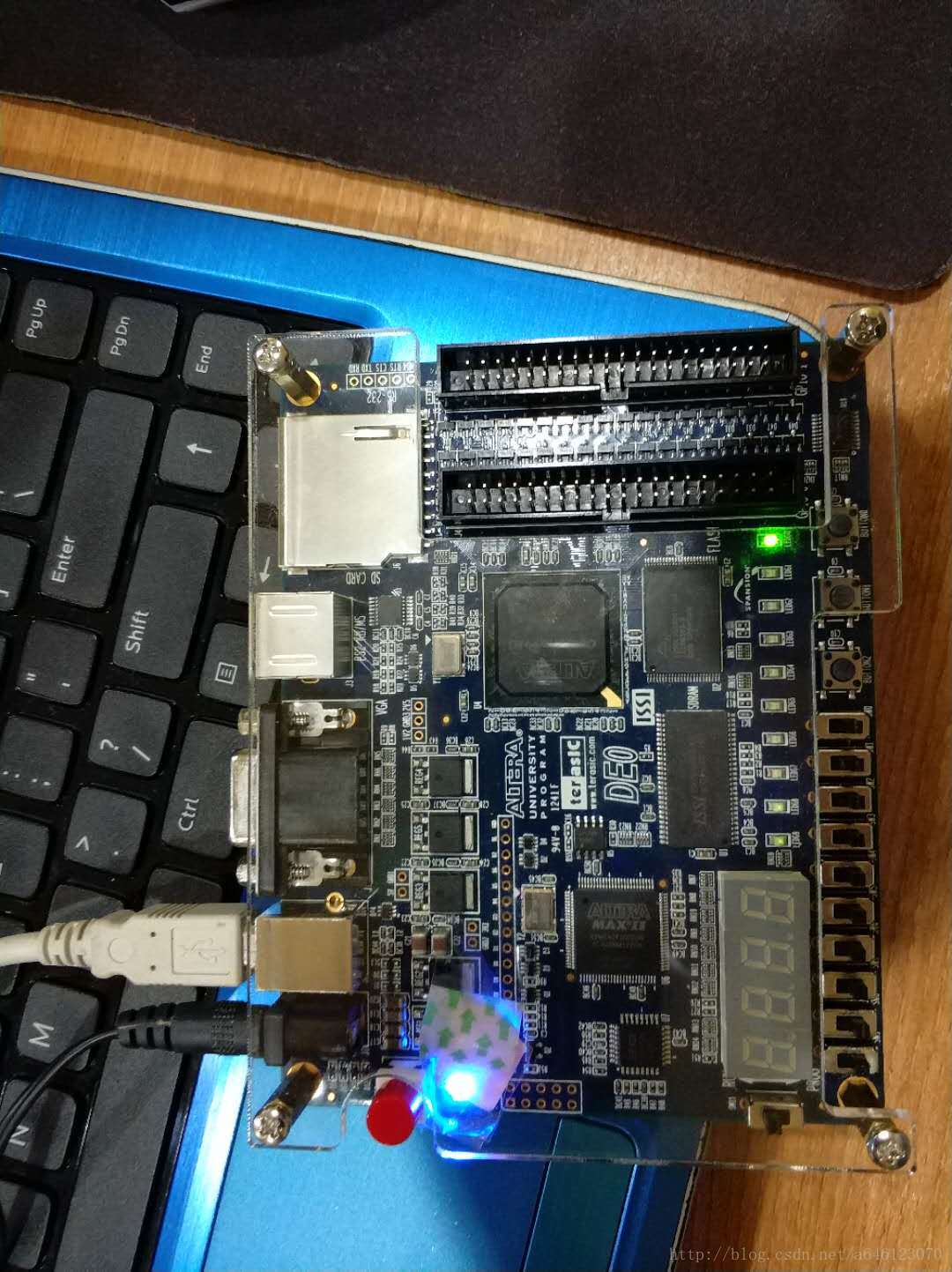

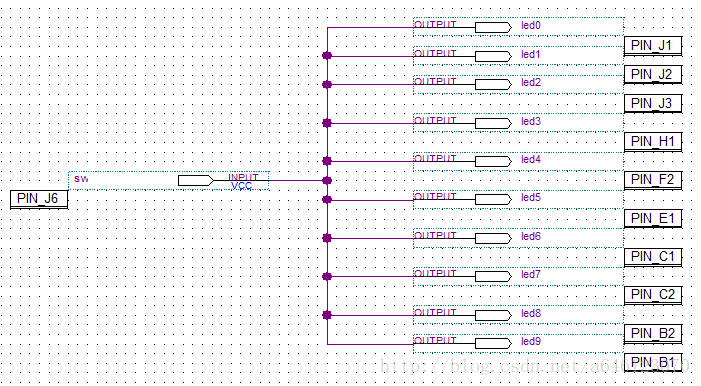

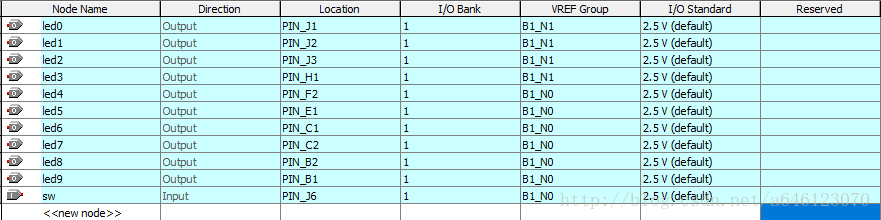

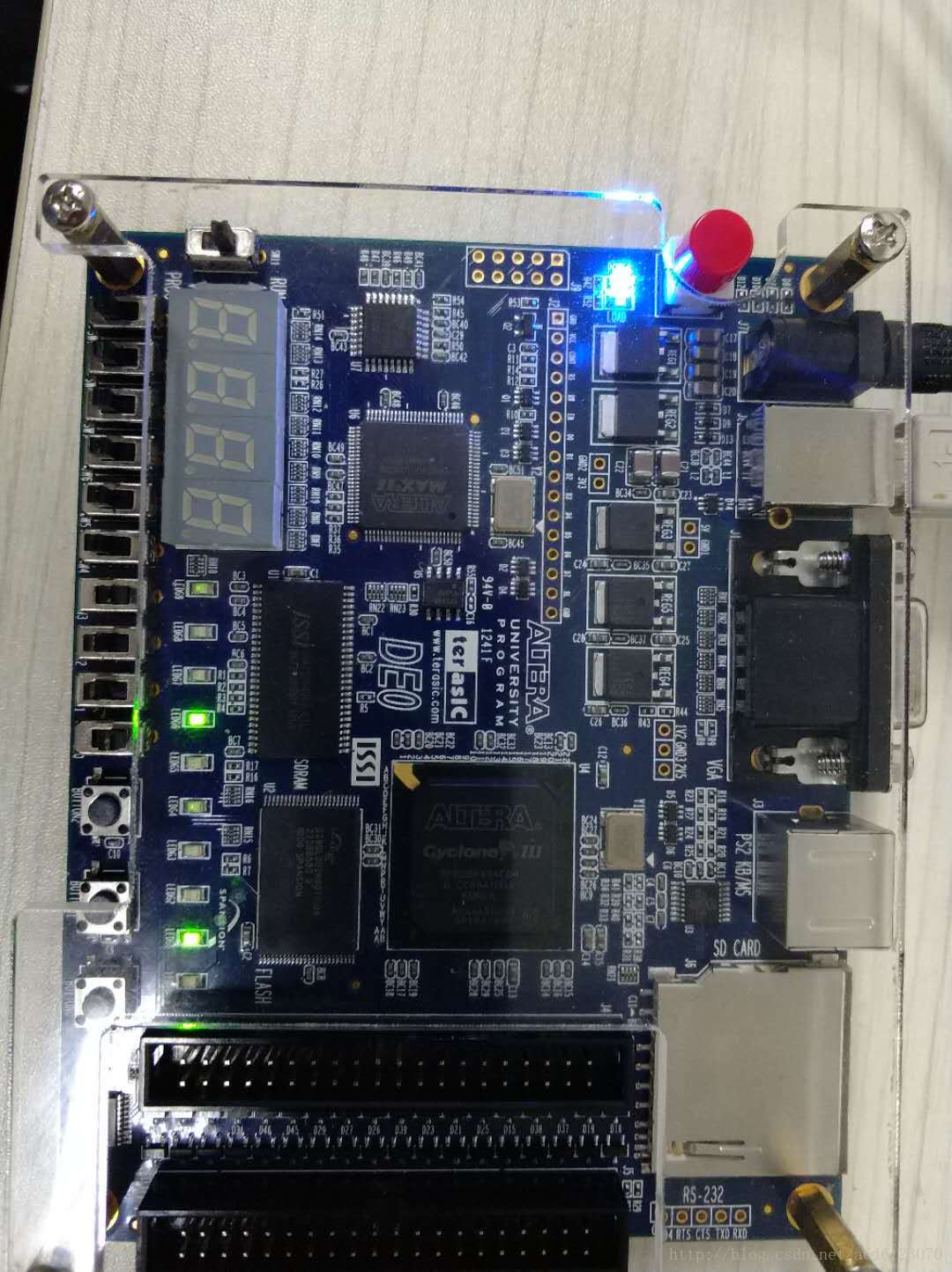

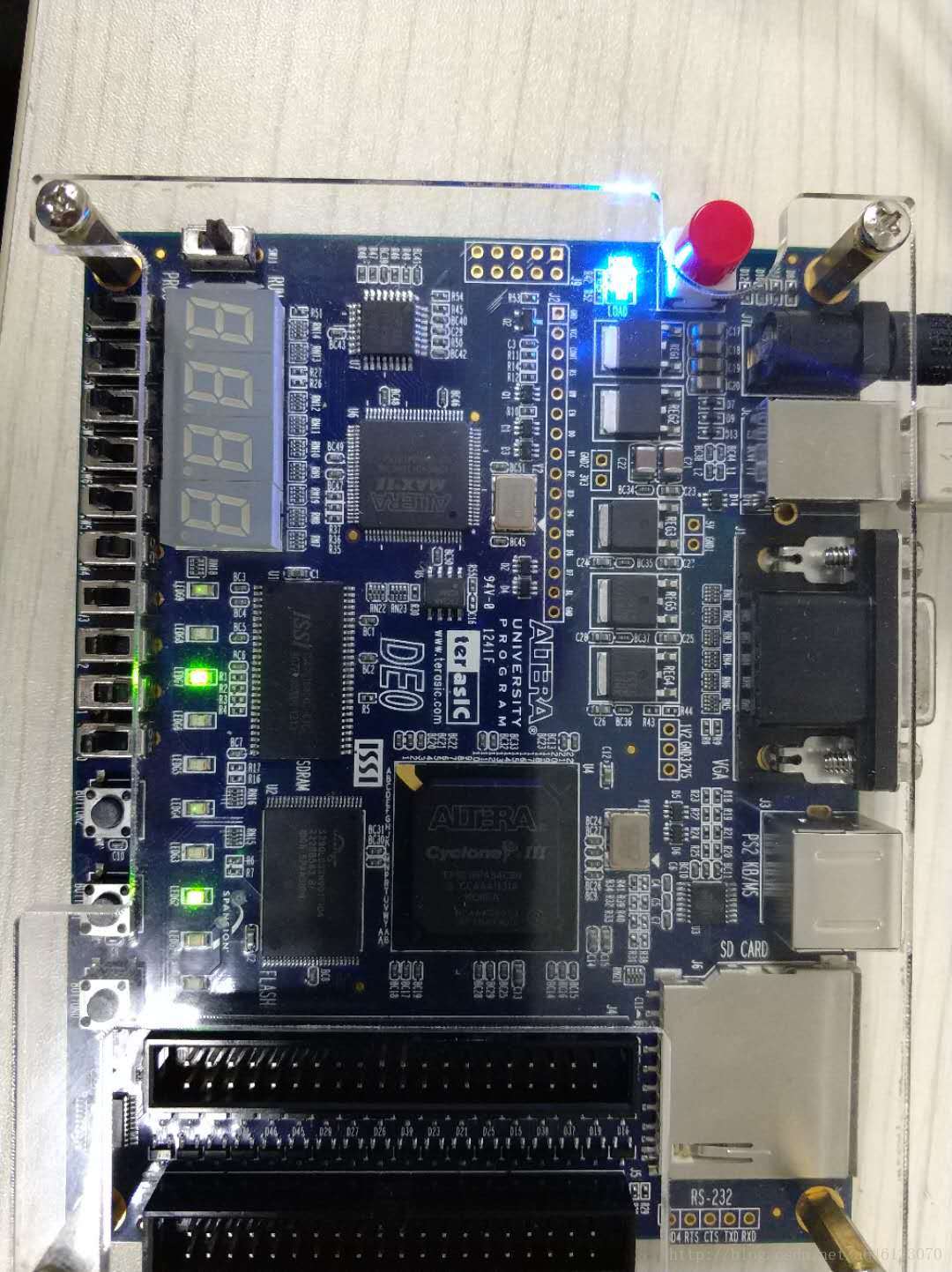

**实验一 用1个拨码开关控制所有的LED灯亮灭**

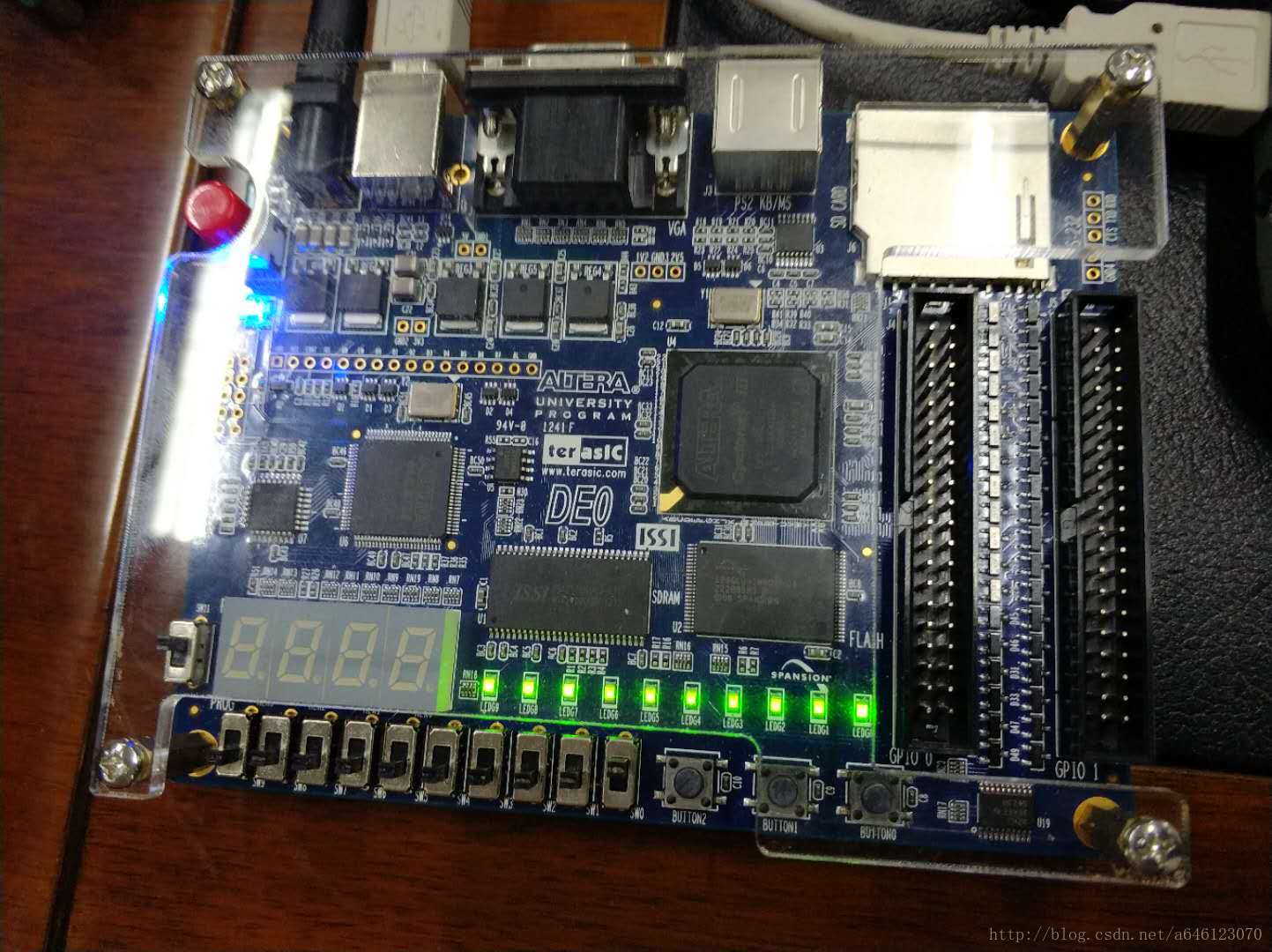

项目创建、编译和下载

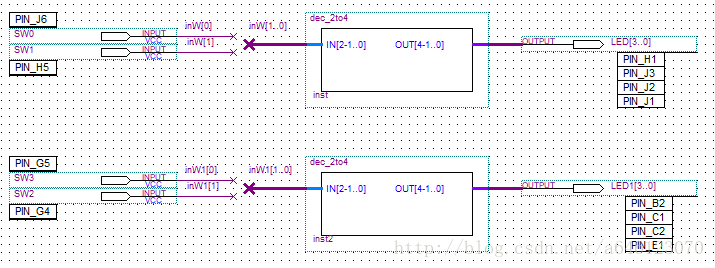

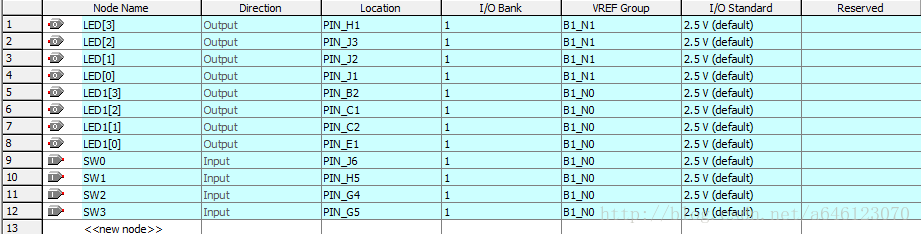

**实验二**

译码器组合逻辑

2-1 放置2个2-4译码器模块,则总共有2组SW, 每组2个,2组LED,每组4个,每组SW分别控 制其对应的LED组。

module dec_2to4(

IN ,

OUT);

input [2-1:0] IN ;

output [4-1:0] OUT ;

reg [4-1:0] OUT ;

always @ (IN) begin

case(IN)

2'b00: OUT = 4'b 0001;

2'b01: OUT = 4'b 0010;

2'b10: OUT = 4'b 0100;

2'b11: OUT = 4'b 1000;

endcase

end

endmodule // module dec_2to4;

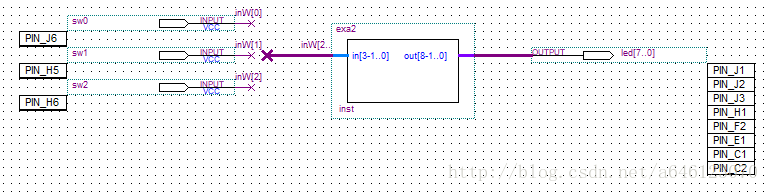

2-2 设计一个3-8译码器

module exa2(out,in);

output [8-1:0] out;

input [3-1:0] in;

reg [8-1:0] out;

always @(in)

begin

case(in)

3'd0: out=8'b00000001;

3'd1: out=8'b00000010;

3'd2: out=8'b00000100;

3'd3: out=8'b00001000;

3'd4: out=8'b00010000;

3'd5: out=8'b00100000;

3'd6: out=8'b01000000;

3'd7: out=8'b10000000;

endcase

end

endmodule

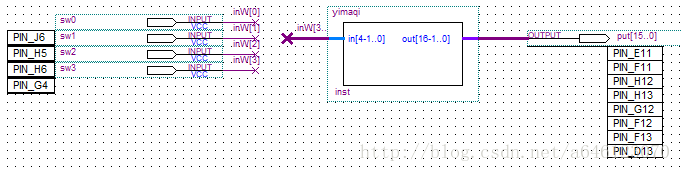

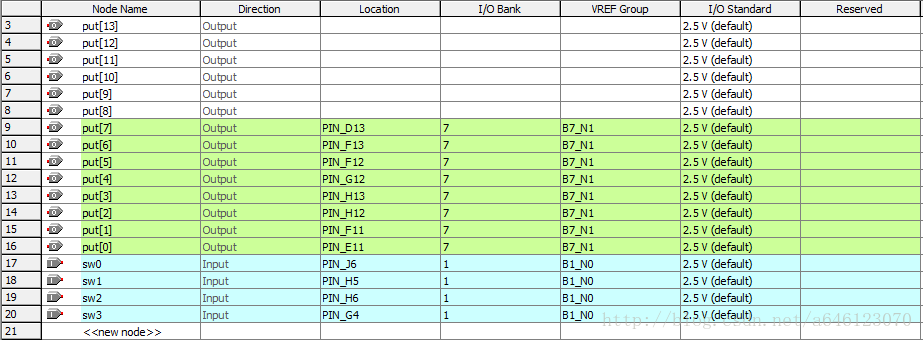

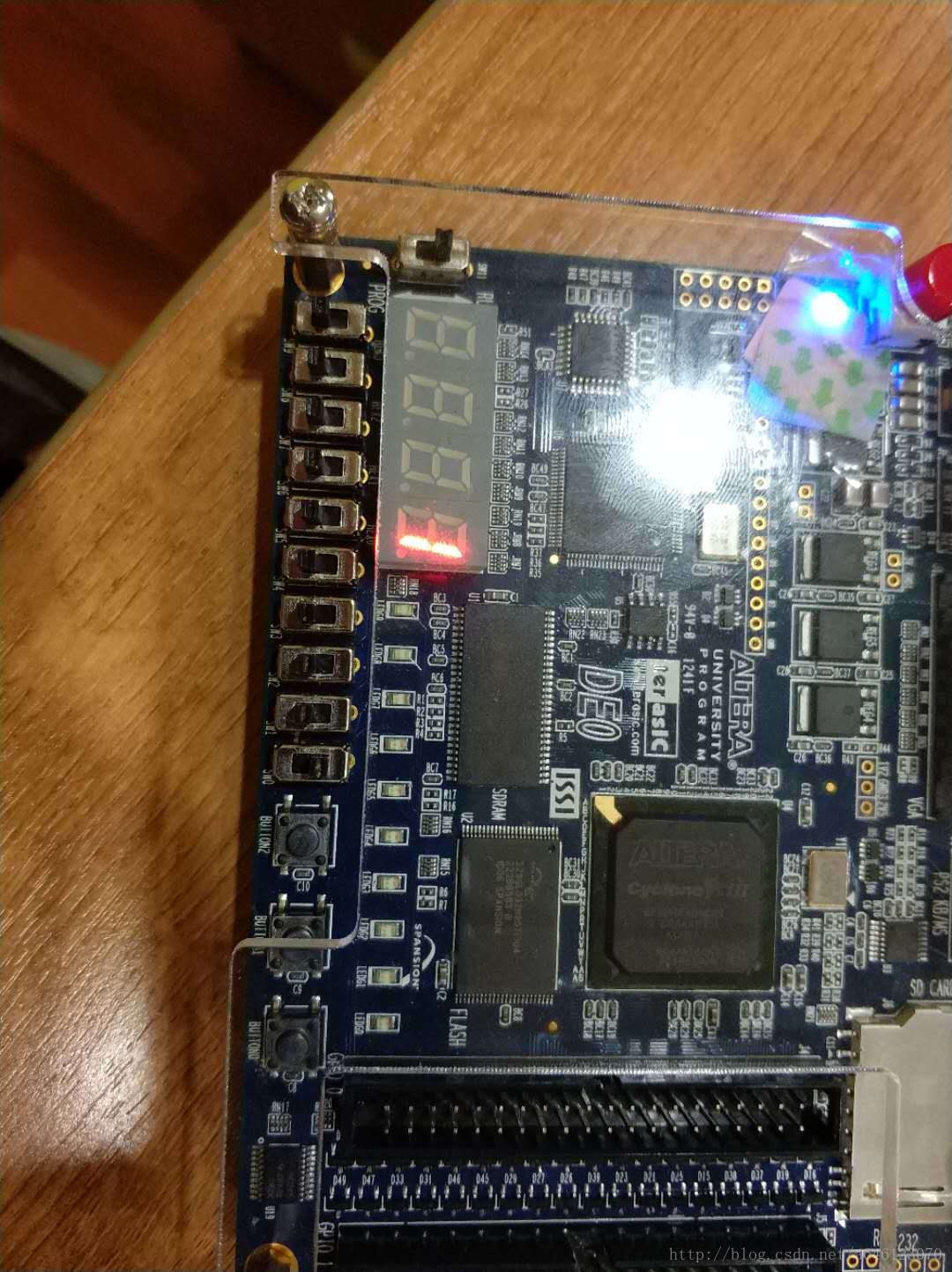

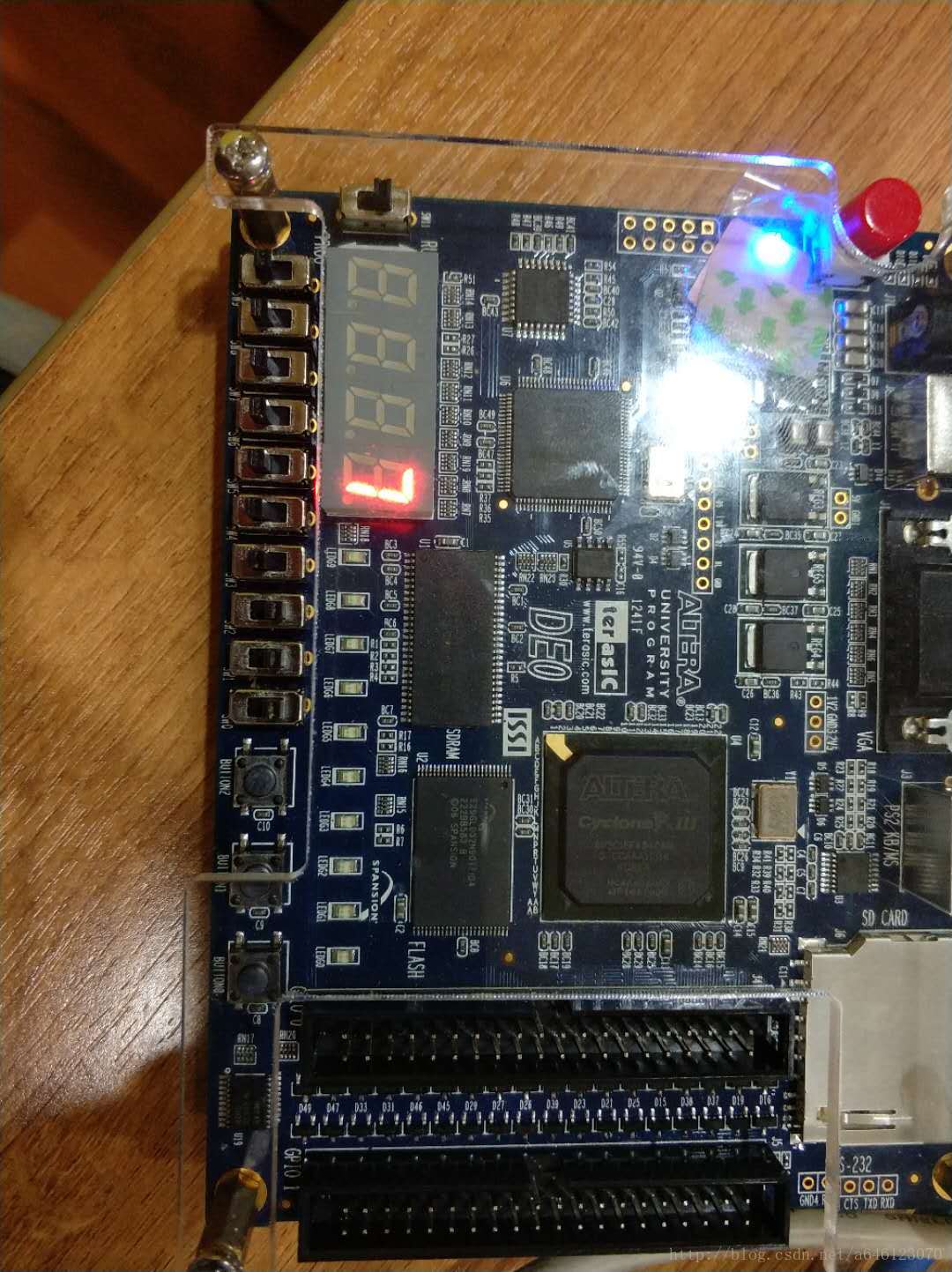

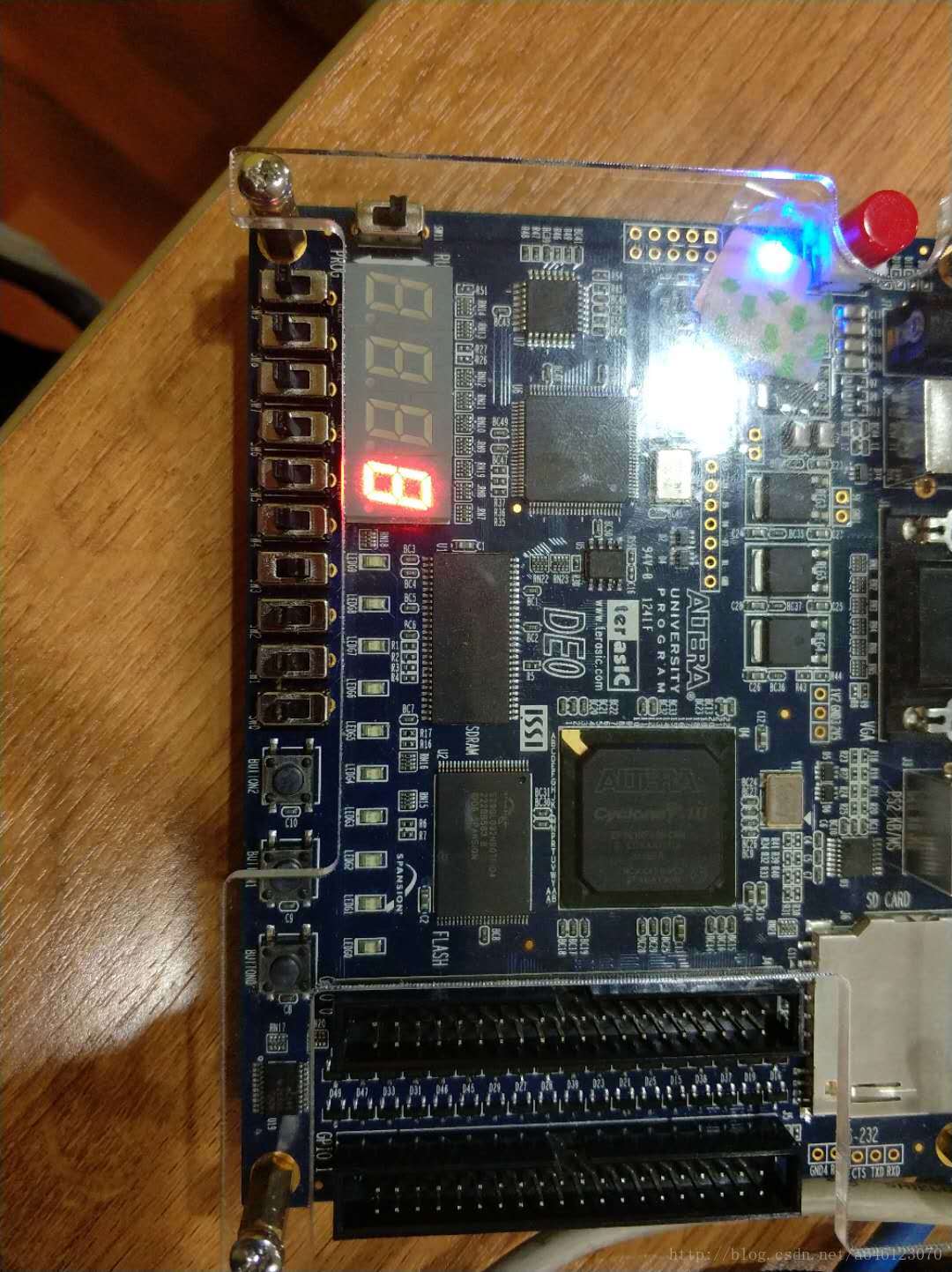

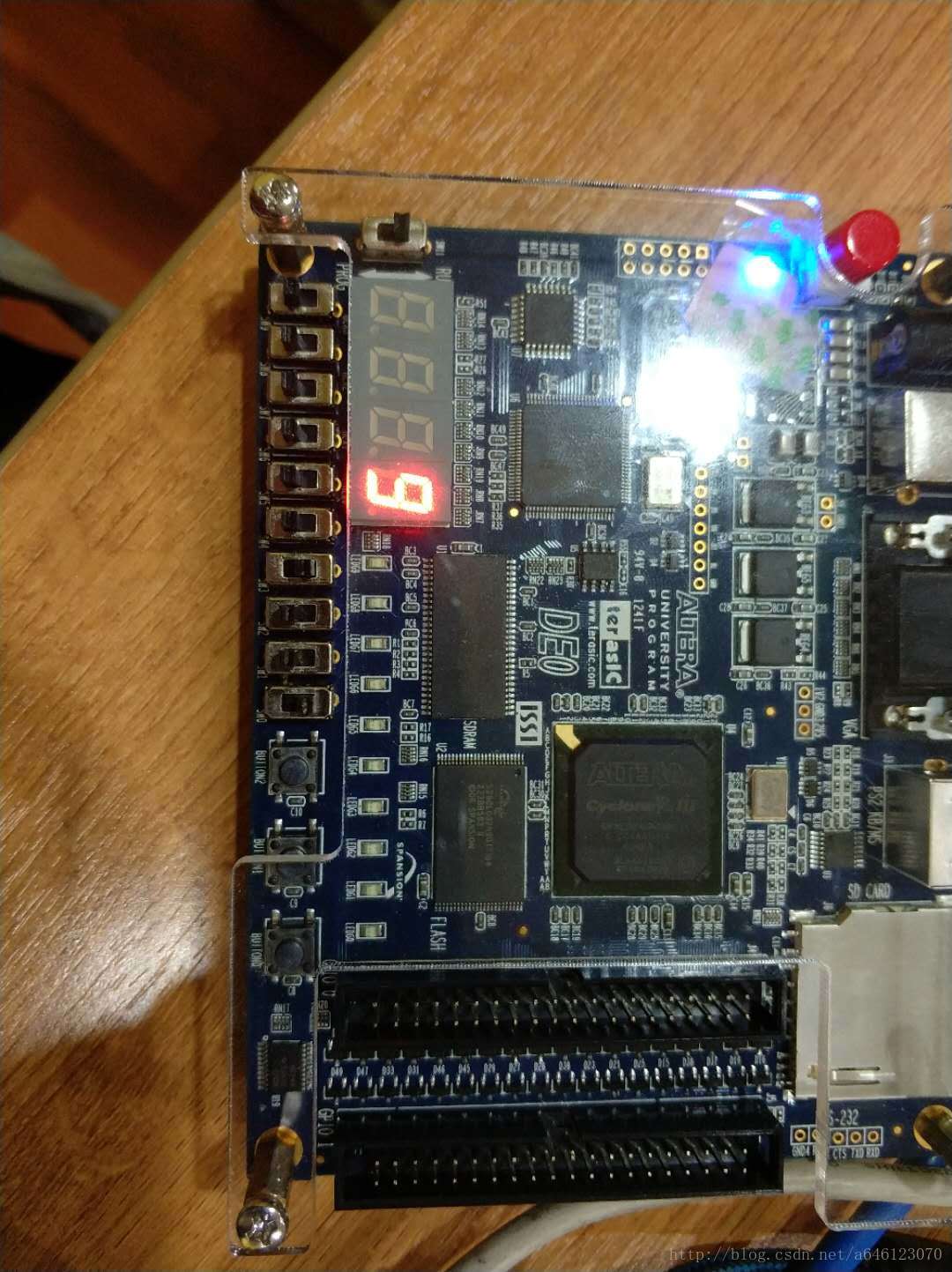

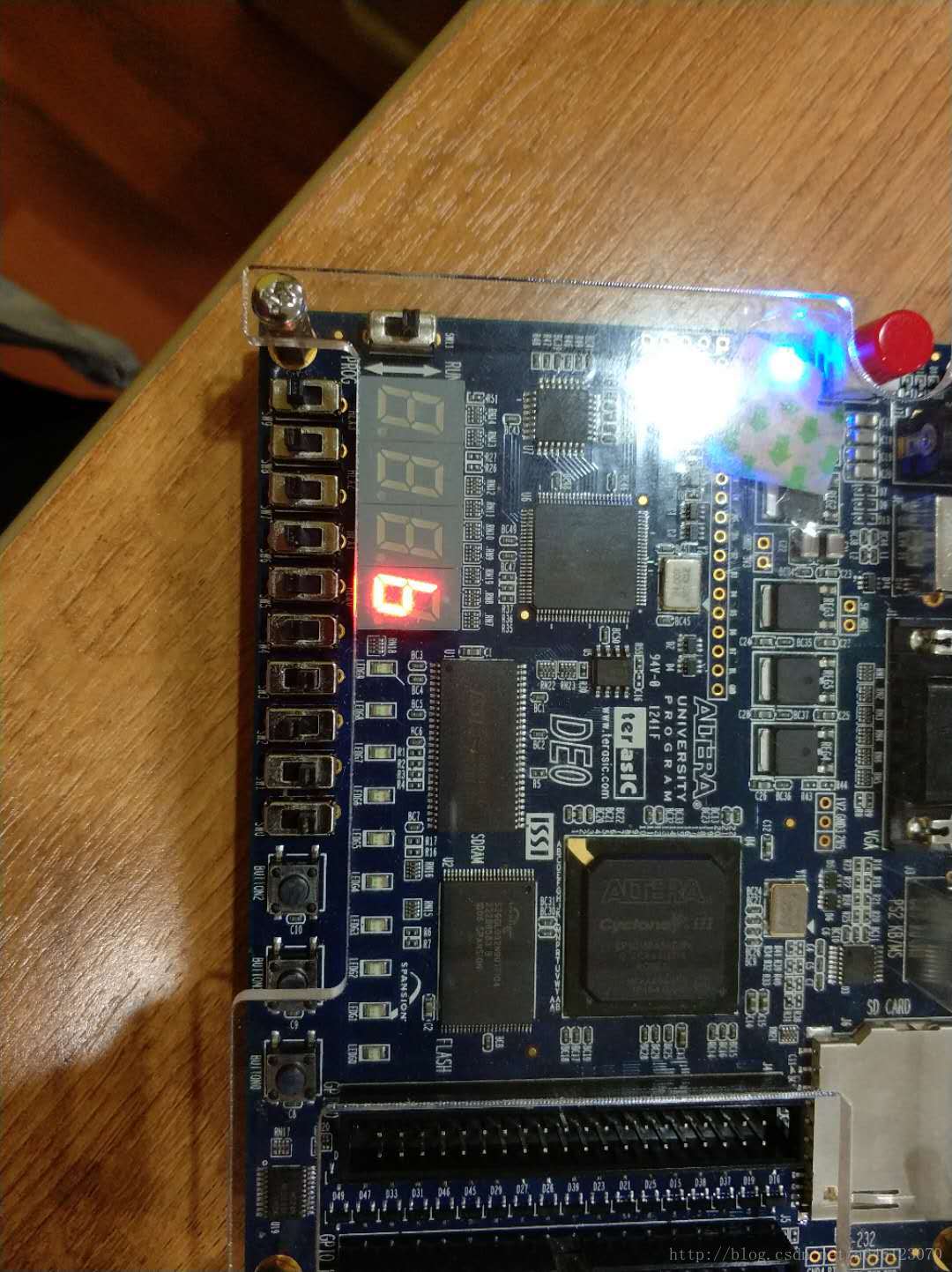

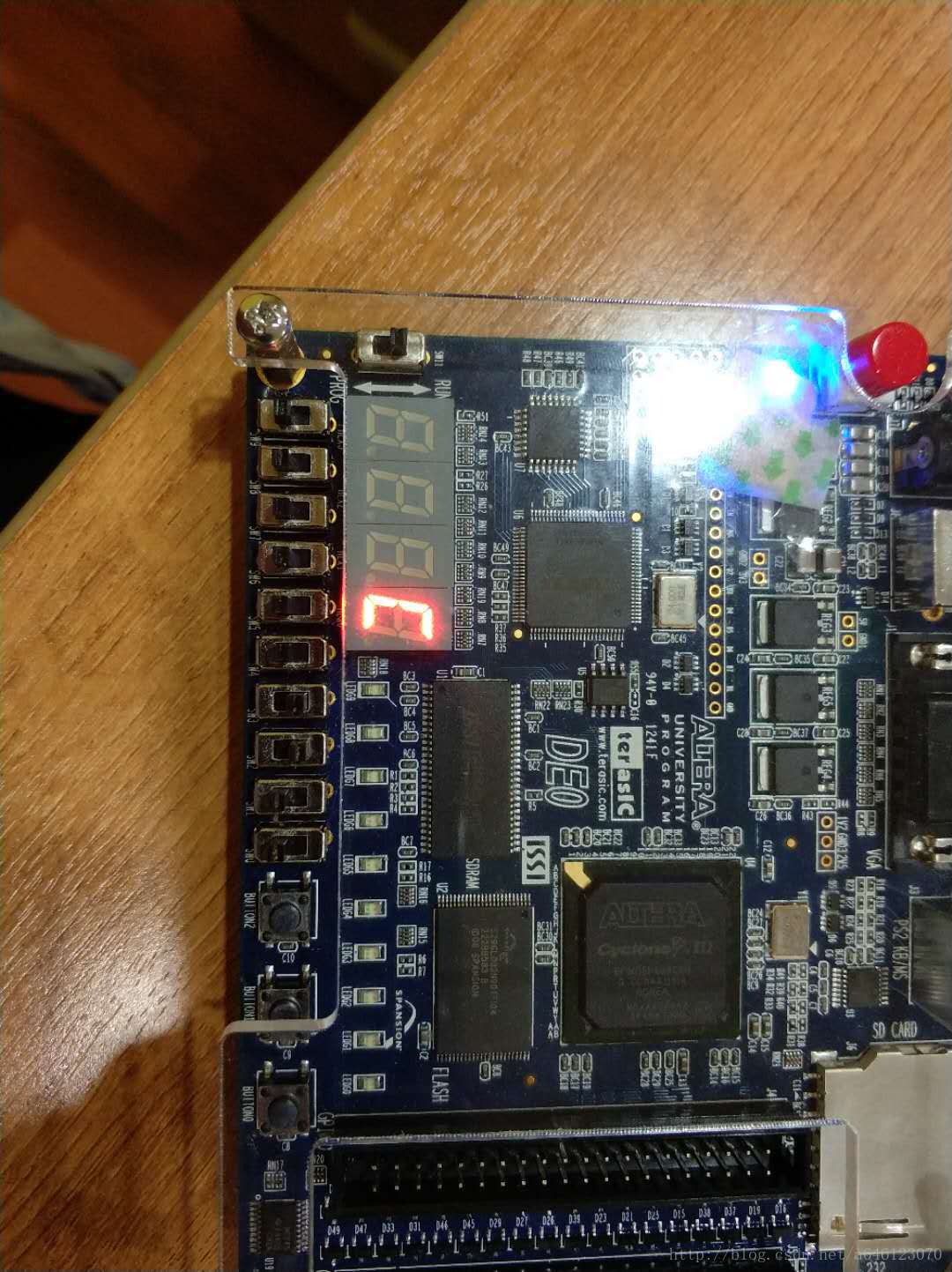

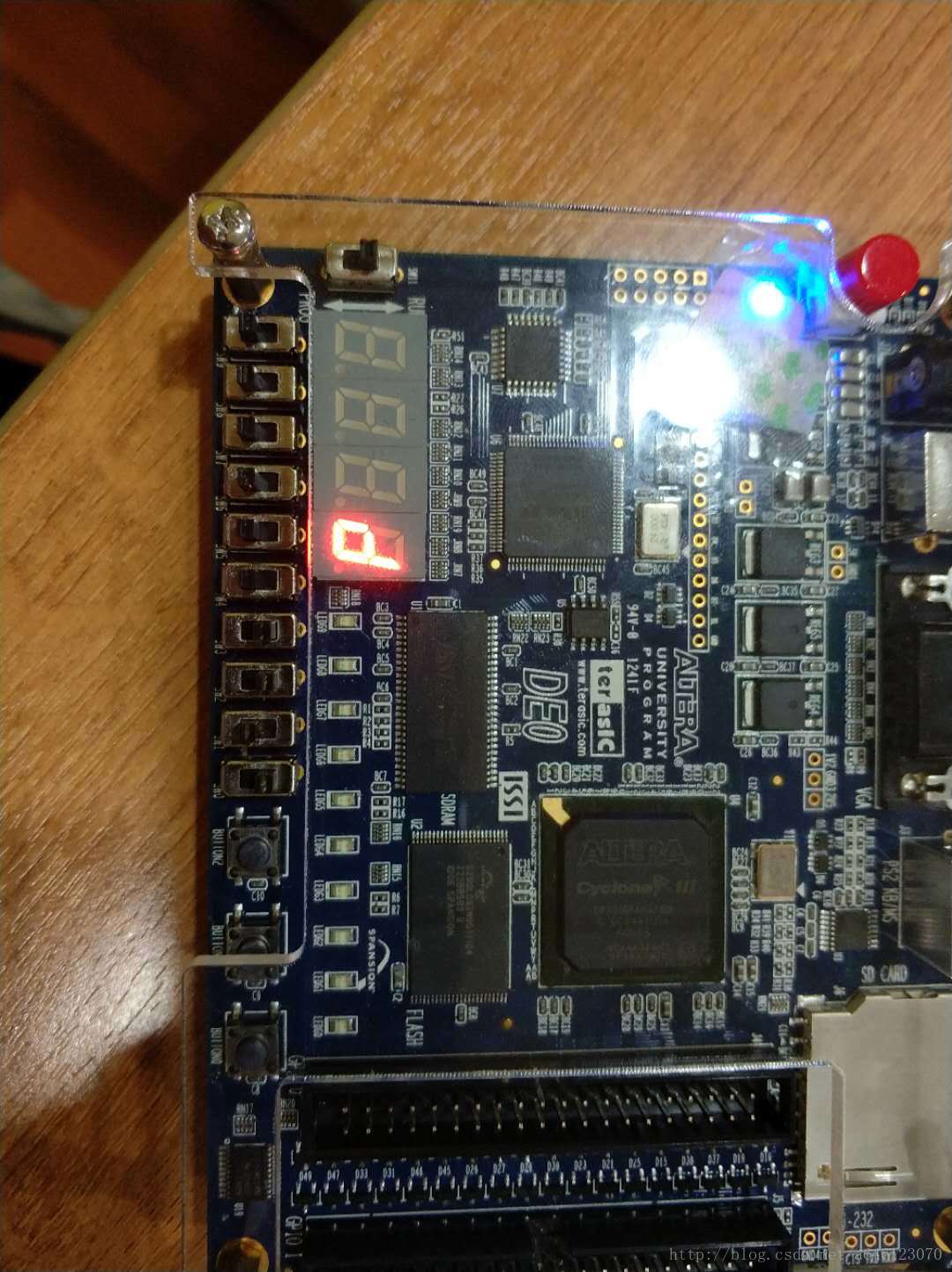

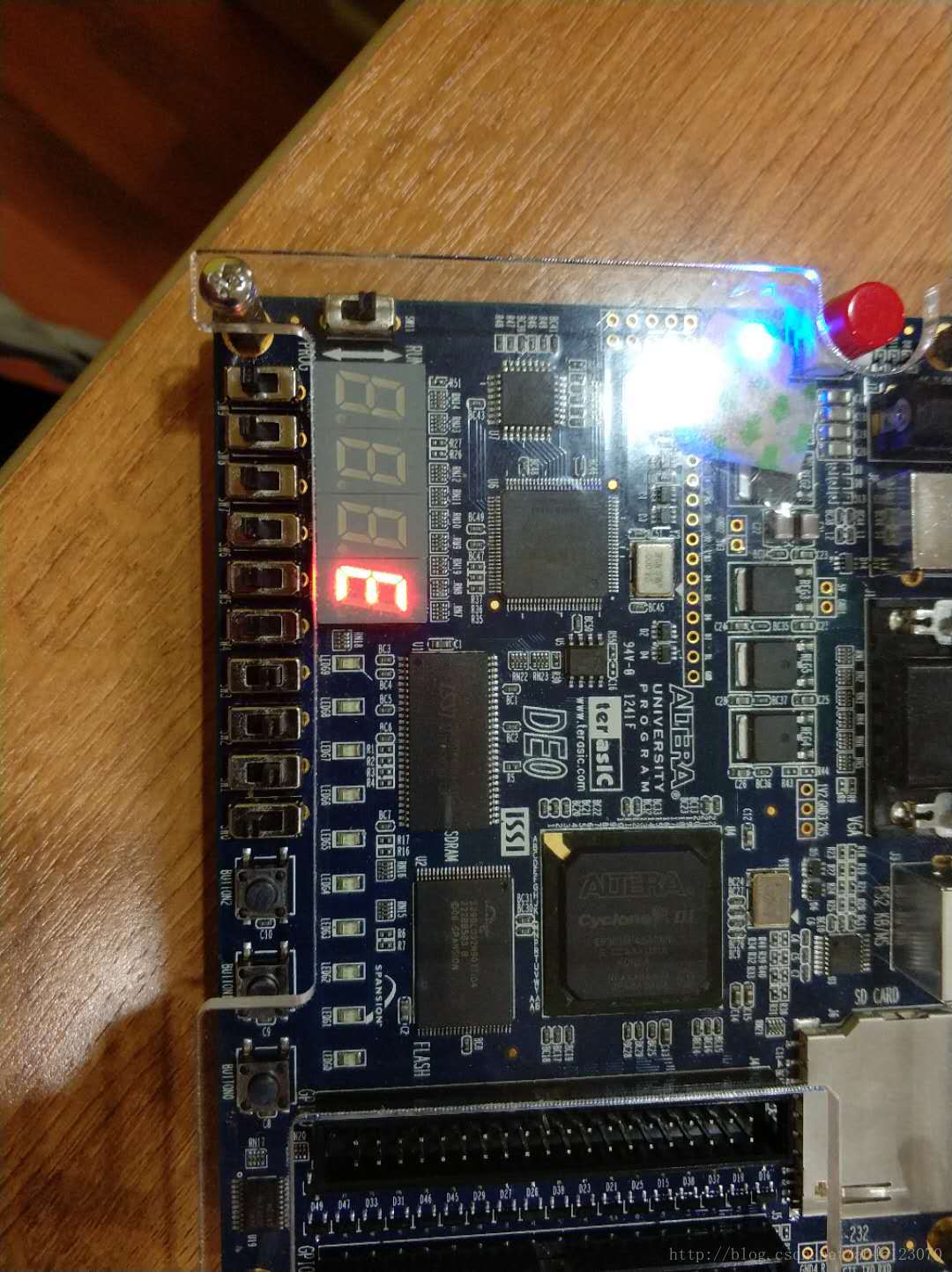

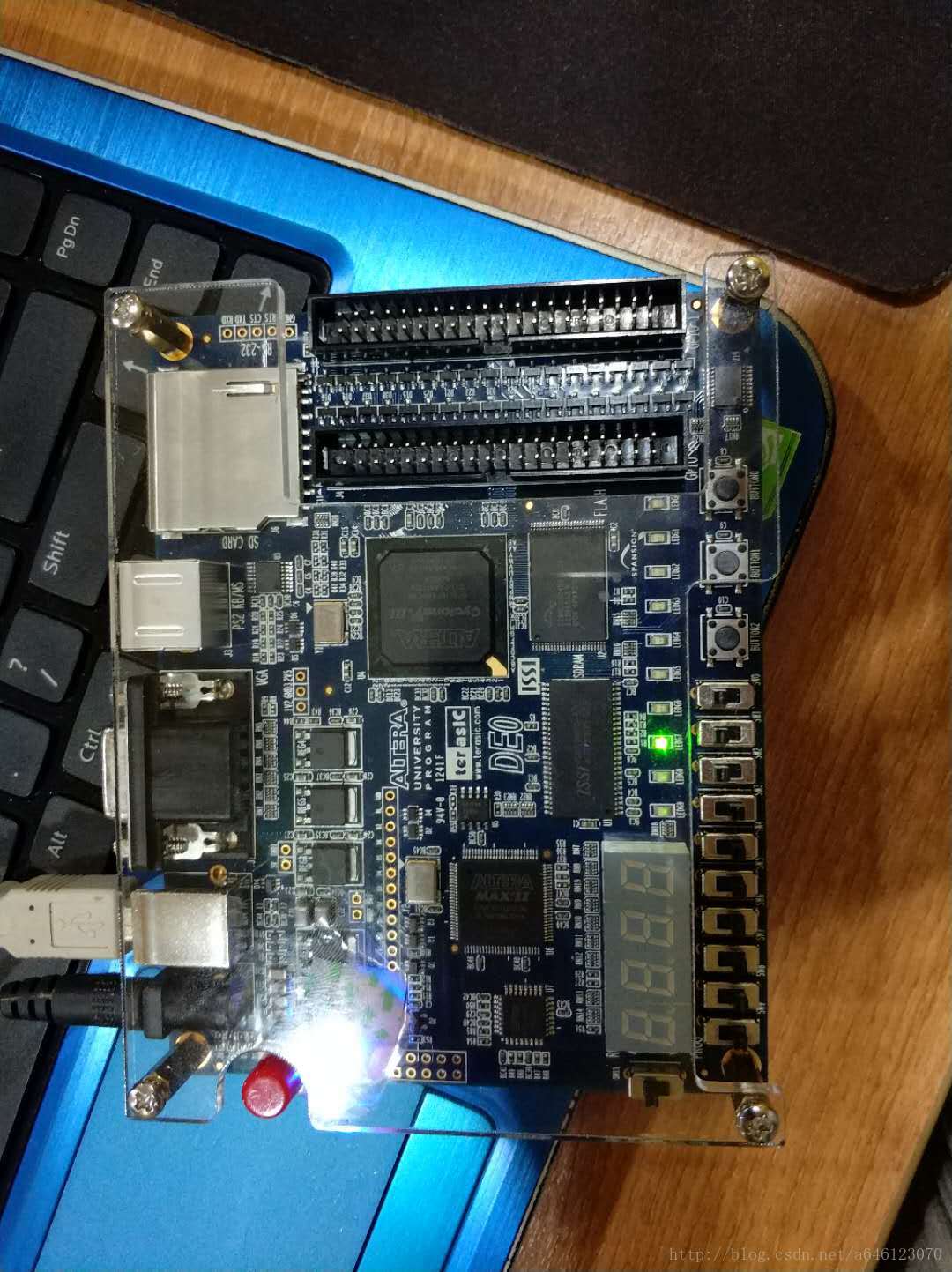

2-3 用4个拨码开关控制一个7段译码器的数字,从 0-9-A-F,共16个数字和字母

module yimaqi(out,in);

output [16-1:0] out;

input [4-1:0] in;

reg [16-1:0] out;

always @(in)

begin

case(in)

4'd0: out=16'b1111111111000000;

4'd1: out=16'b1111111111111001;

4'd2: out=16'b1111111110100100;

4'd3: out=16'b1111111110110000;

4'd4: out=16'b1111111110011001;

4'd5: out=16'b1111111110010010;

4'd6: out=16'b1111111110000010;

4'd7: out=16'b1111111111111000;

4'd8: out=16'b1111111110000000;

4'd9: out=16'b1111111110010000;

4'd10: out=16'b1111111110001000;

4'd11: out=16'b1111111110000011;

4'd12: out=16'b1111111111000110;

4'd13: out=16'b1111111110100001;

4'd14: out=16'b1111111110000110;

4'd15: out=16'b1111111110001110;

endcase

end

endmodule

实验三

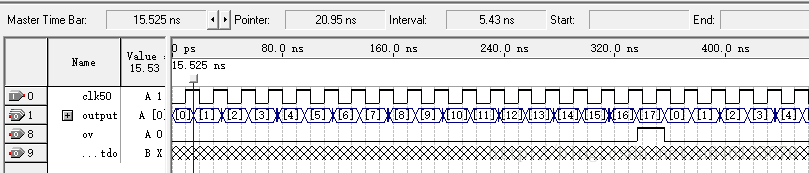

计数器、波形仿真、SignalTap

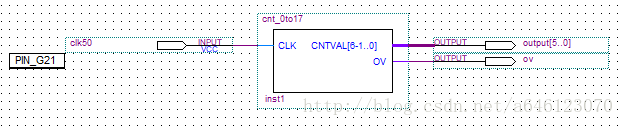

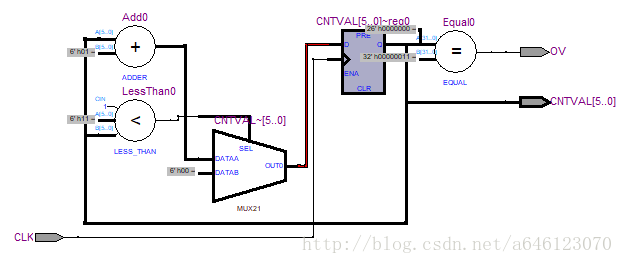

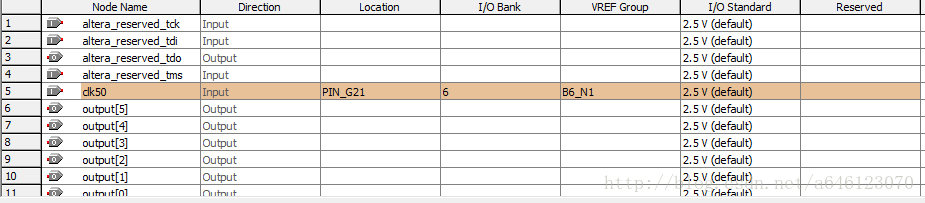

3-1 设计一个0-17的计数器,当计数值为17的时,OV输出1,其他输出0

module cnt_0to17(

CLK , // clock

CNTVAL, // counter value

OV ); // overflow

input CLK;

output [6-1:0] CNTVAL;

output OV;

reg [6-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL >= 17)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

always @ (CNTVAL) begin

if(CNTVAL == 17)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule // module cnt_0to17

本文介绍了FPGA电路开发的基础实验,包括2-4译码器、3-8译码器的设计,以及不同类型的计数器实现。通过实验3-1和3-2,设计了0-17计数器并讨论了高速时钟下的现象。在实验4中,构建了时间基准电路和移位寄存器。实验6探讨了计数器、ROM和DDS,解析了正弦波频率与计数器增量值的关系,并提出了降低频率的方法。

本文介绍了FPGA电路开发的基础实验,包括2-4译码器、3-8译码器的设计,以及不同类型的计数器实现。通过实验3-1和3-2,设计了0-17计数器并讨论了高速时钟下的现象。在实验4中,构建了时间基准电路和移位寄存器。实验6探讨了计数器、ROM和DDS,解析了正弦波频率与计数器增量值的关系,并提出了降低频率的方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?