本文介绍瑞萨RH850/F1L用户手册(user manual)的CAN接口部分的中文翻译。

博主会持续更新该用户手册,直到整个翻译完成,有兴趣的朋友可持续关注.

版权声明

email:1256153255@qq.com

website for get 瑞萨RH850F1x开发板和瑞萨E1仿真器

Section 6 Exceptions/Interrupts(异常/中断)

6.1 Features

响应事件从当前运行的程序切换到不同程序的行为称为异常。此微控制器支持以下类型的异常。

有关异常的详细信息,请参见RH850G3K User’s Manual: Software.

(1) Interrupts

Table 6.1中的以下三种例外情况称为中断,本节对此进行了描述。

◆ FE level non-maskable interrupt (FENMI)

即使生成了另一个FE级中断-FEINT,也会确认FENMI中断。

–即使CPU系统寄存器PSW.NP=1,也会确认FENMI中断。

–从FENMI中断返回是不可能的,恢复也是不可能的。

◆ FE级可屏蔽中断(FEINT)

–如果CPU系统寄存器PSW.NP=0,FEINT作可以被确认。如果PSW.NP=1,FEINT 作被屏蔽。

–从FEINT中断中恢复是可能的,恢复也是可能的。

◆ EI级可屏蔽中断(EIINT)

如果没有生成FE级中断(FENMI或FEINT),则可以确认EIINT中断。

–如果CPU系统寄存器PSW.NP=0,则可以确认EIINT。

如果PSW.NP=1,正在处理具有更高优先级的EIINT,或PSW.ID=1,则屏蔽它。

–从EIINT中断返回是可能的,恢复也是可能的。

–可以为每个中断通道指定中断屏蔽。

–可以为每个中断通道指定8个中断优先级。

–在本节中,与中断通道n对应的EIINT用“INTn”表示,而与中断源xxx对应的EIINT用“INTxxx”表示。

有关PSW寄存器,请参阅Section 3.3.2.5, PSW — Program Status Word 和RH850G3K User’s Manual: Software。

NOTE:

Return(返回):表示程序是否可以从中断的地方恢复。

Recovery(恢复):指示处理器状态(处理器资源的状态,包括通用寄存器和系统寄存器)是否可以恢复到程序中断时的状态。

这些中断源将在以下几页中描述。

6.2 RH850/F1L Interrupt Sources

6.2.1 Interrupt Sources

6.2.1.1 FE Level Non-Maskable Interrupts

(1) Priority

See Table 6.1, List of Exception Sources.

(2) Return PC

Return or recovery from an FE non-maskable interrupt is not possible.

(3) Status Register

See Section 6.4.3, FNC — FE Level NMI Status Register.

(4) Return Instruction

None

FENMI中断源可以通过一个专用的标志寄存器来评估。有关详细信息,请参阅Section 6.2.2,

FE Level Non-Maskable Interrupt Sources 。

6.2.1.2 FE Level Maskable Interrupts

(1) Priority

See Table 6.1, List of Exception Sources.

(2) Return PC

The return PC returned from an interrupt handling routine by the FERET instruction is the PC from

when the program was suspended (current PC).

(3) Status Register

See Section 6.4.4, FIC — FE Level Maskable Interrupt Status Register.

(4) Return Instruction

FERET

Note 1:See Table 6.1, List of Exception Sources.

Note 2:256 KB产品不支持主本地RAM。只有2MB的产品具有辅助本地RAM。

Note 3:INTOSTM0可以作为一个EIINT或FEIN中断来运行,但是不允许同时使用这两种方式。

*定时监视器(TSU)

这可以防止不受信任的程序非法使用CPU时间,管理属性,并控制中断被禁用的时间间隔。

6.2.1.3 EI Level Maskable Interrupts

(1) Interrupt Naming Rules (中断命名规则)

中断请求信号名称、分配的中断控制寄存器以及这些寄存器中的位的组成遵循特殊规则。

在下面,特定中断请求的名称由表示。

有关IC中使用的名称的详细信息,请参见Table 6.4。

◆ 中断请求名:INT<name>

前缀“INT”附加到<name>

◆ 中断控制寄存器:IC<name>

前缀“IC”附加到<name>

16位寄存器IC<name>也可以以字节单位访问。

–IC寄存器的低字节(bit[7:0]):IC<name>L

后缀“L”附加到IC<name>

–IC寄存器的高字节(bit[15:8]):IC<name>H

后缀“H”附加到IC<name>

◆ 中断控制寄存器位名称: CT<name>, RF<name>, MK<name>, TB<name>,P2<name>, P1<name>, P0<name>

位前缀“CT”、“RF”、“MK”、“TB”、“P2”、“P1”或“P0”附加到中断<name>。

举例:

来自TAUD0通道(<name>=TAUD0I2)的通道2的中断请求被命名为INTTAUD0I2。

相关的中断控制寄存器是ICTAUD0I2, ICTAUD0I2L, ICTAUD0I2H

这个寄存器中的位是CTTAUD0I2,RFTAUD0I2, MKTAUD0I2, TBTAUD0I2, P2TAUD0I2,P1TAUD0I2, P0TAUD0I2

(2)Priority

See Table 6.1, List of Exception Sources.

(3)Return PC

由EIRET指令从ISR返回的Return PC是程序暂停时的PC(当前PC)。

(4) Control Register

EI级可屏蔽中断控制寄存器。

See Section 6.4.1, ICxxx — EI Level Interrupt Control Registers。

(5) Return Instruction (返回指令)

EIRET instruction

(6)Configuration

EI级可屏蔽中断在总共288个通道上受支持,通道级联连接为INTC1和INTC2。

CAUTION

因为CPUCLK2是INTC2的工作时钟,所以连接到INTC2的INT32至INT287中断的延迟超过直接连接到INTC1的中断。

Table 6.4 lists EI level maskable interrupts。

Note 1:每个中断连接到INTC1通道0至31和INTC2通道32至287。

Note 2:这表示是否在电平或边缘检测到中断源。这也会影响EI级中断控制寄存器复位后的值。有关详细信息,请参阅Section 6.4.1, ICxxx — EI Level Interrupt Control Registers。对于电平检测,通过访问保留中断源的寄存器来清除中断源。寄存器的伪读取和SYNCP指令的执行需要将寄存器更新的结果反映到后续指令中。

Note 3:不考虑中断信道,偏移地址根据优先级(0到7)在+100H到170H的范围内确定。

Note 4:不管优先级如何,偏移地址均为+100H。

Note 5:表引用方法使用一个表来读取每个中断通道的异常处理程序地址,并通过引用该表来提取处理程序地址。表引用位置由以下公式确定:异常处理程序地址读取位置=INTBP寄存器+通道号×4字节

Note 6:同一中断源分配给不同的中断通道。有关详细信息,请参阅同一中断源分配给不同的中断通道。有关详细信息,请参阅Section 6.5.1, SELB_INTC1 — INTC1 Interrupt Select Register。

Note 7:两个中断源被分配给同一个中断通道。有关详细信息,请参阅Section 6.5.2, SELB_INTC2 — INTC2 Interrupt Select Register。

Note 8:For details, see Section 6.10, Exception Handler Address.

Note 9:Only supported in the F1L for Gateway。

Note 10:Only supported in devices with 1.5- and 2-MB code flash memories。

Note 11:INTOSTM0可以作为EIINT或假中断来运行,但不能同时使用两种方式。当OSTM0作为TSU(定时监控单元)运行时,它被用作假中断。当OSTM0作为TSU以外的任何函数时,它用作EIINT。

Note 12:For details on the interrupt source, see the RH850/F1L, RH850/F1M, RH850/F1H Flash Memory User’s Manual: Hardware

Interface.

6.2.2 FE Level Non-Maskable Interrupt Sources

6.2.3 FE Level Maskable Interrupt Sources

6.3 Edge/Level Detection (边沿/电平检测)

外部中断(TNMI和INTPm)可以指定为在外部中断引脚处检测到上升沿、下降沿、上升或下降沿、低电平或高电平时生成。

以下寄存器用于指定每个中断的边沿和电平:

6.4 Interrupt Controller Control Registers (中断控制器控制寄存器)

写入ICxxx、IMRm(m=0到8)、FNC和FIC寄存器仅在监控模式(PSW.UM=0)下启用。

6.5 EI Level Maskable Interrupt Select Registers (EI级别可屏蔽中断选择寄存器)

6.6 Interrupt Function System Registers (中断功能系统寄存器)

6.7 Operation when Acknowledging an Interrupt (识别到中断时的操作)

检查在指令执行期间报告的每个中断是否根据优先级得到确认。确认每个中断的程序如下所示。

(1)检查条件是否满足,中断是否按其优先级进行确认。

(2)根据当前PSW值计算异常处理程序地址。*1

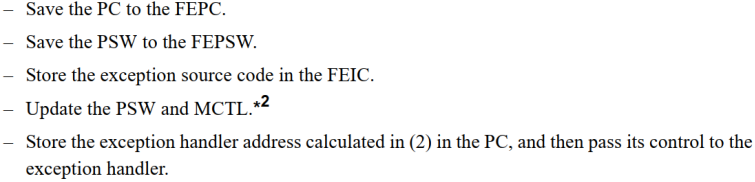

(3)对于FE级不可屏蔽/可屏蔽中断,执行以下处理:

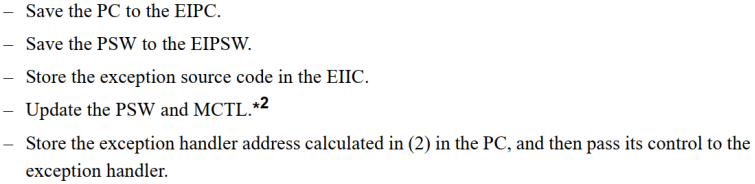

(4)对于EI级异常,执行以下处理:

Note 1:详细请参考Section 6.10, Exception Handler Address.

Note 2:有关需要更新的值,请参阅Table 4-1 Exception Cause List in the RH850G3K User’s Manual: Software.

下图显示了步骤(1)到(4)。

6.7.1 Exception Source Codes When an SYSERR Exception Occurs

下表列出了发生SYSERR异常时的异常源代码。

6.8 Return from Interrupts (从中断返回)

要从中断处理返回,请执行对应于每个相关中断级别的返回指令(EIRET或FERET)。

当上下文已保存在堆栈等中时,必须在执行返回指令之前恢复上下文。

EIRET指令用于从EI级可屏蔽中断处理返回,FERET指令用于从FE级可屏蔽中断处理返回。

当执行EIRET或FERET指令时,CPU执行以下处理,然后将其控制传递给返回的PC地址:

(1)从服务例程返回EI级别异常时,返回的PC和PSW值从EIPC和EIPSW寄存器加载。

从服务例程返回FE级别异常时,返回的PC和PSW值从FEPC和FEPSW寄存器加载。

(2)控制权被传递到返回PC和PSW所指示的地址。

(3)当EP=0和INTCFG.ISPC=0时,CPU更新ISPR寄存器。

使用EIRET和FERET指令从异常处理返回的流程如下所示。

6.9 Interrupt Operation

6.9.1 Interrupt Mask Function of EI Level Maskable Interrupt (EIINT)

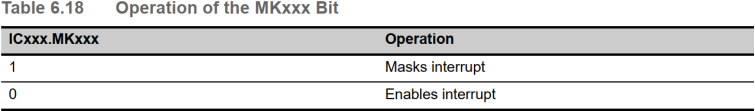

可以为EIINT的每个中断通道指定中断屏蔽。中断屏蔽由以下寄存器设置执行。

ICxxx.MKxxx位也可以通过IMRm寄存器的相应IMRmEIMKn位进行读写。中断掩码状态同时反映在ICxxx寄存器和IMRm寄存器中。

[ Operation example ]

(1)将1写入IMRm.imkn位时,禁止相应通道的中断。

(2)读取相应的ICxxx.MKxxx位时,返回1。

CAUTION

如果在中断请求挂起(RFxxx=1)时将MKxxx位设置为0,则中断服务例程将在此时执行(根据中断优先级规则)。即使通过将RFxxx位设置为1在软件中发出中断请求,只要用MKxxx=1屏蔽中断,中断也不会发生。

要取消挂起的中断请求,请清除软件中相应的RFxxx位。

6.9.2 Interrupt Priority Level Judgment (中断优先级判断)

当输入FE级不可屏蔽中断(FENMI)、FE级可屏蔽中断(FEINT)和EI级可屏蔽中断(EIINT)时,确定包括其他异常的优先级,并处理优先级最高的异常(包括中断)。同时发生的异常(包括中断)按预先分配的优先级顺序(默认优先级顺序)进行处理。

FENMI > FEINT > EIINT

See the RH850G3K User’s Manual: Software for other exceptions.

对于EIINT(INTn)中断,可以为每个中断源单独设置中断优先级。用位P2xxx到P0xxx指定中断优先级。中断优先级可以从0到7设置:0是最高的,7是最低的。在具有相同优先级的多个EIINT(INTn)中断中,具有最低中断通道号的中断具有优先级。

中断控制器在执行中断处理时,当另一中断请求被确认时,执行多个中断处理。当多个EIINT(INTn)中断同时发生时,要确认的中断由以下程序确定。

6.9.2.1 Comparison with the Priority Level of the Interrupt Currently being Handled (与当前正在处理的中断的优先级进行比较)

与当前正在处理的中断具有相同或更低优先级的中断被挂起。

当前正在处理的中断的优先级存储在ISPR寄存器中。

优先级高于当前处理的中断的中断进入下一优先级判断阶段。

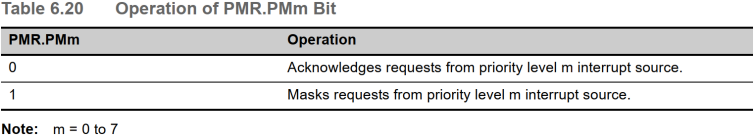

6.9.2.2 Masking through Priority Mask Register (PMR) (通过优先级屏蔽寄存器(PMR)屏蔽)

只有PMR寄存器启用的中断才能进入下一个优先级判断阶段。

For the PMR register, see Section 3.3.3.2, PMR — Interrupt Priority Masking, or the RH850G3K User’s Manual: Software.

6.9.2.3 The Requested Interrupt Source with the Highest Priority Level is Selected (具有最高优先级的请求中断源被选中)

当同时从多个源请求中断时,由ICxxx设置最高优先级的中断。P[2:0]xxx位优先。当存在多个最高优先级中断(ICxxx.P[2:0]xxx位=0)时,选择最低中断通道号。

6.9.2.4 Interrupt Hold by CPU (CPU中断保持)

中断确认根据PSW寄存器的NP和ID位的状态保持。此时,即使在中断确认挂起时,也执行EIINT中断之间的优先级判断以及EIINT、FEINT和FENMI中断之间的优先级判断,并且在满足确认条件时选择具有最高优先级的中断。

Example

已请求优先级为5的EIINT中断,中断生成挂起,因为PSW.ID位的值为1。如果请求优先级为3的后续EIINT中断,并且PSW.ID位被清除为0,则将生成后一个EIINT中断(优先级为3)。

Figure 6.4显示了在执行中断处理时确认另一个中断请求时的多重中断处理示例。

当中断请求信号被确认时,PSW.ID标志自动设置为1。因此,ID标志应清除为0以执行多个中断处理。具体地,在中断处理程序中执行EI指令等以使能中断。

CAUTION

为了执行多重中断服务,必须在执行EI指令之前保存EIPC和EIPSW寄存器的值。从多中断服务返回时,在执行DI指令后恢复EIPC和EIPSW的值。

6.9.3 Interrupt Request Acknowledgement Conditions and the Priority (中断请求确认条件和优先级)

See the RH850G3K User’s Manual: Software.

6.9.4 Exception Priority of Interrupts and the Priority Mask (中断的异常优先级和优先级掩码)

See the RH850G3K User’s Manual: Software.

6.9.5 Interrupt Priority Mask (中断优先级掩码)

See the RH850G3K User’s Manual: Software.

6.9.6 Priority Mask Function (优先级掩码功能)

优先级掩码函数禁止指定中断优先级的所有EIINT中断。

要屏蔽的中断优先级在PMR寄存器中指定。可以为每个优先级设置掩蔽和确认。

使用此功能可以执行以下操作:

◆ 临时禁止优先级低于给定优先级的中断

◆ 临时禁止具有给定优先级的中断

使用此功能挂起的EIINT中断的存在可以通过 Section 6.9.7, Exception Management.。

For details on the PMR register, see Section 3.3.3.2, PMR — Interrupt Priority Masking, or the RH850G3K User’s Manual: Software.

6.9.7 Exception Management (异常管理)

可以在RH850/F1L中检查挂起的中断。For details, see the RH850G3K User’s Manual:Software.

6.10 Exception Handler Address (异常处理函数地址)

在RH850/F1L中,可以根据设置更改输入复位后或确认异常或中断时执行处理程序的异常处理程序地址。

重置和异常(包括中断)的异常处理程序地址是用直接向量法确定的,其中异常处理程序地址的参考点可以通过使用PSW.EBV位、RBASE寄存器和EBASE寄存器来更改。对于中断,可以为每个通道选择直接矢量法和表参考法。如果选择了表引用方法,则执行可以分支到内存中分配的异常处理程序表所指示的地址。

CAUTION

使用直接向量方法选择的EIINT(INTn)的异常处理程序地址与V850E2核心产品的不同。在V850E2核心产品中,一个不同的异常处理程序地址被分别分配给每个中断通道(EIINT(INTn))。在RH850/F1L中,为每个中断优先级分配一个异常处理程序地址。因此,具有相同优先级的中断将分支到相同的异常处理程序。

6.10.1 Direct Vector Method

CPU使用将Table 6.21中所示的偏移量相加的结果,将基址寄存器/偏移量地址的选择添加到由RBASE或EBASE寄存器指示的基址,作为异常处理程序地址。

通过使用PSW.EBV位*1选择是将RBASE还是EBASE寄存器用作基址。当PSW.EBV位设置为1时,EBASE寄存器的值用作基址。当PSW.EBV位清除为0时,RBASE寄存器的值用作基址。

但是,对于RESET或SYSERR exception*2,始终使用RBASE寄存器作为参考。

此外,用户中断可以看到相应基址寄存器的RINT位,并根据位的状态减少偏移地址。如果RBASE.RINT位或EBASE.RINT位设置为1,则所有用户中断都使用100H的偏移量进行处理。如果位被清除为0,则根据Table 6.21, Selection of Base Register/Offset Address。

Note 1:异常确认本身有时可能会更新PSW.EBV位的状态。在这种情况下,基于更新的值选择基址寄存器。

Note 2:如果在选择code flash P/E模式或FCU固件区域时生成SYSERR,则微控制器处于未定义状态。For detail of code flash P/E mode and selection of FCU firmware area, see the RH850/F1L,RH850/F1M, RH850/F1H Flash Momory User’s Manual: Hardware Interface.

下表显示了基址寄存器选择和偏移地址缩减如何为每个异常确定异常处理程序地址。PSW位的值根据异常确认更新的值确定异常处理程序地址。

基址寄存器选择用于对复位和某些硬件错误执行异常处理,方法是使用相对可靠的区域(如ROM)中的程序,而不是易受软件错误影响的区域(如RAM和cache区域)。用户中断偏移地址缩减功能用于减少特定系统内部操作模式下异常处理程序所需的内存占用大小。这样做的主要目的是使仅使用最小功能的操作模式(例如,在系统维护和诊断期间)消耗的内存量最小化。

6.10.2 Table Reference Method

对于直接向量方法,每个中断优先级有一个用户中断异常处理程序,中断通道指示多个具有相同优先级的中断分支到同一中断处理程序,但有些用户可能希望从一开始就为每个中断处理程序使用不同的代码区域。

RH850/F1L使用表引用方法处理假定上述用法的中断。

如果在中断控制器等中将表参考方法指定为中断信道向量选择方法,则当确认与该中断信道对应的中断请求时,用于确定异常处理程序地址的方法不同如下。

<1> 在以下任何情况下,通过使用直接向量方法确定异常处理程序地址:

–当PSW.EBV=0且RBASE.RINT=1时

–当PSW.EBV=1和EBASE.RINT=1时

–当中断通道设置不是表参考方法时

<2> 在<1>以外的情况下,计算表参考位置。

异常处理程序地址读取位置=INTBP寄存器+通道号×4字节

<3> 从<2>中计算的中断处理程序地址读取位置开始读取字数据。

<4> 使用<3>中读取的单词data作为异常处理程序地址。

Table 6.22显示了与每个中断通道相对应的异常处理程序地址读取位置,Figure 6.8显示了内存中分配的概述。

2598

2598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?