第一章

1、控制复杂性的艺术:

A、抽象:管理复杂性的关键技术在于抽象即隐蔽不重要的细节

B、约束:对设计选择的一种内在限制,目的是为了可以更有效的在更高的抽象层

次上工作

C、三条原则:

层次化:一个系统划分为模块和子模块

模块化:所有模块有定义好的功能和借口

规整化:模块间寻求一致,这样模块易于被重新使用

2、数字系统:

数的进制、补码

3、 NML= VIL – VOL

NMH= VOH– VIH

4、什么是数字系统的静态约束

静态约束要求对于给定的有效逻辑输入,每个电路元件应该能产生有效的逻辑输出。

第二章

1、 数字电路:

(1)一个或多个离散变量输入端

(2)一个或多个离散变量输出端

(3)功能规范描述输入和输出的关系

(4)时序规范描述当输入改变是输出响应的延迟。

一个包含离散电压值输入和输出的模块由节点和元件组成;节点是一段导线,通过电压传递离散变量,分为输入节点、输出节点和内部节点;元件是带有输入、输出、功能规范(描述输入和输出的关系)、时序规范(描述当输入改变时输出响应的延迟)的电路

2、组合电路:无记忆(只跟当前输入有关)

A、 每一个电路元件本身都是组合电路;

B、 每一个电路节点或者是一个电路的输入,或者仅仅连接到一个电路元件的一个输出端口

C、 电路不能包含回路:经过电路的每条路径最多只能经过每个电路节点一次逻辑电路:

有记忆(和当前输入有关,跟以前的输入也有关)

一般而言所有不是组合电路的电路都可以称为时序电路

A、 每一个电路元件是寄存器或组合电路

B、 至少有一个电路元件是寄存器

C、 所有寄存器接受同一个时钟信号

D、 每一个环路至少包含一个寄存器

2、 布尔表达式

或与式、与或式、最大项和最小项

最小项就是有若干积(“与”构成了最小项,真值表相与取值为1的)的和(或)构成。是与或式。

最大项就是有若干和(“或”构成了最大项,真值表中相或取0的)的积(与)。是或与式。

4、X和Z

非法值X:符号X表示电路节点的值未知或未知,通常会发生在此节点同时被0或者1驱动(称之为竞争)

浮空值Z:符号Z表示节点既没有被高电平驱动也没有被低电平驱动。这个节点被称为浮空,高阻态,或者高Z态

5、组合逻辑模块

多路选择器是一种最常用的组合逻辑电路。它从几个可能的输入中根据选择信号的值来选择一个作为输出。见54页例子2.12

译码器有N个输入和2N个输出。它的每一个输出都取决于输入的组合。

6、时序

组合逻辑电路的时序特征包括传输延迟和最小延迟的特征

传输延迟:

输入改变直到对应的一个和多个输出到达它们最终的值所经历的最长时间

最小延迟(污染延迟):

当一个输入发生变化到任何一个输出开始改变的最短时间

关键路径(耗时最长),最短路径(耗时最短)

毛刺:一个输入信号的改变可能会导致多个输出信号的改变。这被称为毛刺或者冲突。

第三章

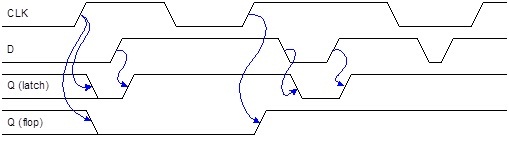

1、 锁存器和触发器

a) D锁存器是电平敏感的,D触发器是边沿触发的

Latch:锁存器 Flop:触发器

2、 有限状态自动机(必考)熟练掌握如何如何使用有限状态机来设计数字系统包括编码

Moore型有限状态机的输出仅仅取决于当前的状态

Mealy 型有限状态机的输出取决于当前的状态和输入值

3、 时序逻辑电路的时序

建立时间约束

保持时间约束

A、 动态约束:动态约束是指同步时序电路的输入在时钟沿附近的建立和维持孔径时间内必须保持稳定。

B、 系统时序

C、 时钟偏移

D、 亚稳态

E、 同步器

第四章

模拟阶段,在模块上加入输入,并检查输出已验证模块的操作是否正确。在综合阶段,将模块的文字描述转换成逻辑门。

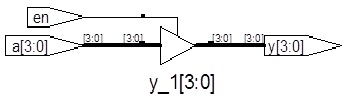

三态缓冲器

moduletristate(input [3:0] a,

input en,

output [3:0] y);

assign y = en ? a: 4'bz;

endmodule

例 8’b11 的各部分含义以及存储

1、 时序逻辑

寄存器

可复位寄存器

带使能端的寄存器

多寄存器

锁存器

2、 测试程序

测试程序是用于测试其他待测试模块的硬件描述语言模块。此程序包含了向待测试模块提供输入的语句,已测试是否产生了理想的正确输出。输入和期待的输出模式成为测试向量。

1) 被测元件实例化

2) 形成激励信号

3) 输出结果处理和预期结果比较

本章主要是代码的书写,应注意

第五章

1、算数电路:

加法

减法:加法器求反加一

比较器:寄存器数据通路,复用器控制通路

2、数字系统:

定点数系统

3、存储器阵列

可编程逻辑阵列(PLA)

现场可编程门阵列(FPGA)

用case语句可以实现计数器

Always@(posedge clk,posedgereset)

Begin

If(!reset)

Q<=0;

Else

Q<=Q+1;

End

第六章

体系结构前面部分几节的概念

体系结构设计准则

Simplicity favors regularity简单有助于归整化

Make the common case fast加快常见功能

Smaller is faster越小设计越快

Good design demands good compromises好的设计需要折中

汇编语言

MIPS体系结构中R/I/J指令差别

R-Type: registeroperands

I-Type: immediateoperand

J-Type: forjumping (we’ll discuss later)

第七章

微结构前面部分的概念

单周期:每个指令都在单个周期内执行

多周期:每个指令被分解成一系列较短的步骤

流水线:每个指令被分解成一系列的步骤在一次执行多个指令。

单周期处理器着重掌握,包括编码

单周期mips处理器一个周期的步骤

1.取指令

2.从寄存器文件读取源操作数

3.即时符号扩展

4.存储器地址的计算

5.从内存中读取数据,并把它写回寄存器文件

6.确定的下一条指令的地址

4892

4892

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?