学习达芬奇PRO FPGA开发板

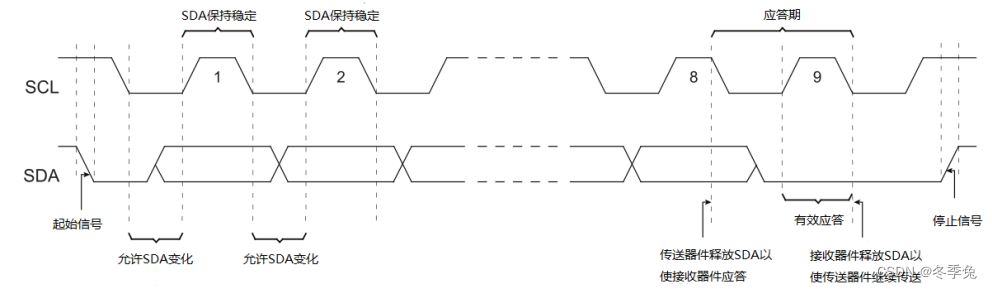

SCL为高电平时,SDA要求保持稳定,所以SDA需在SCL低电平时赋值。这里注意,我们代表着主机。

在编写代码时,注意起始信号与应答结束。

而在生成I2C的SCL的四倍频率驱动时钟时,clk_divide[8:1]表示对clk_divide除以2 25-1=24,结果得到clk时钟频率的1/50 为1M,即dri_clk 为1M,在状态机中,dri_clk又四分频得到SCL,SCL为0.25M 与预计相符。

同时注意代码中信号的0或1代表信息,不要搞反。

图片来源达芬奇PRO FPGA开发板开发指南 V2.1

3631

3631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?