数字IC后端设计实现流程之initial design

前端提供的文件

- 门级网表 (Gate Level Netlist)

数字前端工程师或者是 R2N 的同事在 release 东西给后端工程师做 PR 时,一定会 release 一个门级网表,这个 netlist 是基于 RTL 或者 gtech 文件进行逻辑综合后产生的一个门级网表。这个网表包含了当前 block 的所有 sub-module,通过 hierarchy 的调用方式,最后有个顶层的设计,这个顶层名字就是我们所说的设计 module 名字。另外还有指出了 block 有哪些输入端口,输出端口,block 中用到了标准单元库中的那些 cell。

- 时序约束文件(Timing Constraint)

时序约束文件在整个数字 IC 设计过程的作用是一样的。它都是 guide 工具基于某个特定的目标去做逻辑和时序的优化。一个时序约束文件都需要含有以下几个部分:

Crete_clock –name CLK -period 10 [get_ports clk]

Set_clock_uncertainty -setup 0.1 [all_clocks]

Set_max_transition –max 0.2 [current_design]

Set_max_transition 0.1 -clock CLK

Set load 50 [all_outputs]

Set_max_fanout 40 [current_design]

Set_dont_touch $cells

Set_input_delay –clock -max [get_ports **]

Set_input_delay –clock -min [get_ports **]

Set_output_delay -clock -max [get_ports **]

Set_output_delay -clock –min [get_ports **]

Set_multicycle_path 3 -setup -end -from ***

Set_multicycle_path 2 -hold -end -from ***

Set_false_path -from ** -to **

Set_clock_group –async -name ic-backend -group {A B} -group {C D}

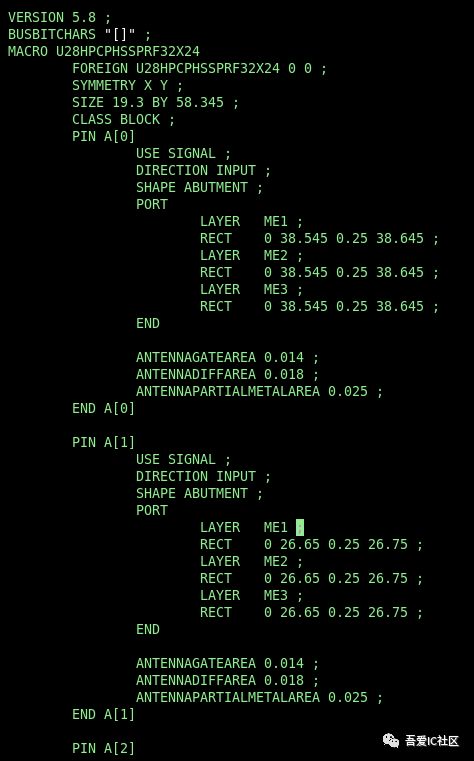

- Memory 的 lef 文件

前端工程师在 compiler 对应 memory 的时候会产生对应的一些文件,比如 LEF,DB 和 GDS 文件等。这个 Memory lef 是提供给后端工程师做 milkyway 用的。

- 逻辑综合(Design Compiler)后 pre-layout 的信息统计

正规的 flow 中,在 release gate level netlist 时都需要附上逻辑综合后的纯逻辑的面积,memory 的面积,io port 数量,IO PAD 数量以及 ip 等相关信息。因为这些信息能够帮助数字后端工程师更快速地完成模块的面积估算,特别是某个 stage RTL 改动比较大的时候。

- Prime Time QA report

资深的工程师在 release netlist 之前,一定会自己在 Prime time 中对设计进行 QA,检查当前 design 的 timing 是否可接受,检查 memory 是否存在 min period 等问题。

Foundary 提供的文件

- 工艺库 lef 文件,timing model db 文件

Lef 文件以及 db 文件主要用来后续做 Milkyway library 和 NDM library。

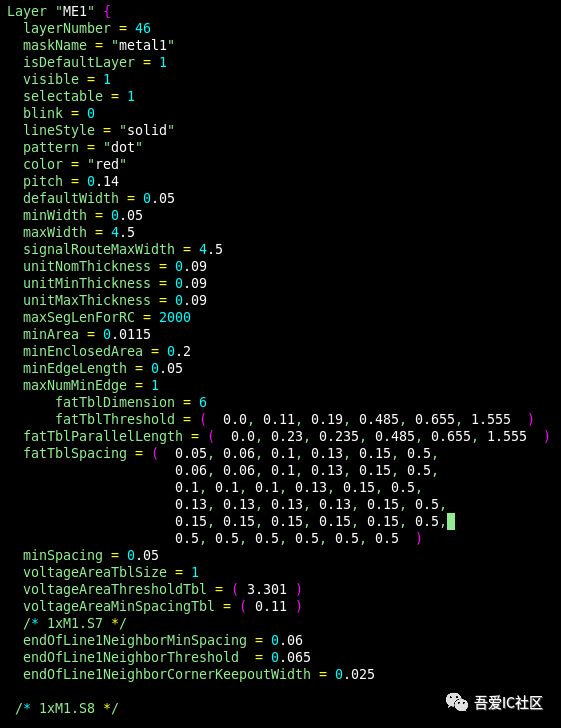

- 工艺的 tech file 文件

Techfile 文件一般是由 Foundary 提供的,当然也有是第三方 Vendor 提供的,比如 ARM 可能会提供他们自己的 standard cell 和 memory 的 library 给客户使用。

这个 tech file 文件主要是提供给 APR(Auto Place And Route)工具使用,guide 工具完成绕线使用。这个文件会给出每层 Metal 的 min width ,min space 以及 via 的相关定义等信息。

这里留一个思考题: 既然这个 tech file 规定了金属层,via 间的 rule 信息了,能不能将 ICC/ICC2 中绕线后的 DRC 结果作为 signoff drc 的结果(即不用 calibre 跑 DRC)?

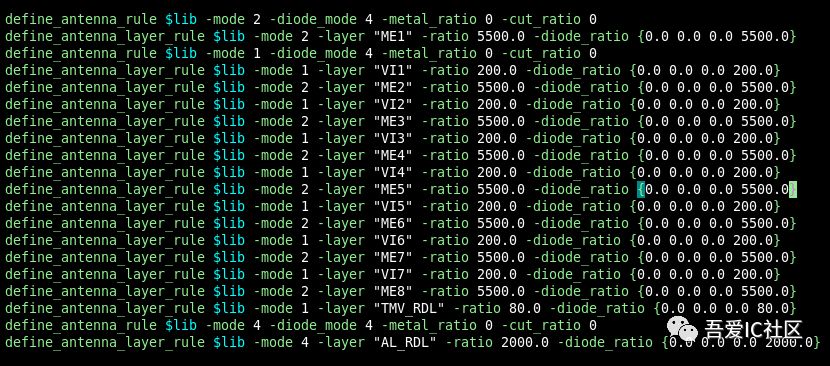

- 天线规则文件 (antenna rule)

Foundary 一般都会提供天线规则文件,以 clf 格式给出。此时需要改成 ICC 或者 ICC2 的 tcl 格式。下图给出供 ICC2 使用的 antenna tcl 文件,大家可以和 clf 文件进行对比。关于 antenna layer 的定义希望大家搞清楚,有的时候可能需要做更改哦。吾爱 IC 社区的小编在之前的文章提及到这个玩意哦。

- Tluplus 文件和 layer map 文件

这个文件提供了 RC 相关信息,主要用来供工具估算 delay 信息的。

数字后端工程师需要准备的事情

- Milkyway 和 NDM 生成

为何要用 Milkyway 和 NDM?Milkyway 是供 ICC 使用,NDM 则是供 ICC2 使用。这里简单说下,MIlkyway 是对应 GDS 的抽象化,因为它文件不大,信息量够 PR 工具使用。有人可能会说直接用 GDS,试问你是想玩死工具吗?Milkyway 的制作其实就包含了三类信息,Blockage,Pin,Via,就是通常所说的 BPV。简而言之,就是 Milkyway 就是告诉 tool,这个 ip 有多大,有哪些 signal pin,power ground pin, 哪些地方有 blockage,在哪些地方可以打孔。

关于 Milkyway 和 NDM 的制作脚本,小编之前已经分享在知识星球了,需要的朋友可以前往查看。

- 检查时序约束文件

在读入 netlist 前,需要检查下前端提供的时序约束文件 constraint,检查时钟周期是否符合 spec? 检查时序约束是否存在缺失?检查是否有 ideal network 的约束?

- 读入 netlist 和 DC constraint

做完以上各个准备工作后,可以读入 design 的 netlist 和 DC constraint。经常会有人来问关于读 netlist 出现的各种错误,这里简单罗列几种常见错误的原因:

-

参考库(reference library)缺失

-

Netlist 中含有未映射到标准单元库的 cell,比如存在 GTECH 这样的 cell

-

TOP module 名字指定错误

-

子模块的 milkyway 和 db 文件不一致(主要是指两边 port 不一致)

成功读入 design 的 netlist 和 constraint 后,设计就算导入成功了,完成了第一步 initial design 的工作。整个 initial design 的参考脚本请点击下方的 “阅读原文” 查看。

好了,今天的分享就到这里了。下一期会进行数字 IC 后端实现中关于 floorplan 的内容分享。

https://mp.weixin.qq.com/s/bfmCxNlhlI9LftBF2HAXLQ">https://mp.weixin.qq.com/s/bfmCxNlhlI9LftBF2HAXLQ

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?