本章介绍了标准的整数乘法和除法指令扩展,命名为“ M”,其中包含将两个整数寄存器中保存的值相乘或相除的指令。

我们将整数乘法和除法从基本指令集中分离出来,以简化低端实现,或者针对不经常使用整数乘法和除法或者在附加加速器中处理得更好的应用。

9.1 乘法运算

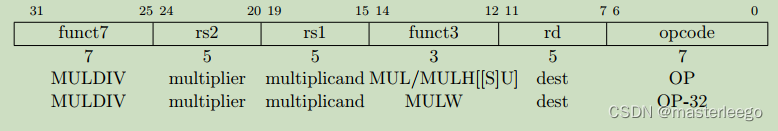

MUL实现rs1与rs2之间的XLEN位与XLEN位乘法,并将结果的低XLEN位放在目标寄存器中。MULH、MULHU和MULHSU执行相同的乘法,但返回完整的2×XLEN位乘积的高XLEN位,分别对应于有符号×有符号、无符号×无符号和有符号rs1×无符号rs2乘法。如果同时需要同一乘积的高位和低位,则建议的代码序列为:MULH[[S]U] rdh,rs1,rs2; MUL rdl,rs1,rs2(源寄存器指示符必须是相同的顺序,并且rdh不能与rs1或rs2相同)。然后微体系结构可以将它们融合为一个乘法运算,而不是执行两个单独的乘法。

MULHSU用于多字有符号乘法中,将被乘数的最高有效字(包含符号位)与乘数的较低有效字(无符号)相乘。(?)

MULW是RV64指令,它将源寄存器中的低32位相乘,然后将结果的低32位以符号位扩展后放入目标寄存器。

在RV64中,可以使用MUL来获取64位乘积的高32位,但是带符号的自变量必须是正确的32位带符号的值,而无符号的自变量其高32位必须为零。如果不知道参数是符号扩展还是零扩展,则可以选择将两个参数都左移32位,然后使用MULH[[S]U]。

9.2 除法运算

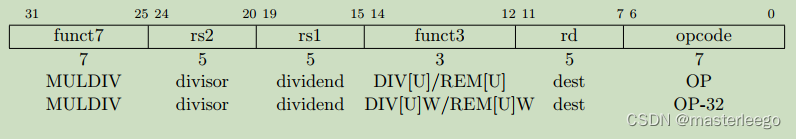

DIV和DIVU分别实现一个rs1除以rs2的XLEN位与XLEN位有符号和无符号除法,并向零舍入。REM和REMU提供了相应除法运算的余数部分。对于REM,结果的符号与被除数的符号相同。

对于有符号和无符号除法,原则都是被除数=除数×商+余数。

如果同一除法的商和余数都需要的话,则建议的代码序列为:DIV[U] rdq,rs1,rs2; REM[U] rdr,rs1,rs2(rdq不能与rs1或rs2相同)。然后微体系结构可以将它们融合为一个除法运算,而不是执行两个单独的除法运算。

DIVW和DIVUW是RV64指令,它们将rs1的低32位除以rs2的低32位,分别将它们视为有符号和无符号整数,然后将32位商数放在rd中,并以符号位扩展为64位。REMW和REMUW是RV64指令,分别提供相应的有符号和无符号余数运算。REMW和REMUW总是将32位结果以符号位扩展为64位(包括除以零)。

表9.1总结了除以零和除法溢出的语义。除以零的商所有位均为1,除以零的余数等于被除数。仅当最小的负整数除以-1时,才发生有符号除法溢出。带溢出的有符号除法的商等于被除数,余数为零。无符号除法溢出不会发生。(?)

![表格9.1 零除和除法溢出的语义。L是操作的宽度,以位为单位:对于DIV[U]和REM[U]为XLEN,对于DIV[U]W和REM[U]W为32。](https://img-blog.csdnimg.cn/02365d8db02c48f0bb22f92ebff4d31d.png)

我们考虑过在整数除以零的情况下引发异常,这些异常在大多数执行环境中都会导致陷阱。然而,这将是标准ISA中唯一的算术陷阱(浮点异常设置标志并写入默认值,但不会导致陷阱),并且在这种情况下,需要语言实现者与执行环境的陷阱处理程序进行交互。此外,在语言标准规定“除以零”异常必须立即导致控制流更改的情况下,只需向每个除法运算添加一条分支指令,并且该分支指令可以插入除法之后,并且通常预测为不发生,这几乎不会增加运行时开销。

为无符号和有符号除以零返回所有位置位的值,以简化除法器电路。所有位均为1的值既是无符号除法返回的自然值,表示最大的无符号数,也是简单无符号除法器实现的自然结果。有符号除法通常使用无符号除法电路来实现,并且指定相同的溢出结果简化了硬件。

9.3 Zmmul扩展,V1.0,已批准

Zmmul扩展实现了M扩展的乘法子集。它添加了9.1节定义的所有乘法指令:MUL、MULH、MULHU、MULHSU以及(仅用于RV64)MULW。指令编码和M扩展指令是一致的。

Zmmul扩展支持需要乘法运算而不需要除法的低成本实现。对于许多微控制器应用来说,除法操作过于罕见,无法证明除法器硬件成本的合理性。相比之下,乘法运算更加频繁,使得乘法器硬件的成本更加合理。简单的FPGA软内核特别受益于消除除法但保留乘法的变动,因为许多FPGA提供硬核乘法器,但要求在软逻辑中实现除法器。

663

663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?