文章目录

ARM系统开发基础

电路基础

软件和硬件的对应关系

软件: 0 1

电路: 低电平 高电平

芯片: 截止 导通

二极管

1) 单向导通特性 --- 整流

2) 反向击穿特性 --- 稳压管

3) 发光特性 --- LED

4) 电容特性 --- 储能 RAM

RAM

1) SRAM --- 硬件解决 --- 有三大总线、快、贵

2) DRAM --- 软件解决 --- 没有三大总线(必须初始化后才使用)、便宜、慢

三极管 — 开关

1)区分NPN和PNP 看箭头 P—>N

2)控制逻辑

PNP

导通:基极上加低电压

截止:基极上加高电压

NPN

导通:基极上加高电压

截止:基极上加低电压

MOS管 — 开关

1) 区分N沟道和P沟道看箭头 P--->N 取首字母

2) 控制逻辑

P型

导通:栅极上加低电压

截止:栅极上加高电压

N型

导通:栅极上加高电压

截止:栅极上加低电压

补充:二极管三极管和MOS管区别

电子管

这三种管都是半导体器件。

1.二极管顾名思义就是有两个极,只有一个PN结,是将PN结加上相应的电极引线和管壳就成为半导体二极管。适用于高频和小功率的工作,也用作数字电路中的开关元件,二极管具有单向导通的特性,一般用在整流、稳压、续流等领域。

2.三极管简称晶体管,(包含有集电极c,发射极e,基极b)不是简单的两个PN结拼起来的,每个极的厚度都有讲究的。三极管分为NPN型和PNP型两种,是最重要的一种半导体器件。它能起放大、振荡或开关等作用。

3.MOS管也称为场效应管,是一种较新型的半导体器件。外形与普通晶体管相似,但两者的控制特性却截然不同。

普能晶体管是电流控制元件,通过控制基极电流达到控制集电极电流或发射极电流的目的,到信号源必须提供一定的电流才能工作。

MOS管则是电压控制元件,它的输出电流决定于输入端电压的大小,基本上不需要信号源提供电流,所以它的输入电阻很高,这是它的突出特点。它广泛应用于放大电路和数字电路。

数字门电路

(1)与门 – 断路特性 – 遇0为0

(2)或门 – 短路特性 – 遇1为1

(3)非门 – 取反

1.异或:如果a、b两个值不相同,则异或结果为1。如果a、b两个值相同,异或结果为0。

2.与或非门

1)“与”运算及“与”门(有0得0,没0得1)

2)“或”运算及“或”门 决定某一结论的所有条件中,只要有一个成立,则结论就成立,这种因果关系叫或逻辑

3)“非”运算及“非”门 若前提条件为“真”,则结论为“假”; 若前提条件为“假”, 则结论为“真”。即结论是对前提条件的否定, 这种因果关系叫非逻辑

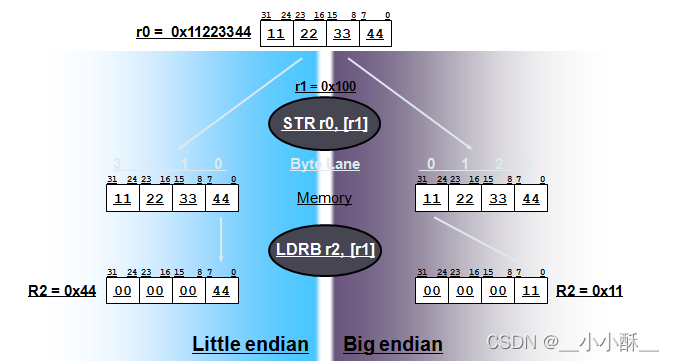

字节顺序:

1)ARM体系结构将存储器看作是从0地址开始的字节线性组合。从0字节到3字节放置第一个存储的字(32位)数据,从第4个字节到第7个字节放置第二个存储的字数据,依次排列。

ARM处理器是32位处理器,它的寻址空间最大为4G,以字为单位进行对齐。

字对齐:比如说你有一个32位整型数,存放的时候,它可以存放在0的位置,4的位置,8的位置,但是不可以存放在3这个字节位置,不满足字节对齐。

2)ARM体系结构可以用两种方法存储字数据,称之为大端格式和小端格式。

我们用的ARM cortex-A9使用的是小端格式存储。

大端和小端存储格式区别:

大端格式:字数据的高字节存储在低地址中,而字数据的低字节则存放在高地址中。

小端格式:与大端存储格式相反,在小端存储格式中,低地址中存放的是字数据的低字节,高地址存放的是字数据的高字节。

小端:低对低,高对高

大端:高对低,低对高

The ARM 可以用 little/big endian格式存储数据

Little endian:

最低有效字节被存储在内存的低地址空间

Big endian:

最高有效字节被存储在内存的低地址空间

计算机硬件组成:

1.输入设备

2.输出设备

3.存储器

4.运算器

5.控制器

6.计算机总线结构

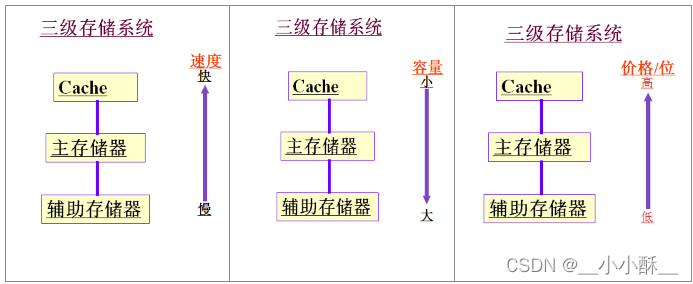

存储器:

存储器是用来存放程序和数据的部件,它是一个记忆装置,也是计算机能够实现“存储程序控制”的基础。

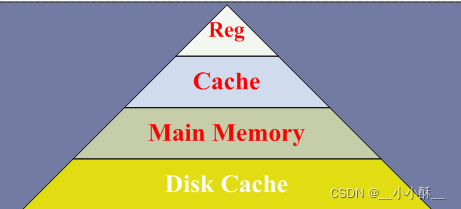

1).高速缓冲存储器(Cache)

CPU可以直接访问,用来存放当前正在执行的程序中的活跃部分,以便快速地向CPU提供指令和数据。

(高速缓存是什么(一级缓存))

2).主存储器

可由CPU直接访问,用来存放当前正在执行的程序和数据。

(CPU可访问主存)

3).辅助存储器

设置在主机外部,CPU不能直接访问,用来存放暂时不参与运行的程序和数据,需要时再传送到主存。

存储速度:reg->cache->main memory->disk cache

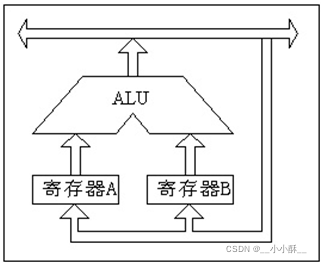

运算器

是对信息进行处理和运算的部件,经常进行的运算是算术运算和逻辑运算,因此运算器的核心是算术逻辑运算部件ALU,运算器中有若干个寄存器(如累加寄存器、暂存器等)

控制器

是整个计算机的指挥中心。控制器中主要包括时序控制信号形成部件和一些专用的寄存器。

计算机的总线结构

将各大基本部件,按某种方式连接起来就构成了计算机的硬件系统。

目前许多计算机(主要指小、微型计算机)的各大基本部件之间是用总线(Bus)连接起来的。

总线是一组能为多个部件服务的公共信息传送线路,它能分时地发送与接收各部件的信息。

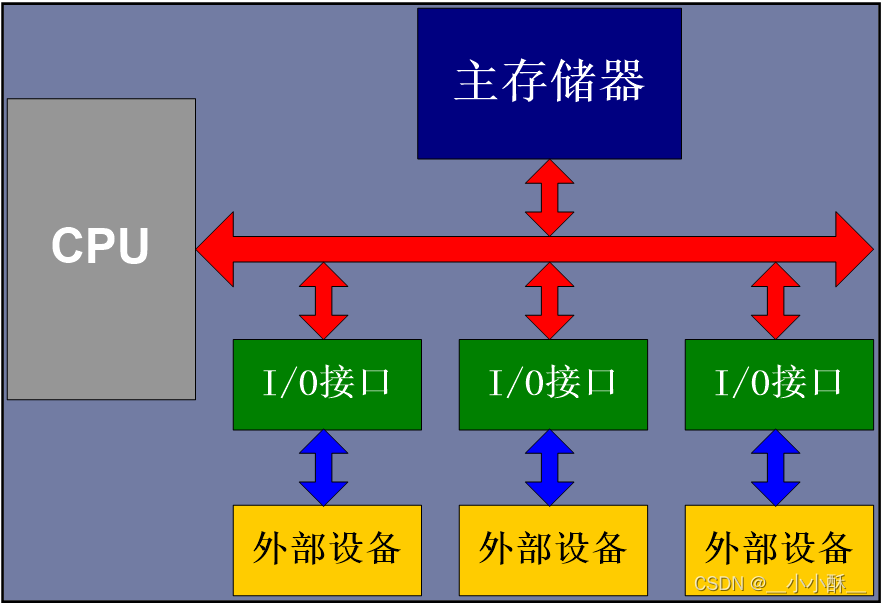

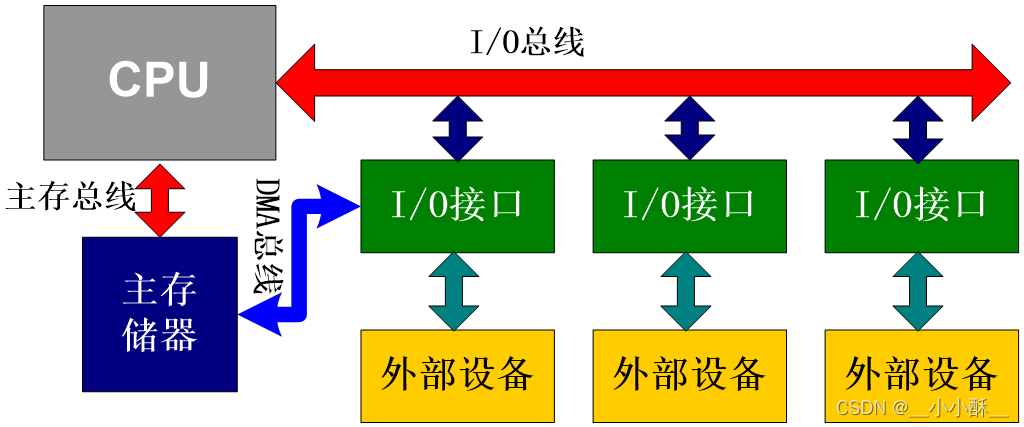

单总线

多总线

ARM工作状态

1).ARM状态,此时处理器执行32位字对齐的ARM指令。

2).Thumb状态,此时处理器执行16位字对齐的Thumb指令。

3).Jazelle状态

发生异常以后,处理器会工作在ARM状态

当ARM处理器执行32位的ARM指令集时,工作在ARM状态。

当ARM处理器执行16位的Thumb指令集时,工作在Thumb状态。

在程序执行过程中,处理器可以在两种工作状态之间切换,并且cpu工作状态并不影响cpu的工作模式和相应的寄存器中的内容

哈佛结构和冯诺依曼结构

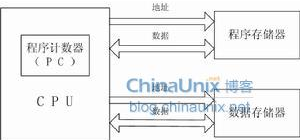

- 冯·诺依曼结构

冯·诺依曼结构又称作普林斯顿体系结构。

冯·诺依曼的主要贡献就是提出并实现了“存储程序”的概念和二进制原理,后来,人们把利用这种概念和原理设计的电子计算机系统统称为“冯·诺依曼型结构”计算机。冯·诺依曼结构的处理器使用同一个存储器,经由同一个总线传输。

由于指令和数据都是二进制码,指令和操作数的地址又密切相关,因此,当初选择这种结构是自然的。但是,这种指令和数据共享同一总线的结构,使得信息流的传输成为限制计算机性能的瓶颈,影响了数据处理速度的提高。

完成一条指令需要3个步骤,即:取指令、指令译码和执行指令。

对冯·诺依曼结构处理器,由于取指令和存取数据要从同一个存储空间存取,经由同一总线传输,因而它们无法重叠执行,只有一个完成后再进行下一个。

-

哈佛结构

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构,如图1所示。

哈佛结构的微处理器通常具有较高的执行效率。其程序指令和数据指令分开组织和存储的,执行时可以预先读取下一条指令。

哈佛结构是指程序和数据空间独立的体系结构,目的是为了减轻程序运行时的访存瓶颈。

例如最常见的卷积运算中, 一条指令同时取两个操作数,在流水线处理时, 同时还有一个取指操作, 如果程序和数据通过一条总线访问, 取指和取数必会产生冲突, 而这对大运算量的循环的执行效率是很不利的。

哈佛结构能基本上解决取指和取数的冲突问题。 -

冯·诺依曼体系和哈佛总线体系的区别

二者的区别就是程序空间和数据空间是否是一体的。冯·诺依曼结构数据空间和地址空间不分开,哈佛结构数据空间和地址空间是分开的。

早期的微处理器大多采用冯·诺依曼结构,典型代表是Intel公司的X86微处理器。

哈佛总线技术应用是以DSP和ARM为代表的。

3410

3410

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?