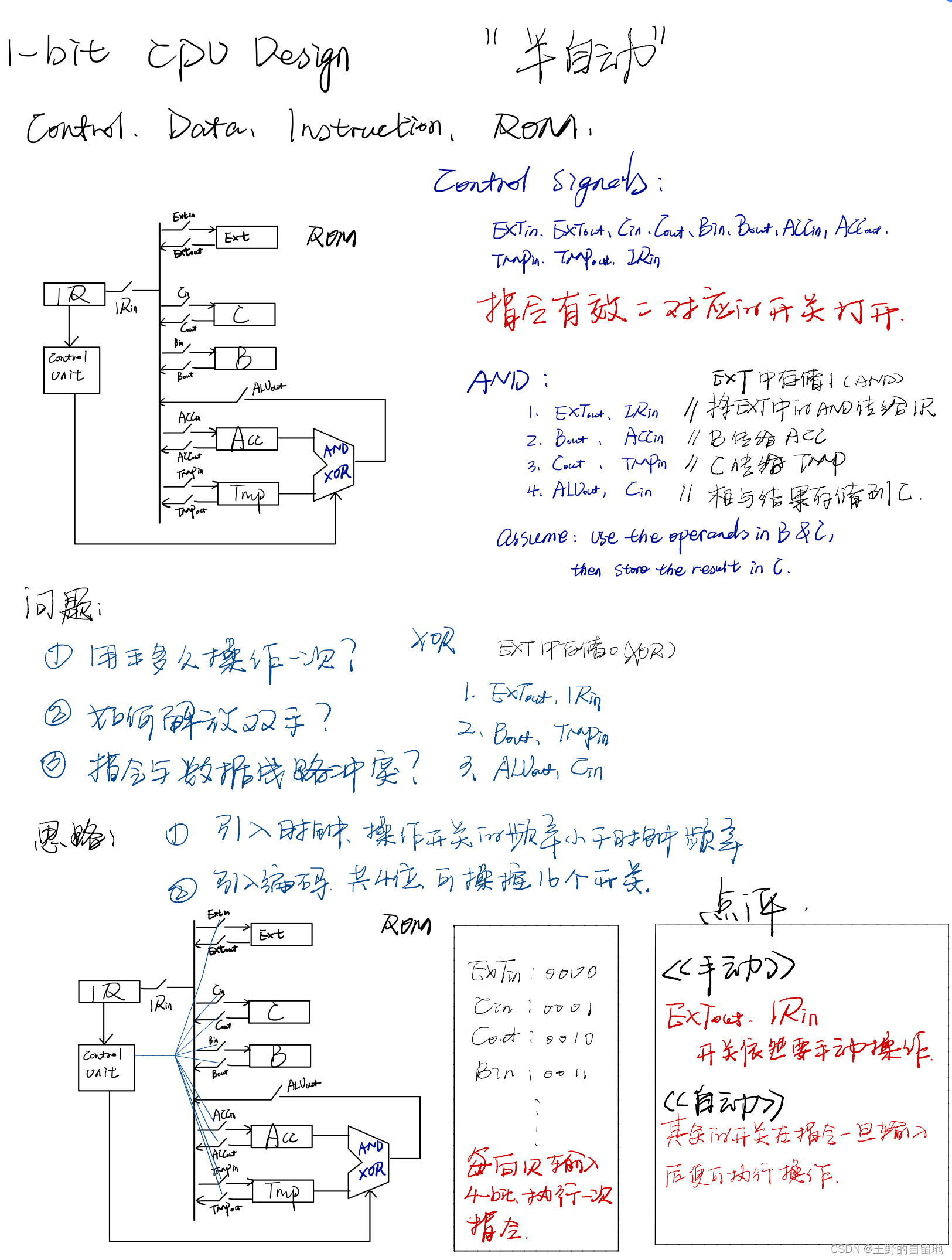

1-bit全手动处理器

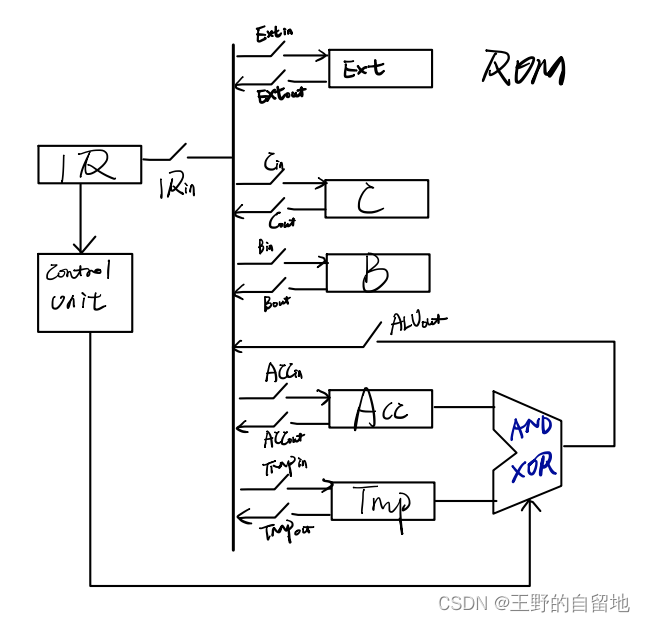

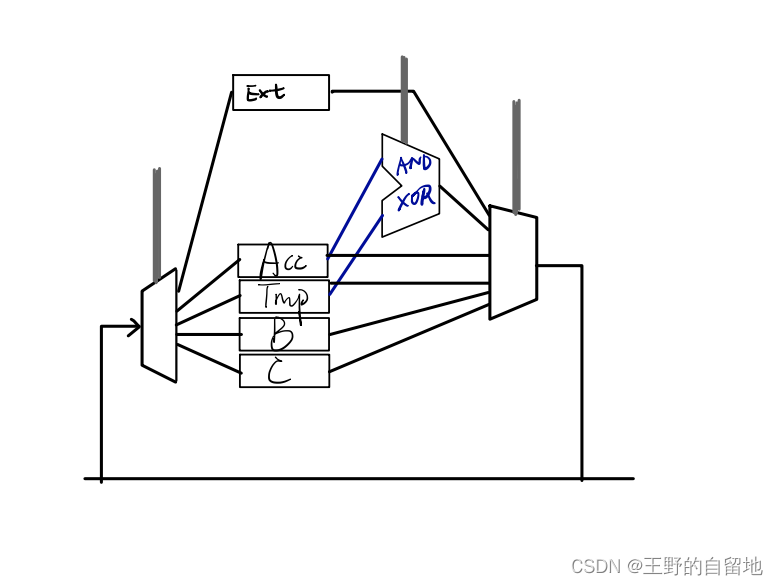

处理器架构

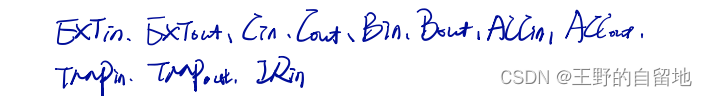

控制信号:

处理器程序(与操作)

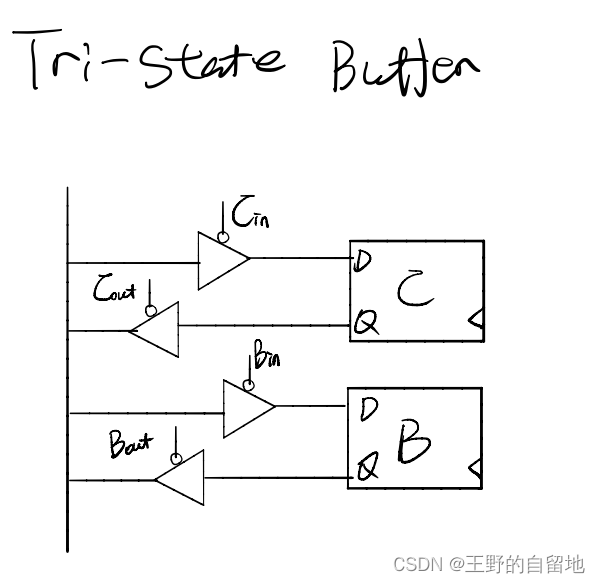

关键组件

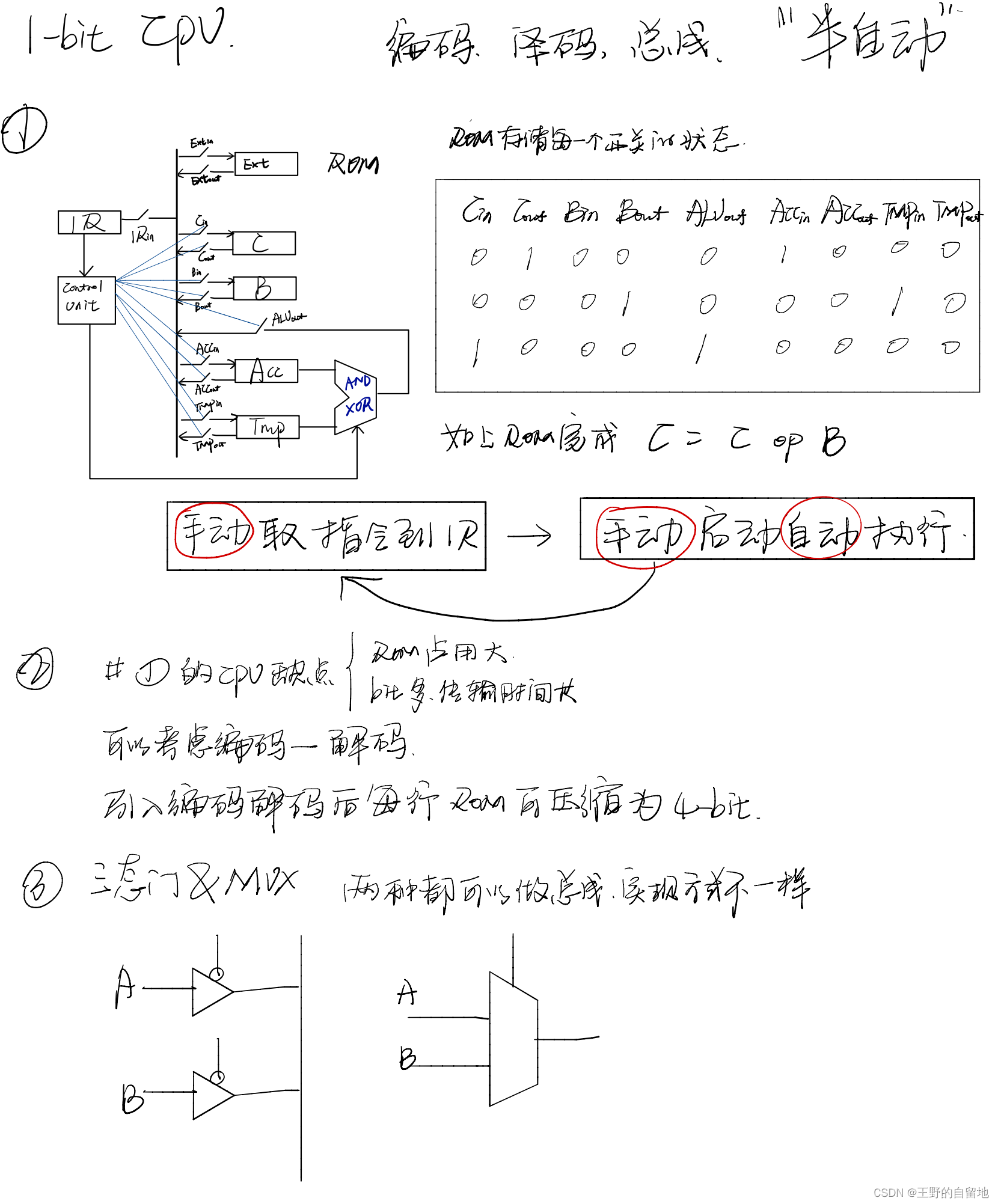

1-bit半自动处理器

1-bit全自动处理器

python语言模拟1-bit 处理器

class OneBitProcessor:

def __init__(self):

self.reg_a = 0

self.reg_b = 0

self.alu = None

def load(self, reg, value):

if reg == 'A':

self.reg_a = value

elif reg == 'B':

self.reg_b = value

def add(self):

self.alu = self.reg_a + self.reg_b

def sub(self):

self.alu = self.reg_a - self.reg_b

def and_(self):

self.alu = self.reg_a & self.reg_b

def or_(self):

self.alu = self.reg_a | self.reg_b

def xor(self):

self.alu = self.reg_a ^ self.reg_b

def execute(self, instr):

op = instr[0]

if op == 'LOAD':

reg, value = instr[1:]

self.load(reg, value)

elif op == 'ADD':

self.add()

elif op == 'SUB':

self.sub()

elif op == 'AND':

self.and_()

elif op == 'OR':

self.or_()

elif op == 'XOR':

self.xor()

print(f"ALU: {self.alu}")

def run(self, program):

for instr in program:

self.execute(instr)

# 运行上面的程序

program = [('LOAD', 'A', 0), ('LOAD', 'B', 1), ('XOR',)]

processor = OneBitProcessor()

processor.run(program)

输出结果:

ALU: 0

ALU: 1

ALU: 1

用Verilog编写1-bit处理器

module OneBitProcessor(

input clk, // 时钟信号

input rst, // 复位信号

input [1:0] opcode, // 操作码

input [1:0] dataA, // 操作数 A

input [1:0] dataB, // 操作数 B

output [1:0] result // 操作结果

);

reg [1:0] reg; // 1-bit 寄存器,存储一个位

reg [1:0] alu; // 1-bit ALU,存储运算结果

always @(posedge clk) begin

if (rst) begin // 复位操作

reg <= 2'b0; // 将寄存器清零

alu <= 2'b0; // 将 ALU 清零

end else begin

case (opcode) // 根据操作码执行操作

2'b00: alu <= dataA & dataB; // AND

2'b01: alu <= dataA | dataB; // OR

2'b10: alu <= dataA + dataB; // ADD

2'b11: alu <= dataA - dataB; // SUB

endcase

reg <= alu; // 将 ALU 结果存储到寄存器中

end

end

assign result = reg; // 输出寄存器的值作为操作结果

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?