主持人按下复位键进入抢答状态,某人抢答时,其他路封锁,译码显示模块送出信号给数码显示模块,从而显示出抢答成功组好,并一直保持到主持人下一次抢答开始。

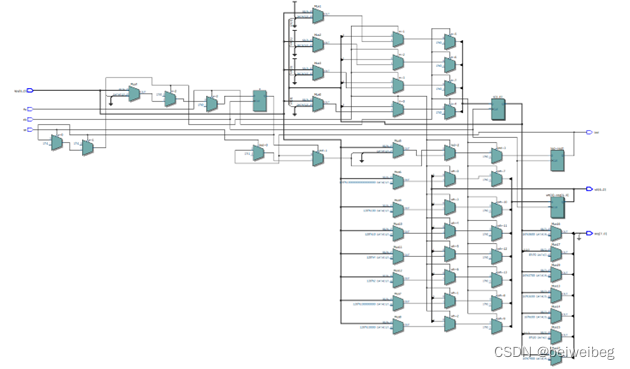

顶层电路图

逻辑电路图:

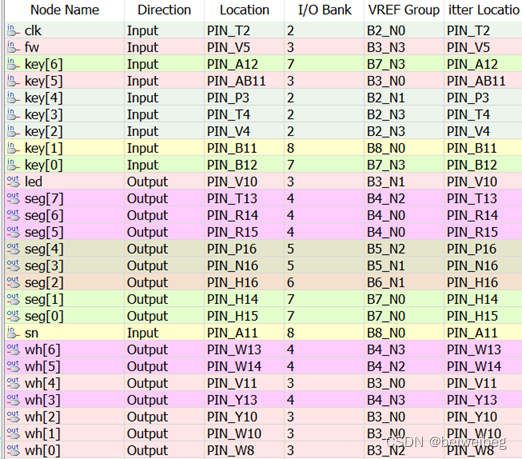

引脚分配:

部分代码

entity decide7 is

port(key:in std_logic_vector(6 downto 0); %七名选手

sn:in std_logic; %允许抢答位

fw:in std_logic; %复位键

clk:in std_logic; %时钟信号

seg:out std_logic_vector(7 downto 0); %七段数码管

wh:out std_logic_vector(6 downto 0); %七盏小灯泡

led:out std_logic ); %允许抢答标志灯

end decide7;

architecture a of decide7 is

signal sel1 :std_logic_vector(2 downto 0);

-----------------------------------------------------------------

begin

process(key,clk)

variable n:integer range 0 to 10;

variable x:std_logic; %变量x充当锁存的功能

begin

当变量x=0时,并且使能键为低电平(被摁下)时,将使能标志位点亮,即置led=1,x=1;

当变量x=1时,根据s2~s8不同的抢答情况会进入不同的case语句。首先根据抢答情况,将变量n赋值为抢答组号,并将x置为0、led置为0。并且点亮对应的灯泡。

该代码中,x=0并且sn=0时,会将led和x置为1;此时可以抢答,一旦进行了抢答的动作之后,又会将x置为0,但此时sn不等于0,即不允许抢答,此时再摁其他的键不会有下一步的动作。达到了锁存的功能。

if CLK='1'AND CLK'EVENT then

if x='0'then

if sn='0'then led<='1'; x:='1';

end if;

end if;

if x='1' then

case key is

when "1111110" =>n:=1;x:='0';led<='0';wh<="0000001";

when "1111101" =>n:=2;x:='0';led<='0';wh<="0000010";

when "1111011" =>n:=3;x:='0';led<='0';wh<="0000100";

when "1110111" =>n:=4;x:='0';led<='0';wh<="0001000";

when "1101111" =>n:=5;x:='0';led<='0';wh<="0010000";

when "1011111" =>n:=6;x:='0';led<='0';wh<="0100000";

when "0111111" =>n:=7;x:='0';led<='0';wh<="1000000";

when others => wh<="0000000";

end case;

end if;

---------------------------------------------------------------

复位键(s9)被摁下,会将led(使能标志位)、x、n、灯泡都置为0。

if fw='0'then wh<="0000000";

n:=0;led<='0';x:='0';

end if;

end if;

变量n代表了要在数码管上显示的数字,下列case为输入字形码在七段数码管上显现。

case n is

when 1 =>seg<="00000110";

when 2 =>seg<="01011011";

when 3 =>seg<="01001111";

when 4 =>seg<="01100110";

when 5 =>seg<="01101101";

when 6 =>seg<="01111101";

when 7 =>seg<="00000111";

when others => seg<="00000000";

end case;

end process;

end a;

531

531

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?