上一期我们学习了DDR4的基础知识(没有学习的可以点击下面连接进去学习一下,还话是有必要知道基础知识才能进行下面的过程)https://blog.csdn.net/bingbang0703/article/details/132403454![]() https://blog.csdn.net/bingbang0703/article/details/132403454

https://blog.csdn.net/bingbang0703/article/details/132403454

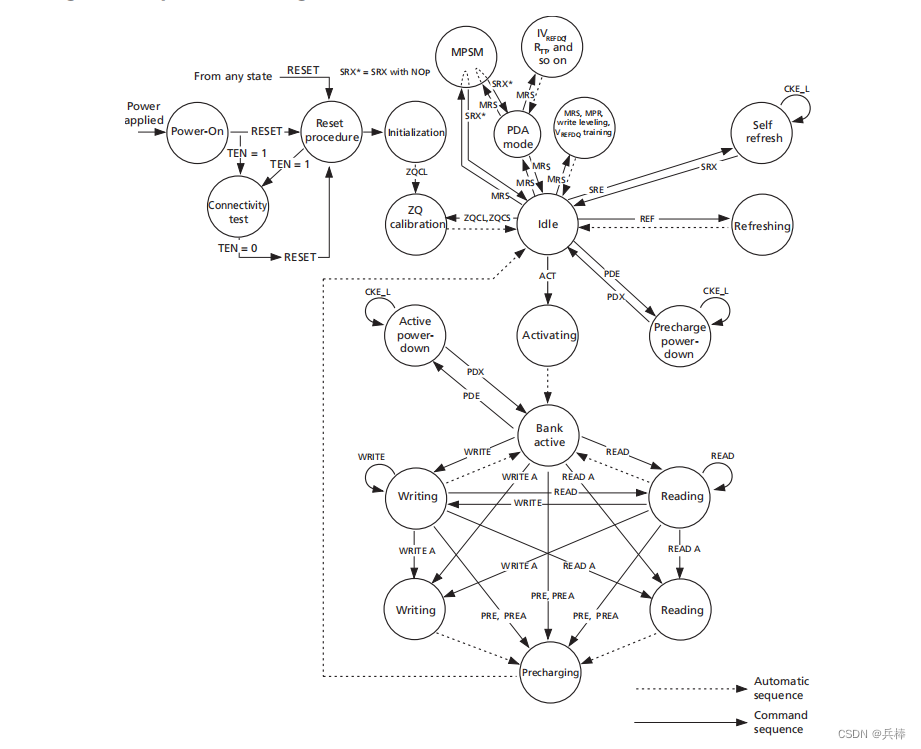

一、DDR4运行状态机

实线的是命令输入导致,虚线是如果没有命令自动运行的。

如图看,可以知道电源(power applied)接进去了会进行刷新(reset procedure),刷新结束再经过处理才会到达idle状态,此时我们要注意的就是ACT命令到来,使其形成激活状态(Activating

)才可以让DDR4进行读写操作,激活之后就进入bank激活,最终开始写操作和读操作。

二、激活DDR4

那么问题就来了,激活怎么进行?

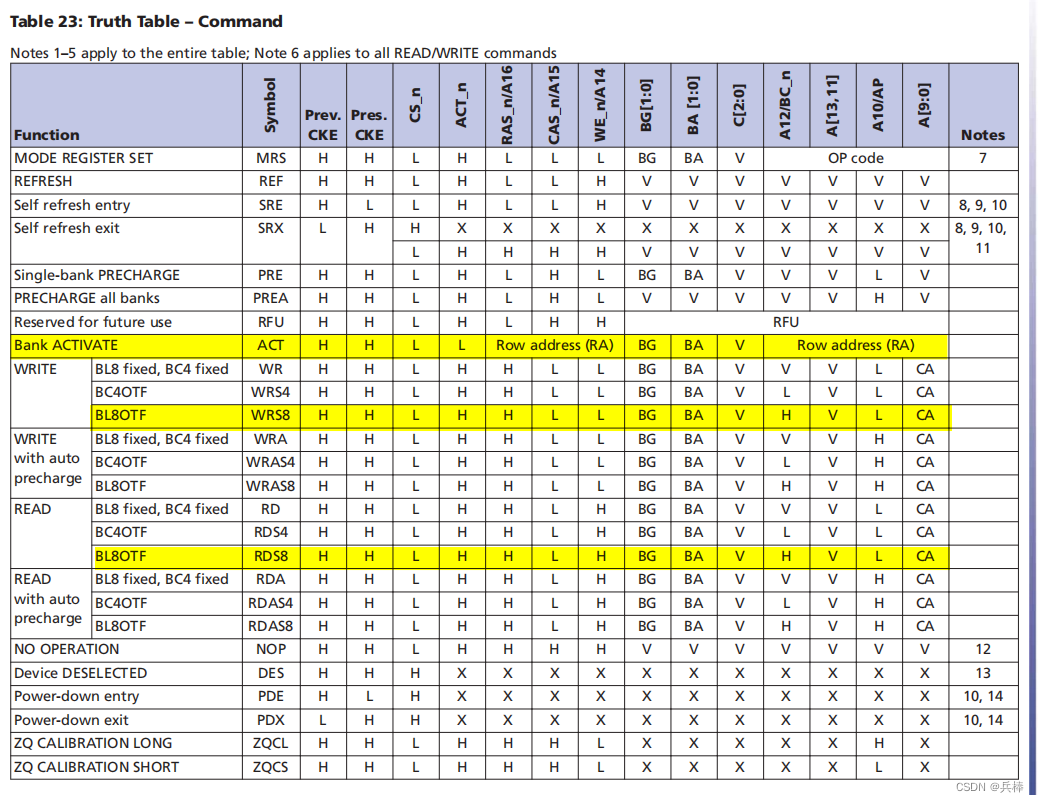

这是我们就要去看DDR4芯片手册手册上的激活信息了

这段话的理解还是比较简单,但要结合命令真值表结合起来看哦!

可以看到黄色标记的bank activating,这时候就是激活命令了,它的基本组成就是app_addr、app_en、app_wdf_end以及app_wdf_wren,这些后续会进行讲解,你只要知道激活命令的形成就行,以及激活命令要定义好BG、BA、地址的位置就行。

还有两个黄色的标记是针对读写的连读数,也就是一次性8个连读连写,这对刚入学习的人,了解一下就行。

三、DDR4 mig IP核调用与学习

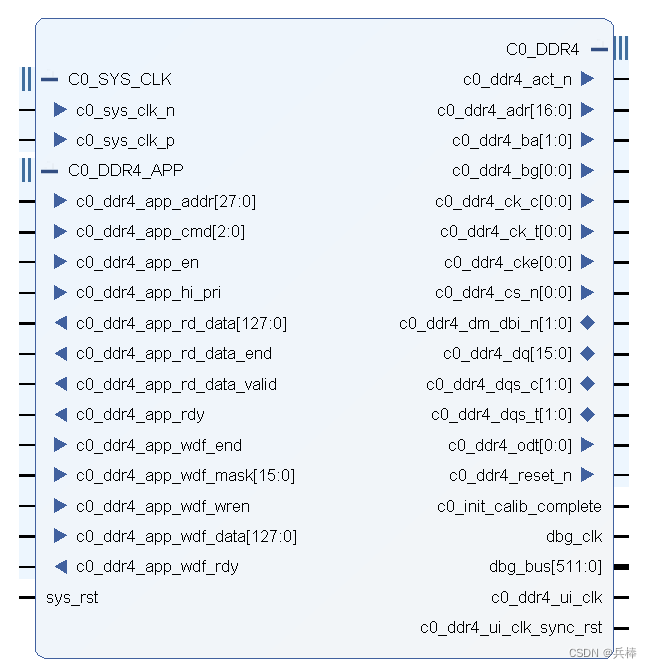

在PL端我们可以直接使用DDR4不需要去PS端运用,那先来了解DDR4 mig IP核的引脚

右侧的接口在上一期的学习当中已经有很多的讲解了,这里就不再多言。(而且右侧端口不需要我们编写,我们要编写的只是左侧的)

在DDR4中由于ddr的升级,要求DDR的安全性和速度,就使用到了差分时钟。

c0_sys_clk_p:正接口

c0_sys_clk_n:反接口

c0_ddr4_app_addr:用户地址,主要组成是存储组(BG)、bank(BA)、行(row)、列(column),怎么进行组合就要看你在IP核中的配置了。

c0_ddr4_app_cmd:命令,000表示写,001表示读。

c0_ddr4_app_en:请求命令,无论是读还是写都需要进行请求。

c0_ddr4_app_hi_pri:输入保留,一般都置0.

c0_ddr4_app_rd_data:读的数据。

c0_ddr4_app_rd_data_end:读的最后一个数据。

c0_ddr4_app_rd_data_valid:读有效。

c0_ddr4_app_rdy:用户端准备信号。

c0_ddr4_app_wdf_end:写数据最后一个数据。

c0_ddr4_app_wdf_mask:掩码,和数据线dq对应,高电平表示该位无效。一般直接全部置0.

c0_ddr4_app_wdf_wren:写使能。

c0_ddr4_app_wdf_data:写数据。

c0_ddr4_app_wdf_rdy:接收缓冲端返回信号,高电平表示已经准备好了,可以发送数据过来。

以上就是用户端的接口各自的含义。

下面就是怎么去调用DDR4 mig IP核。

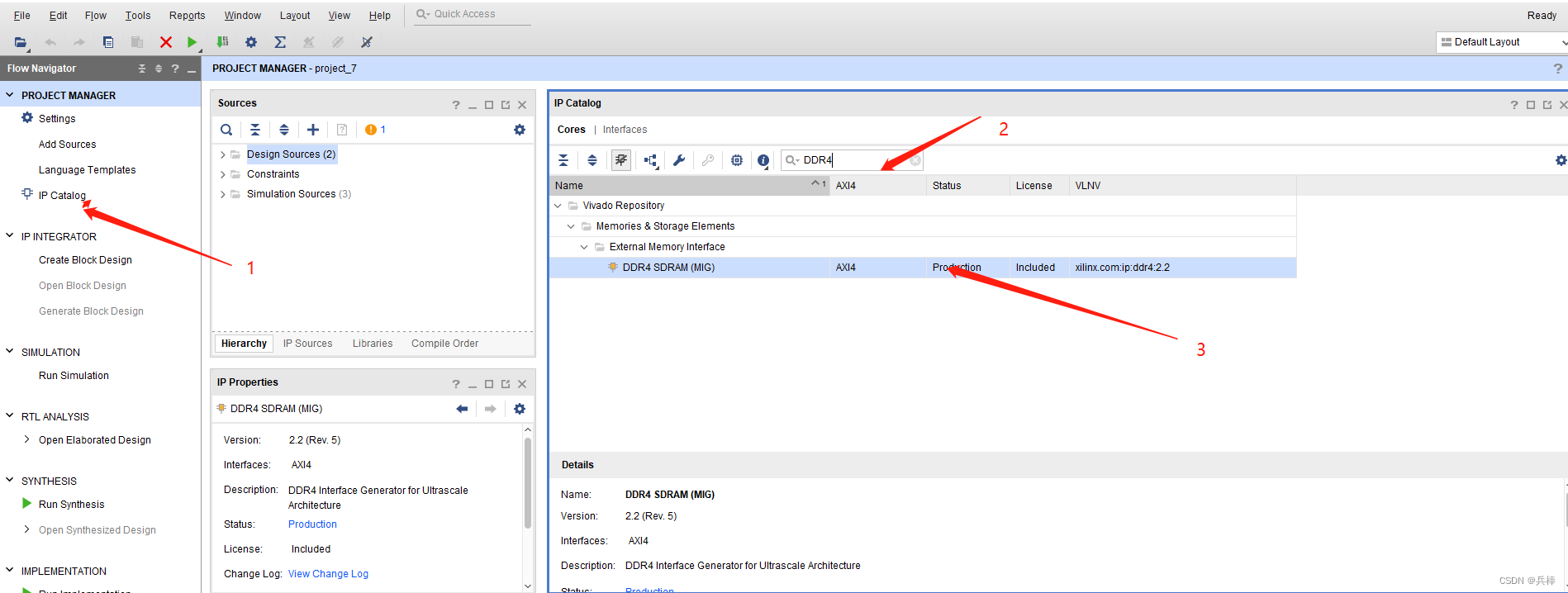

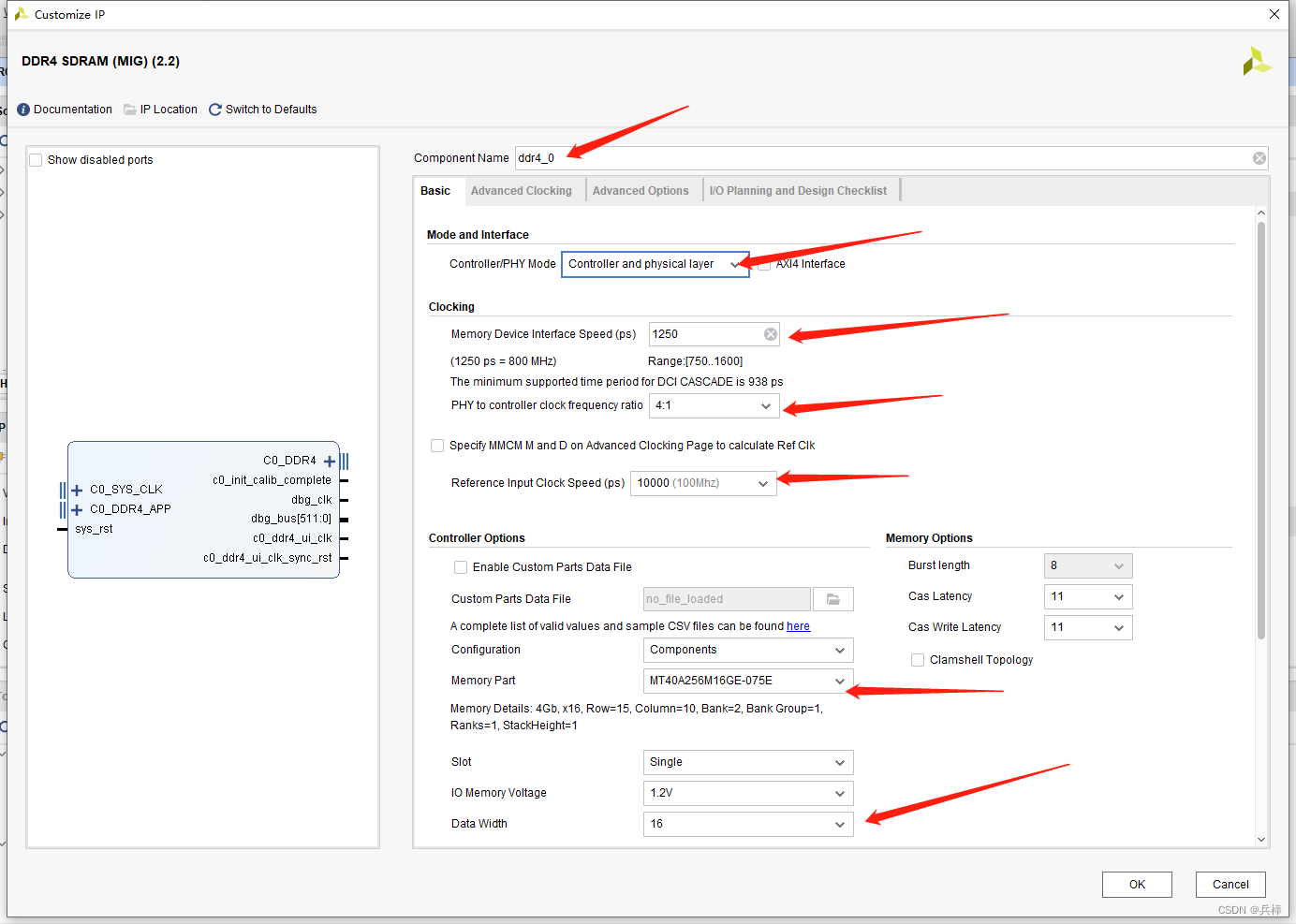

四、调用DDR4 mig IP

第一步

第二步

1.IP名称

2.选择正常模式就行,后面的AXI4不用勾选,没用到AXI4协议接口

3.时钟频率,看你自己调用,最终也不会影响什么,因为时钟是你输入差分时钟进去的。

4.时钟比,因为你输入进去差分时钟,只是给DDR4这个mig控制用,不是给DDR4,经过选择比进行换算,给出一个用户端使用时钟,想往里面 写数据和读数据时就是用这个用户时钟。

5.参考时钟:建议对号入座,选择你输入的时钟大小为参考,否则在时钟约束的时候会出现约束大小的错误。

6.选择信号,选一个和你的ddr型号差不多的就可以,不一定要全部一样

7.选择数据位宽

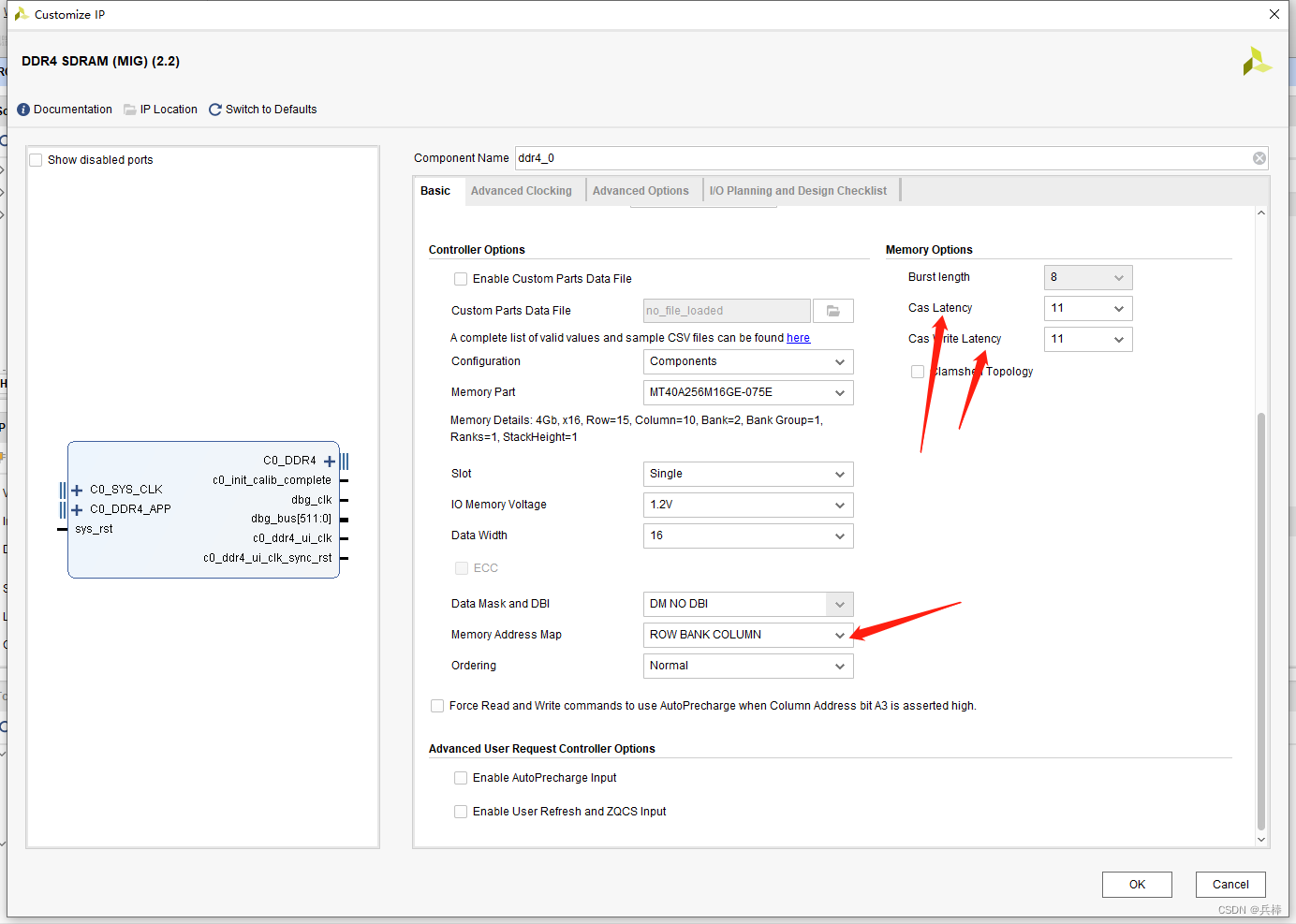

第三步

1.选择app_addr地址组合,根据你的需要进行选择就行。

2.选择CL时间:一般只用在读延时上,经过延时读出数据。

3.选择写延时:写入数据时用户端和DDR4端会有一段数据缓冲时间,这就是写延时。

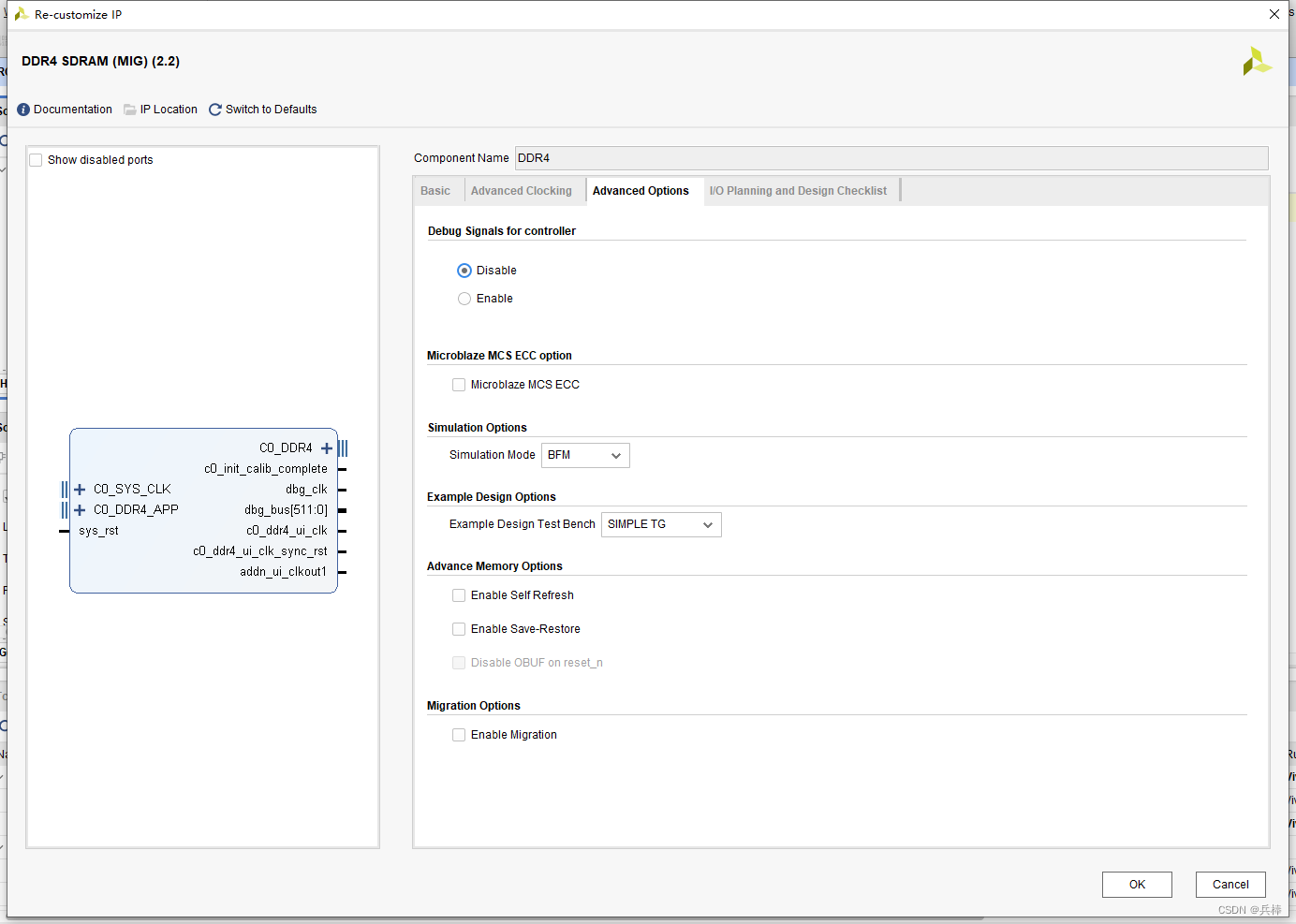

Debug Signals for controller :控制器的调试信号,默认,处除非你会调电路

Simulation Options:默认选择BFM

Microblaze MCS ECC option:不选,一般用不到ECC。

Unisim仿真通常是指对电子电路的仿真。Unisim是Unisim7电路模拟软件,它是一种强大的电路模拟工具,可以用于电路分析和设计。使用Unisim进行电路仿真,可以帮助工程师更好地理解电路的行为,并验证电路设计的正确性。

BFM(Block-based Flow Manager)仿真则可能指的是针对特定软件或系统模块的仿真。BFM是Xilinx公司Vivado软件套件的一部分,用于管理FPGA设计中的高级块流。通过BFM仿真,可以验证这些高级块在系统中的性能和功能。

具体来说,Unisim仿真和BFM仿真是针对不同类型系统的仿真,前者针对电子电路,而后者针对特定软件或系统模块。

Example Design Options:示例设计,选SIMPLE TG,另一个用不到而且很复杂。

后面那几个选项更遇不到,都直接默认就行了

第四步

直接点ok就行,其它一般用不着。

以上就是基础知识,下期学习读写时序和仿真。

2127

2127

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?