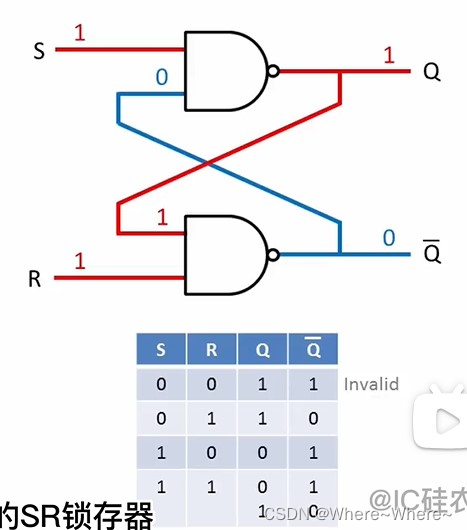

其实选择与非门当做构成SR锁存器的基本逻辑电路是有漏洞的,所以才导致了后续的都为低电平的时候,Q和非Q都是亮起的。但是我们设计的初衷是:Q和非Q是互斥的,是不能同时亮起的,且为了达到这一点,要使得其中两者中的任意一个发生了变化,那么这个变化都要正反馈给另外一个,以此达到通知的目的,这就是为什么最后SR锁存器中,最后输出的结果为另外一个输出的输入,我们都知道一开始有两个原始输入来控制这两个输入,那么这个原始输入和另一个结果的输出的输入是什么关系呢?这就设计了逻辑推导。首先因为Q和非Q是互斥的,比如当Q是亮的时候,那么这个时候一定要保持非Q是暗的,即*(原始输入R,Q输入) = (0,1)(1,1)通过一个逻辑电路一定是低电平的,且当Q时暗的时候,非Q一定是亮的,即(1,0)(0,0)通过一个逻辑电路一定是高电平,这样的逻辑电路还真不好找,但是发现其中逻辑与非门可以满足其中的三个,之后其中的(0,1)不能满足,这样的话,那只能将这种情况人为的设置为无效的条件,但是也为后续这种锁存器的不好用埋下了伏笔,故而就有了锁存器的不断改进,最后到了沿触发式D触发器,才是真正解决了既能锁,又没有特殊情况的问题。

———————————————————————————————————————————

-

SR锁存器到底是什么?其实SR锁存器有两种方式,一种是与非门的锁存器,一种是或非门的锁存器,我们只讲与非门的锁存器,与非门构成的SR锁存器是是一个以低点平为信号的锁存器,其中S,R的初始状态都是高电平的,其中的S是set是设置Q的,其中的R是reset是设置Q非的。当如果S,R一开始都是高电平的话,那么其中的Q和非Q都是不确定的,因为这个结构是循环的,上一个与非门的结果会通过正反馈来控制下面的与非门(相反也是一样的),所以当两个都设置为为1的时候,其中的Q和非Q到底谁亮是取决于上次电路的结果的。当S,R都处于初始位置的时候,即都是高亮的时候,这个时候就需要一个发号施令进入低电平来行使对应的功能,比如其中的R变成低电平的话,那么就会让非Q变亮,而Q会被暗淡下来,为什么呢?是有一个过程的,其中R是通过低电平来重置Q的,让其回到非Q的状态,而由于非Q是和Q是相斥的,所以这个时候就得有一条电路进行正反馈,通知Q,要他变为低电平的(这个时候的S是始终都是亮的,因为这个是正常的状态,还没有轮到S来行使功能),这个时候不管R怎么变化,那么其中非Q的值也不会变化,因为其中Q的反馈是低电平的,无论R怎么变化,也达不到两个都是高电平的状态,这个电路设计的非常巧妙,难以用基本的逻辑来从0-1,所以记住即可,因为这个结构会在后面经常使用。

所以总的来说,在与非门的SR锁存器中,S控制和其平行的Q的信号的,使用低电平控制;而R是控制与其平行的非Q信号的,使用低电平控制。记住,高电平是S和R的基本状态

-

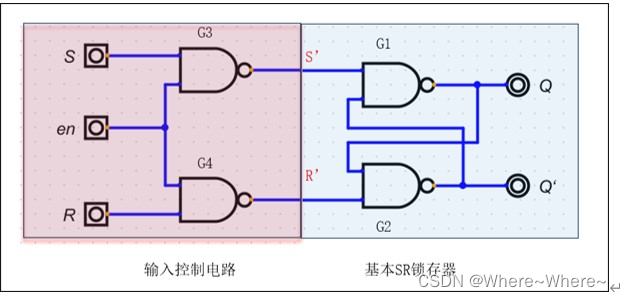

既然我们有了一个基本的锁存器,能够锁定住在Q中的状态,那么我们能够设置一个开关,来决定是否动用这个锁存器呢?可以的,只需要引入一个EN就好了,这个就是开关。

那为什么这样设计呢?我们需要的是,当我们开启EN的时候,那么就可以正常的去控制的,否则的话是控制不了的。那怎么设计呢?我们知道与非门的SR锁存器是通过低电平控制的,那么只要控制其在EN没有打开的时候,一定输出不了低电平就好了,也就是说,当EN是低电平的时候,S和EN的输入永远都是高电平,即EN,S = (0,1)和(0,0)都是表示高电平,同时保证当EN是高电平的时候,其中的(1,0)(1,1)存在低电平,或电路不可以,与电路也不可以,这个时候与非刚好可以,那么这个时候,就可以在S和EN之间建立一个与非门来控制电路了,但是由于这个时候是(1,1)输出的是低电平从而控制了整个锁存器,所以这个时候的带EN的锁存器,从原来的锁存器由低电平控制,变成了现在的由高电平控制了,即当EN通的时候,S的高电平控制Q的置位,Q的高电平控制非Q的置位。

-

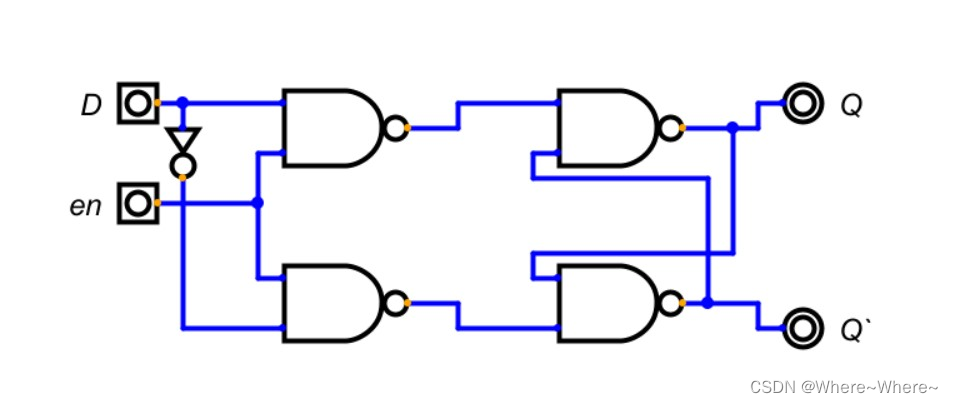

是不是上面的锁存器就很厉害了呢?其实并不是,因为我们在设计之处,是想让Q一定是位非Q的反面的,两者是不能同时存在的,但是上面的锁存器中,当普通的SR锁存器S和R都是低电平的时候,会出现两个Q和非Q都是亮的情况,那么这个和我们原来的初衷是相反的,是无效的。为什么说和我们的初衷是相反的呢?这是因为当S,R都为低电平的时候,我们确实存储了一个高电平的Q,但是当我们的S,R同时变化成高电平的时候,那么这个时候就会出现竞争,因为率先达到与非门进行计算的就一定会让对应的Q或者非Q变成低电平从而影响到另外一个Q或者非Q,那么这个时候,Q或者是非Q的输出就非常地不确定,可能是Q亮,也可能是非Q亮,因为其中一个输出一旦熄灭了,那么另外一个就一定不可能熄灭了,因为被熄灭的这个正反馈锁住了。与其说是有这种情况存在,不如说是这种结构就导致了这种情况的存在,那么唯一的办法就是改变这种结构,即不让其有两个输入,只有一个输入就好了,同时一个输入表示两个不同的状态,就避免了S,R同时是一种状态了

这个就是大名鼎鼎的D锁存器(其中的Q是跟随D变化的),其中的输入状态还是高电平来控制Q亮,D高电平的话,那么Q亮就进入输出存储。且一定锁住(因为没有另外一个输入R来影响了,只有一个D来影响,身兼两职,且D是稳定的),且不会发生下一步Q和非Q的不确定。

-

那是不是这种方式就很完美了呢?并不是的!我们锁存的条件是EN是开启的,且D高电平Q才能输入锁存,但是D一旦关闭的话Q就没了,比如D是低电平的话,那么Q就重置了,变成了非Q,即在EN开启的时候,Q的是否是亮的,即Q是否能锁住,取决于D本身是否是稳定的,如果D是不稳定的,那么其中存储的Q也就是不稳定的,所以有没有一个东西,让D高亮锁存的一瞬间就让Q脱离D的关系呢?这个一瞬间怎么来表示呢?记不记得我们前面提到过的需要等到EN高亮的时候,D才能存进去Q,存的条件是EN是一直高亮的,也就是说通道一直是开着的,所以D波动才能影响到Q,那么如果我们让通道不是常开的,我们设置一下,让通道快要开启的时候,这个时候让D锁存,然后等到EN高亮的时候,反而D锁存不了呢?也就是在EN从低电平到高电平拉高的一瞬间让其存进去呢?有的!看下面的电路!

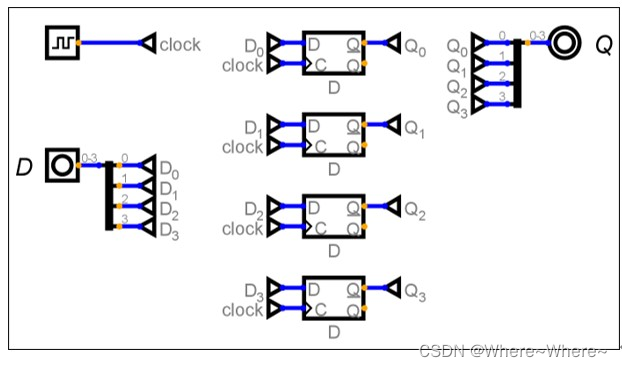

怎么分析呢?这样的电路设计的太巧妙了!其首先是让D是处于一个亮的状态的,同时中间使用了一个非门,使得就算EN的通道没有开放的话,那么也能让信号输出到第一个D锁存器的Q口,那么这个时候,就得等通道的信号了,通道的信号来了之后,同时第二个D口连接着上一个的Q口,这个时候就能里面 缩进去,同时由于通道已经打开,导致第一个锁存器无法正常输出Q亮,所以就堵住了前往后续的道路,故这时无论怎么变化D(前提是其中的C时钟是一个EN常亮),里面锁住的信息都不会发生改变。那么这样边沿触发的D触发器才是真正能隔绝外界干扰的锁存器,即一个bit的锁存器,那么多个这样的锁存器拜访在一起的话,就变成了一个寄存器,非常的nice.

使用的具体功能:只有当输入的EN是上升的时候,D输入的话,那么Q才会正常锁住,之后EN常亮的时候,D不管怎么变化的话都不会改变其中的Q了。那如果D不亮的时候,这个时候也得等到EN的上升沿的时候,Q才会熄灭,总之这样的设计就是在D锁存器上加了一个只有在上升沿中才可输入的功能。如果其中的EN是时钟的话,D亮上升沿才输入Q亮,D暗等到上升沿才变暗。

所以最终的效果是:下面的通道是由时钟控制的,每秒都会输入多少次高电平,一旦我们输入了D之后呢,那么数据就已经存进去了,之后无论D怎么变化之后,里面的值是不会改变的。

——————————————————————————————————————————

有两个输入的锁存器的输出,都有机会被另外一个输入而重置,即当S让Q亮了之后,S之后再怎么变化都不会影响Q了,所以当S处在原始姿势的时候(原始的姿势,SR锁存器和带EN的SR锁存器不太一样,具体见上文),当R变化的时候,那么Q熄灭,非Q亮起。但是等到后续再D锁存器中,却只被D控制,同步亮和熄灭,但是等到边沿触发式的D锁存器中,又回到了最初的样子,当D输入之后,之后再怎么变化,那么也不会影响里面的Q。

4306

4306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?