追根究底

cataol@hotmail.com

欢迎转载,但请保留作者信息

这两天在学习Linux驱动相关的资料,在这里做一下学习笔记,以便以后查询。以前也有做过工作方面的知识整理,可惜在硬盘里零零散散,甚至有些都被删掉了,唉。

首先我们大概看一下硬件大概架构:

ARM<-AHB->Memory Controller<-Host bus->LCD controller<-RGB->LCD

| ARM SOC | LCDC | LCD |

从这里我们可以知道要完成对LCD的控制,需要对ARM SOC内部controller进行配置来match LCD controller的bus timing,完成地址的mapping。配置LCD controller host bus工作在ARM SOC bus方式。配置LCD controller需要使用的LCD的timing。

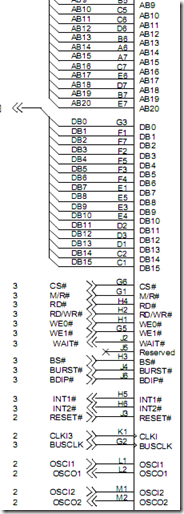

从S1D13515 EVB schematic看一下它的电路,我们主要关心的是power,reset,clock input和host bus interface。

power和reset有on和off的sequence,HW设计或者软件设计遵循即可,Clock使用CLKI1连接。Host Interface方面S1D13513支持Intel 80,motorola 68等其他专用总线,使用CNF pin来配置总线类型。

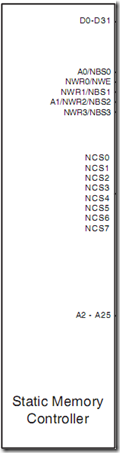

9G20提供EBI bus供外部总线设备连接,包括SDRAM,Static memory controller,NAND FLASH contoller等。SMC是一个AMBA AHB设备,它在SOC AHB master和SM device之间充当接口,可以连接访问SRAM,NOR FLASH等设备。这里我们显然就选择SMC接口来连接S1D13513。

熟读SMC datasheet,对比S1D13513的host bus interface,可以确定使用Intel 80 type bus interface实现两边总线连接。然后就是配置S1D13513的Bus类型,根据S1D13513的bus timing来计算和配置SMC的register设置了。这就是一些简单的计算工作了。

附:Intel 80 type1,type2和Motorola 68 bus interface:

共同点,

都有Addr,Data,CS pin。

区别,

Intel 80 type 1:RD/WR/UBE/LBE。Read,Write,Upper byte,lower byte

Intel 80 Type 2:RD/WEU/WEL。Read,Upper byte write,Lower Byte enable

Motorola 68:RW/UDS/LDS。Read/Write,Upper data strobe,Lower data strobe

Intel80,Motorola68与其他一些bus interface的差异主要体现在其他interface需要有个外部时钟pin来同步。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?