硬件环境

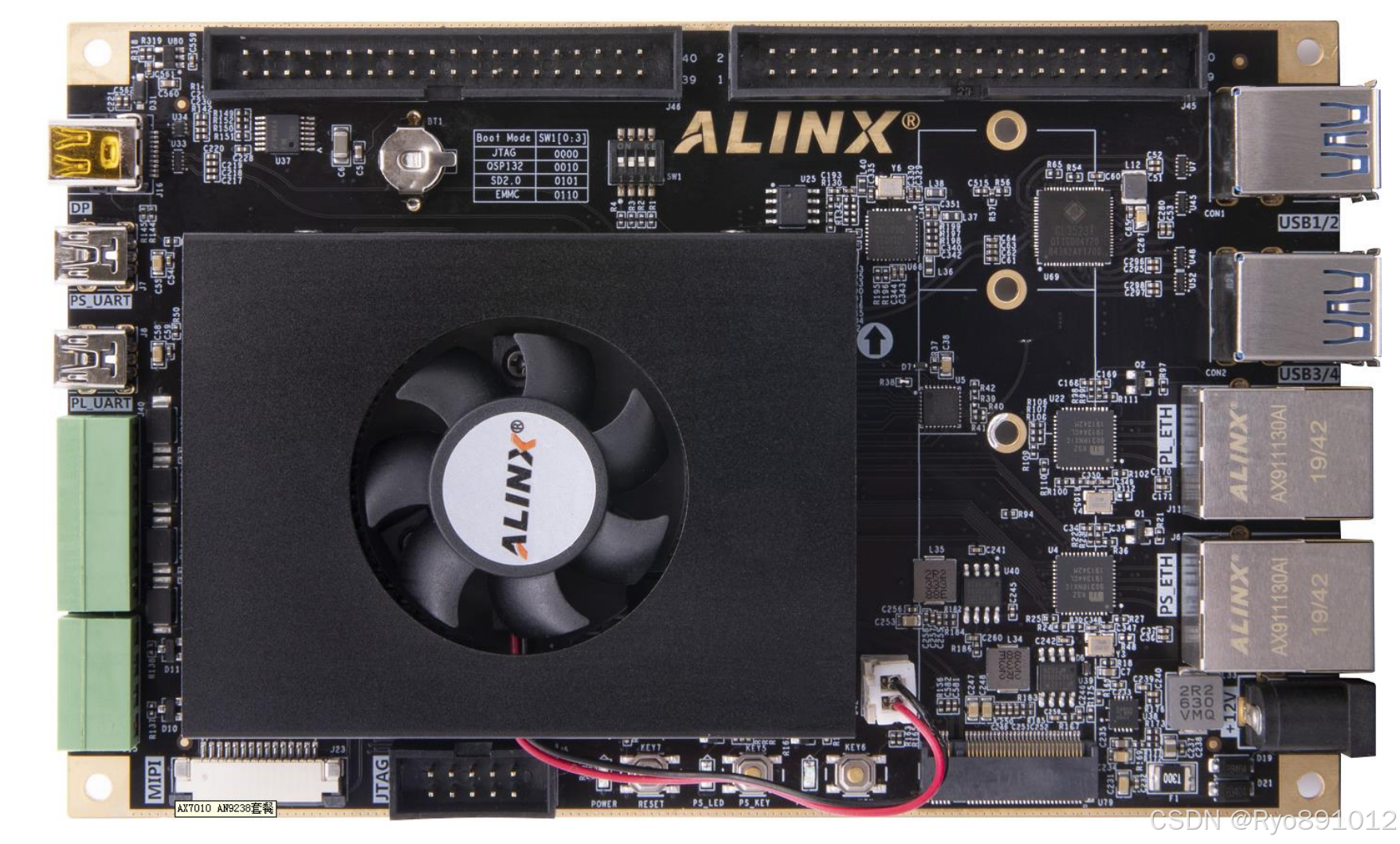

我这次学习Ultrascale+ MPSOC开发,是基于ALINX的AXU4EV-E开发板。开发板配套了很多教程,第一份是纯FPGA开发的一些教程,由于FPGA开发有基础,就先不管了,先搞PS+PL联合开发。

工程建立

好了,万事开头难,这就来了。听说PS可以单独运行,我们就先搞一个串口打印Hello world。

但是,即使是只用PS端的ARM,还是TMD得新建一个PL工程,先别管为毛吧,跟着教程做。

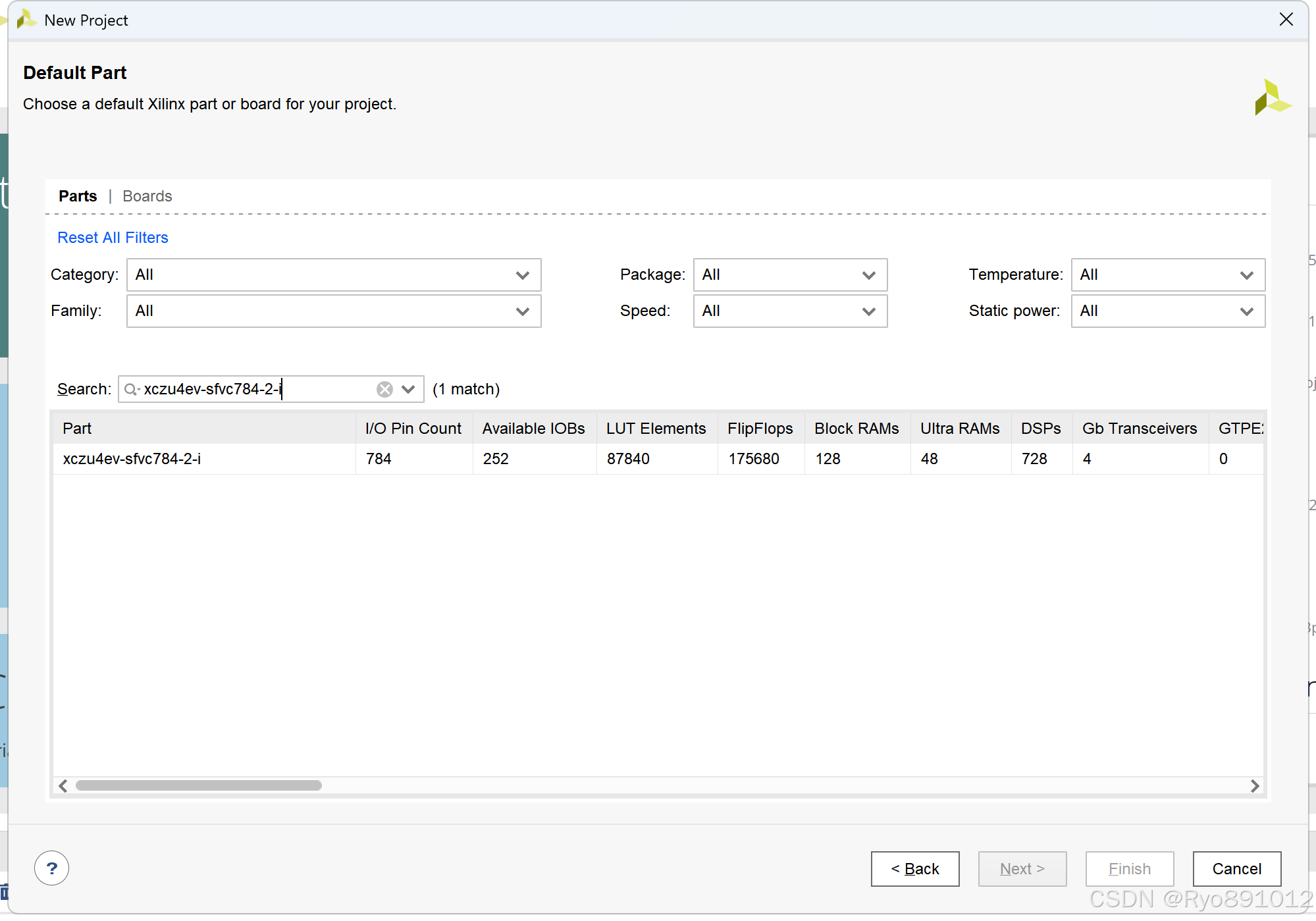

1、打开vivado,新建工程

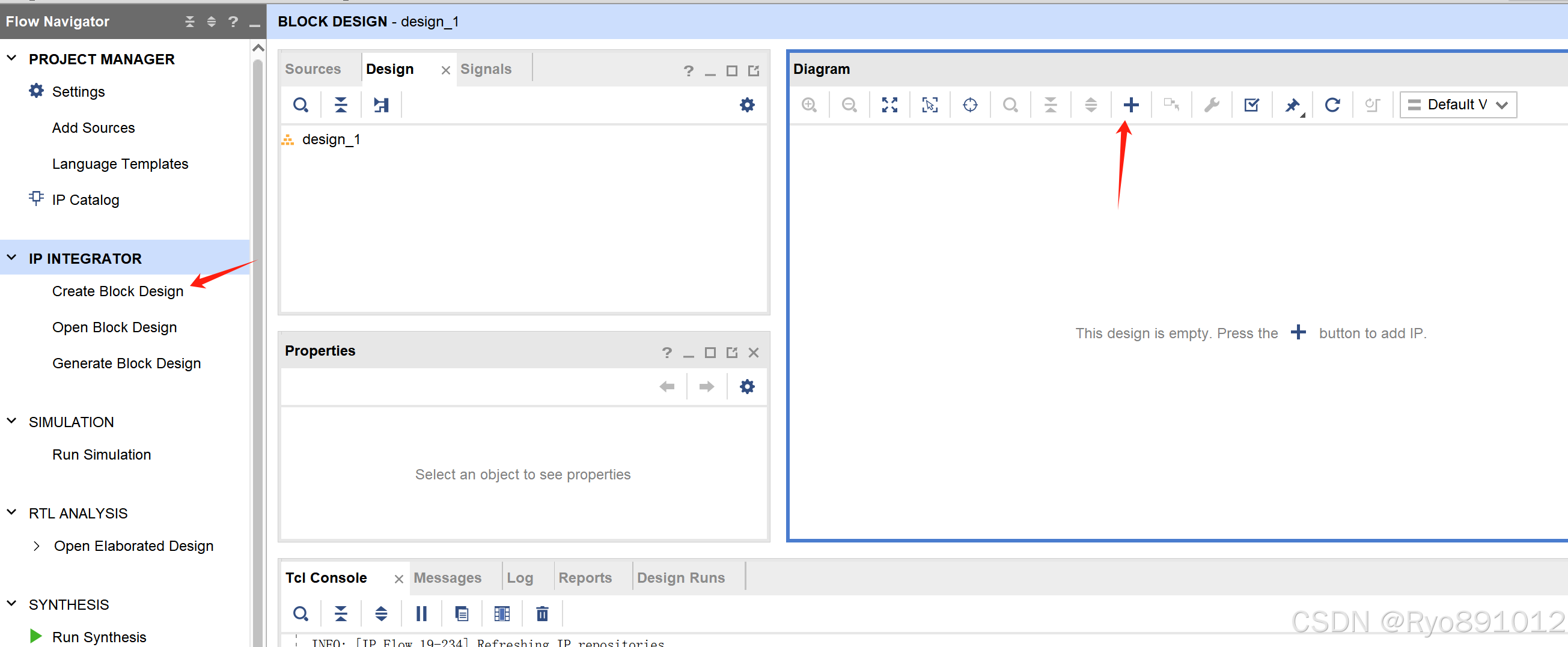

2、然后建BD

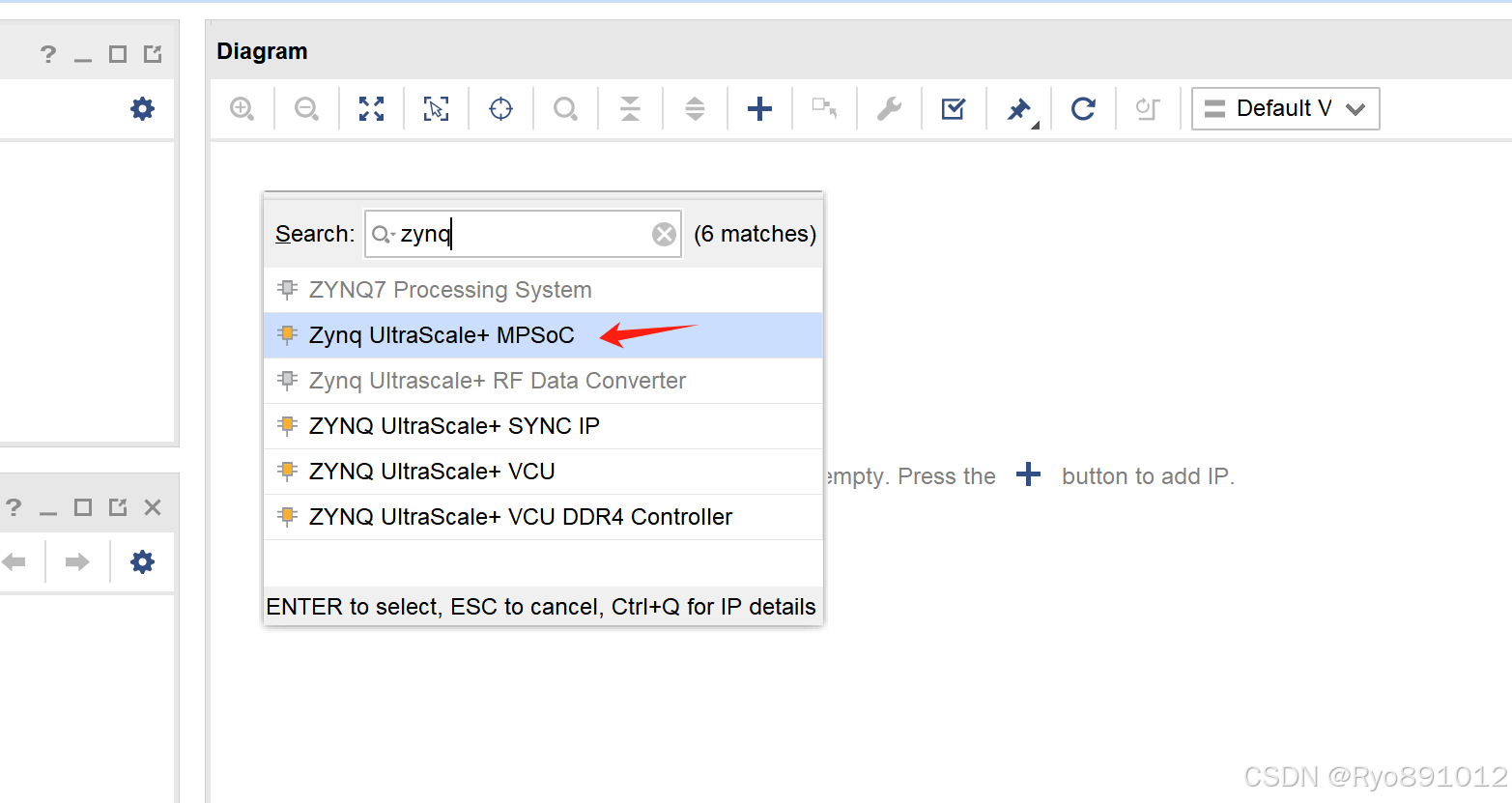

点击右边的Create Block Design,新建一个BD,然后点击+号或者右键点击空白处,搜索zynq,新建一个MPSOC的IP:

3、配置zynq MPSOC

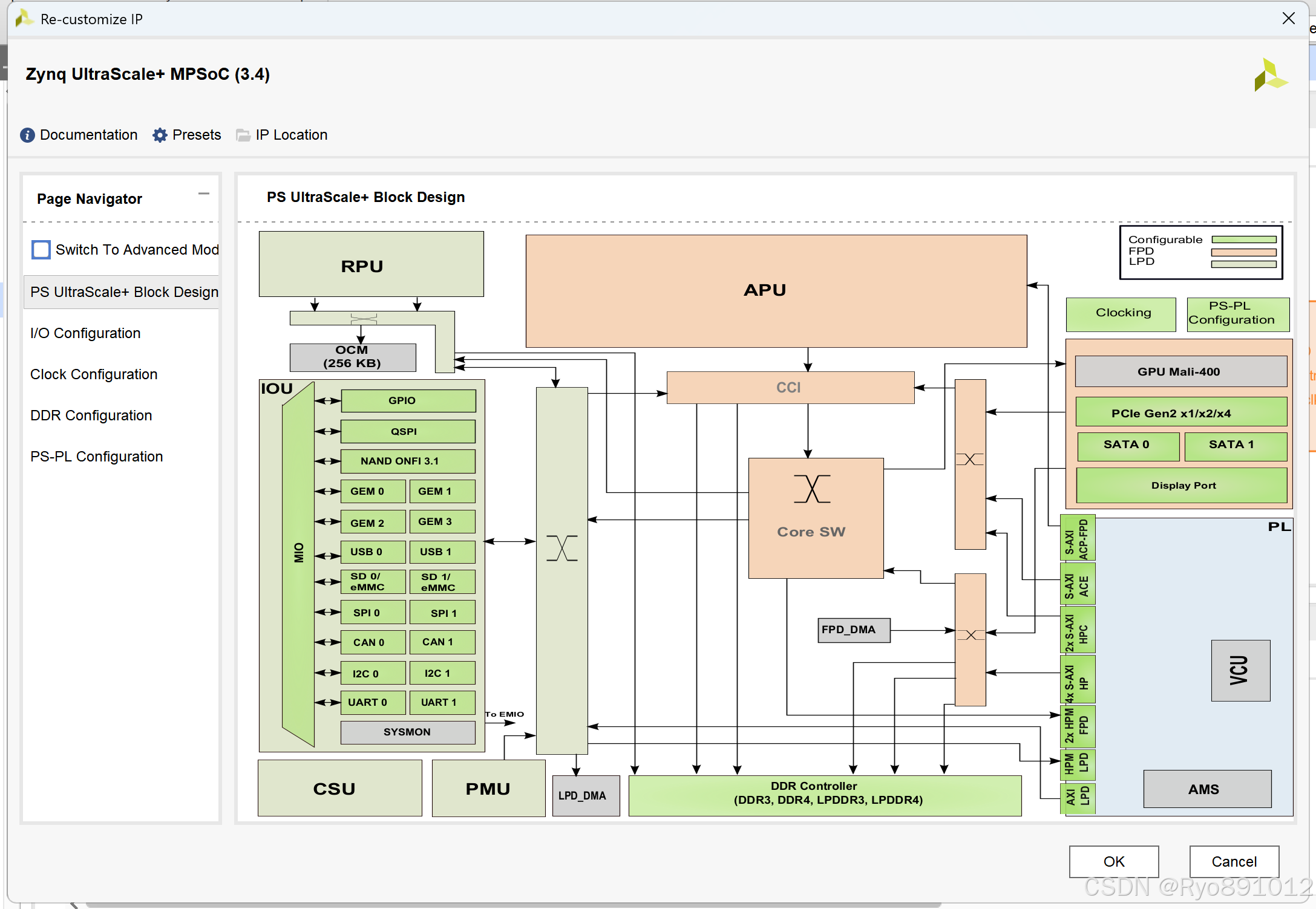

双击新建的MPSOC,就能进入PS的配置界面:

这里我们进行几个必要的配置:

bank电源、时钟、串口接哪里、从哪里启动

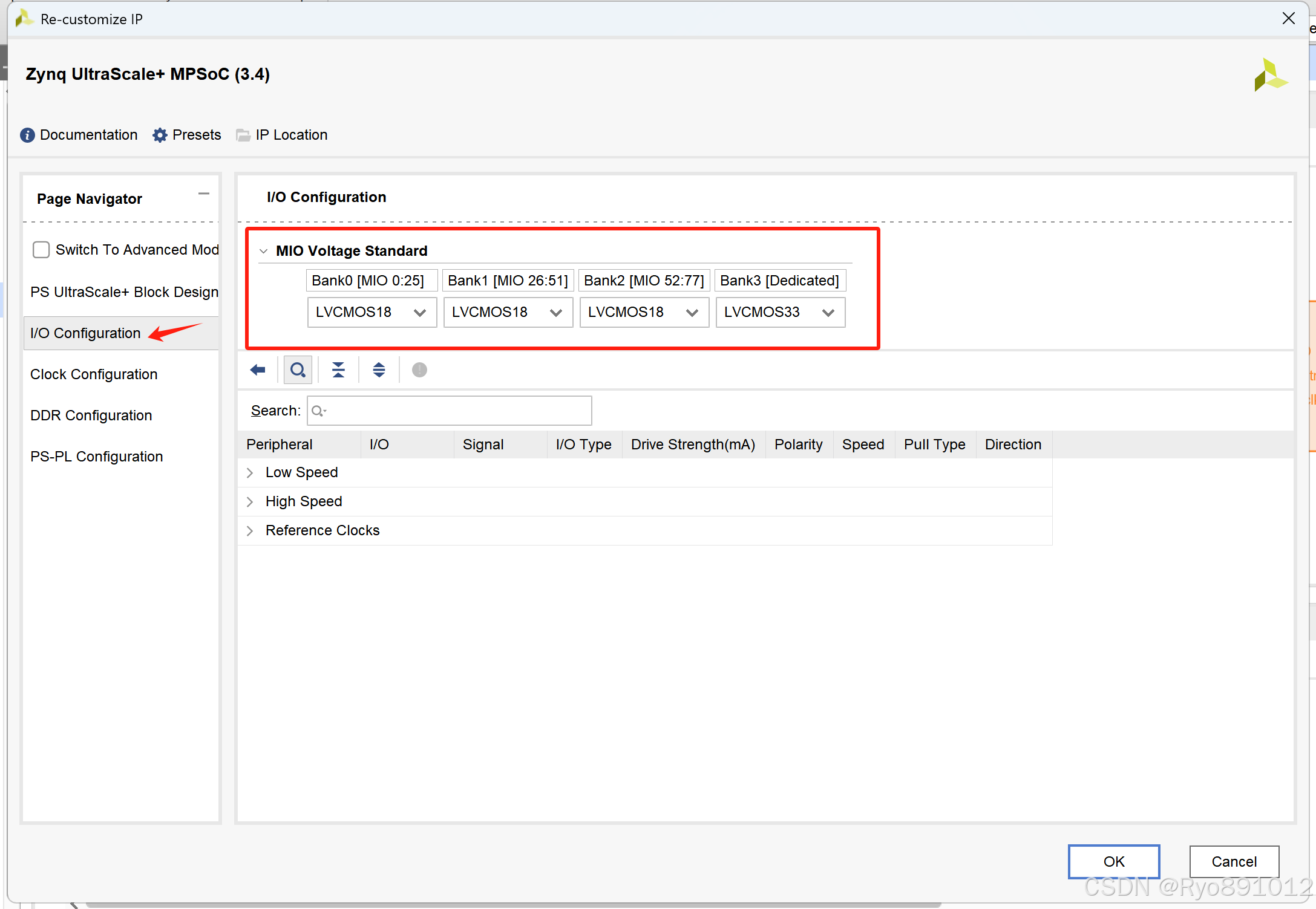

根据开发板的电路图可以知道,bank500-502用的1.8V,bank503用的3.3V,下图设置的BANK0-3就是实际芯片的BANK500-503:

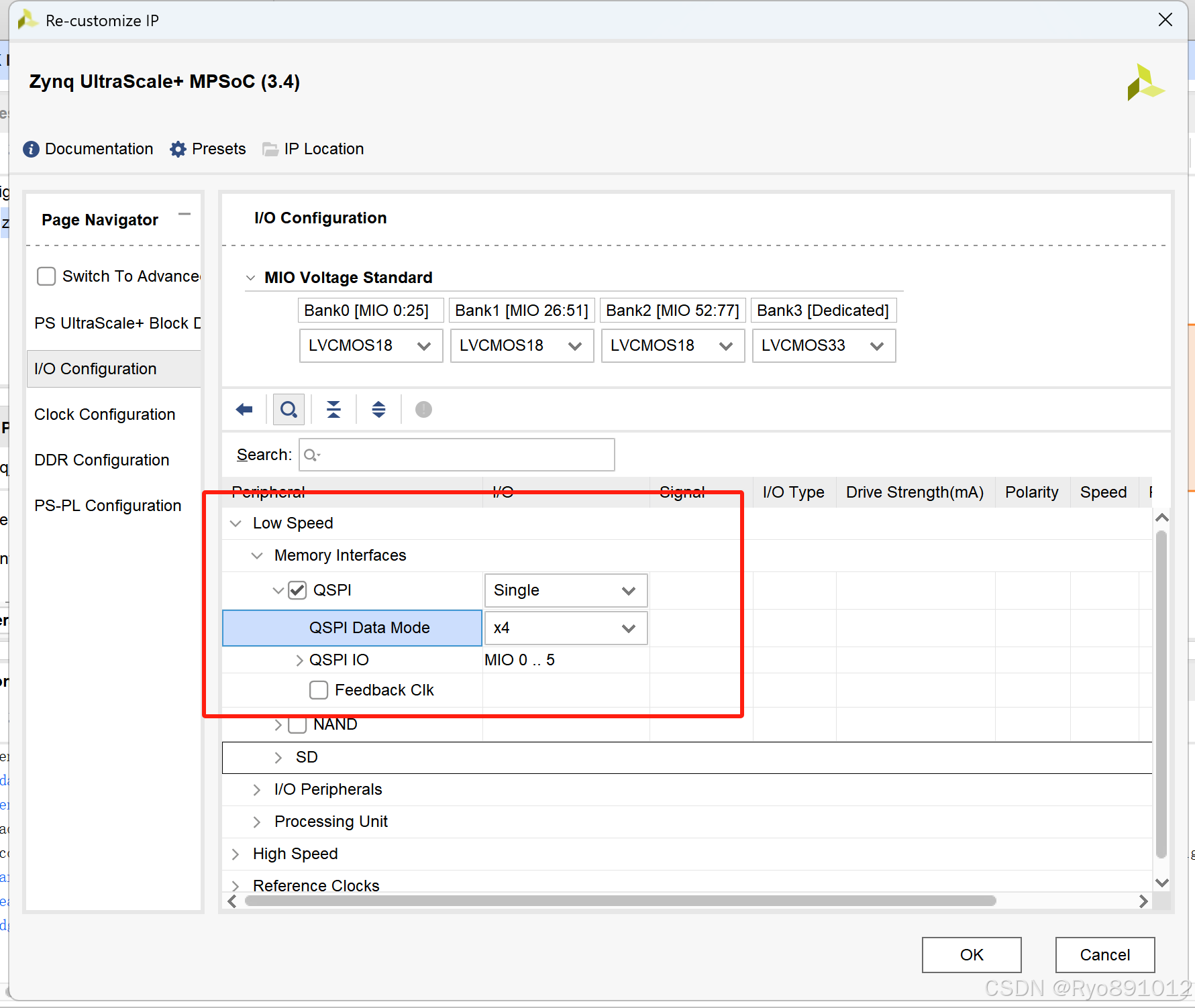

然后勾选SPI x4:

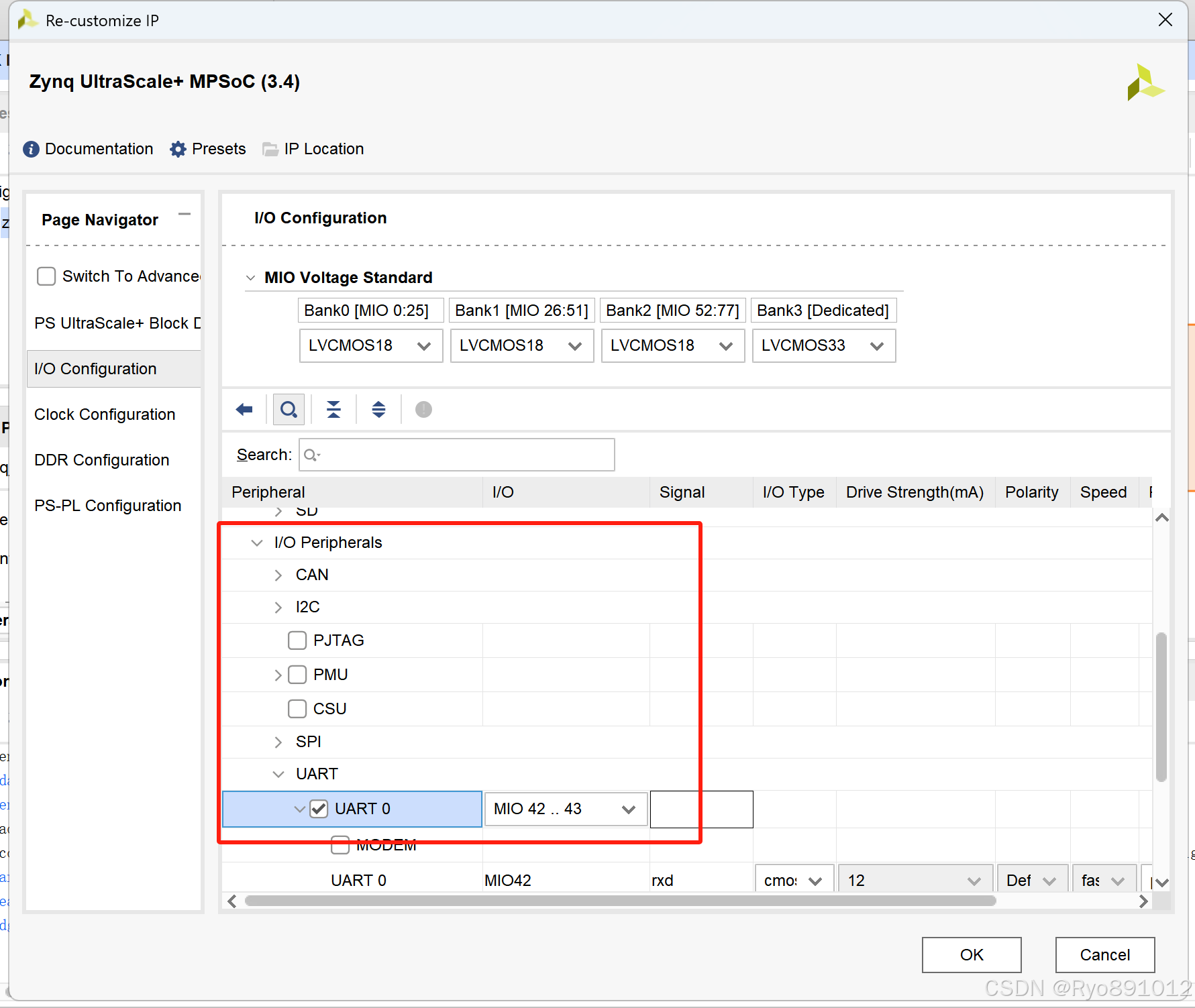

然后是打印Hello的串口,硬件上是接到MIO的42 43:

然后时钟因为硬件是33.333M,默认也是33.333M,就不设置了,直接OK;

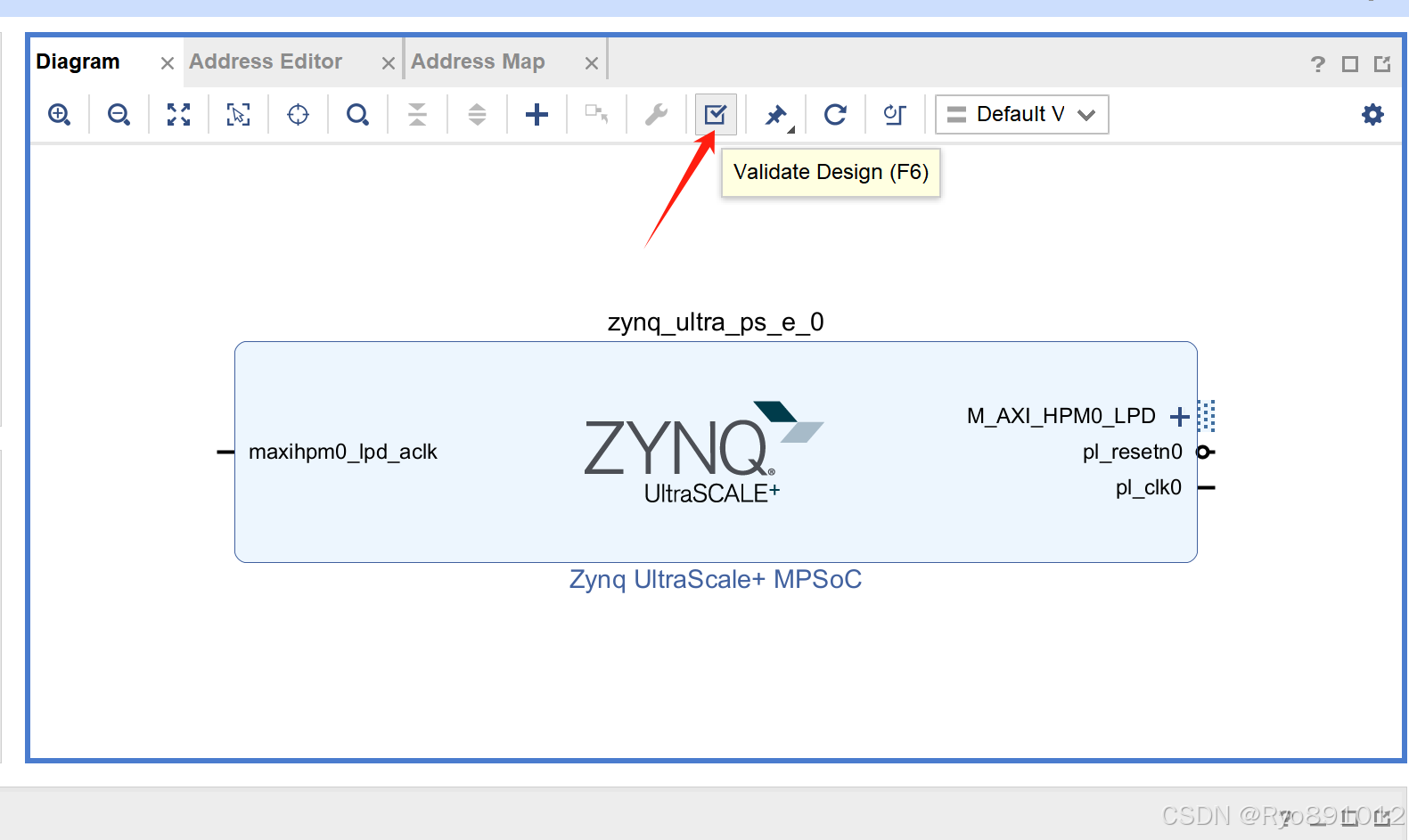

到这里就做好了PS的基础配置,点击检查一下:

发现报错,提示有个时钟未接:

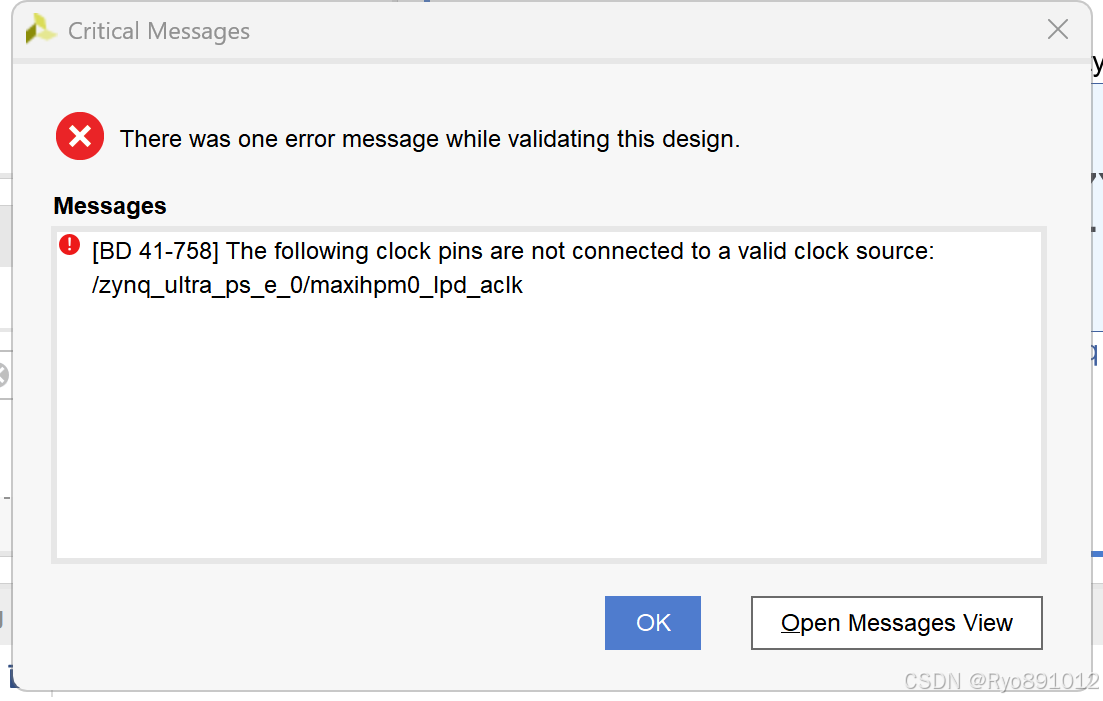

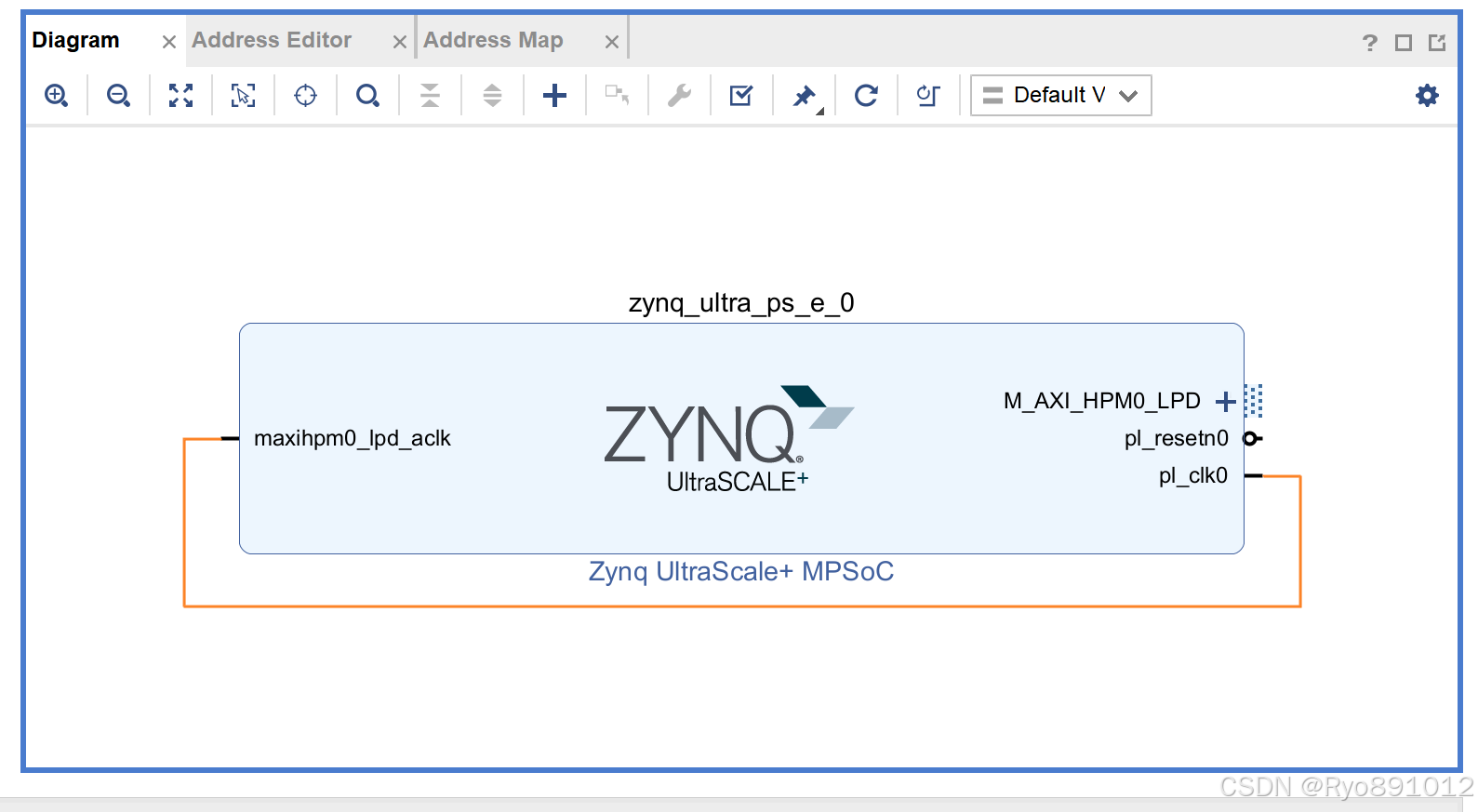

好吧,你可以在配置界面关闭这个时钟,也可以直接连接上:

然后就可以保存关闭BD了。

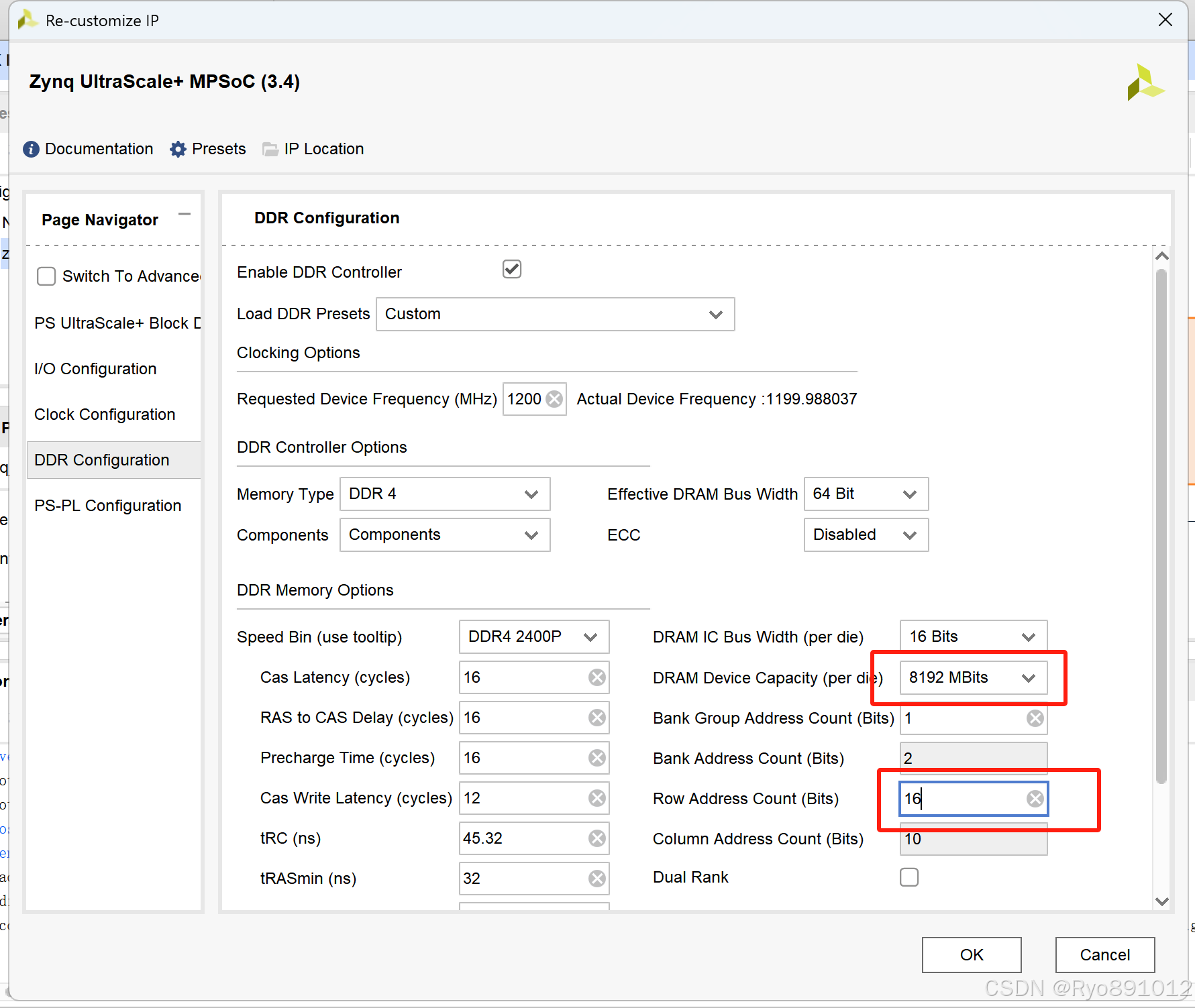

擦,看了一眼ALINX的文档,发现还忘了一步,还得设置DDR,重新打开BD,然后双击进入MPSOC的设置界面:

在 DDR Configuration 窗口中,Load DDR Presets 选择

”DDR4_MICRON_MT40A256M16GE_083E”

还不够,还得改一下参数:

4、运行vivado工程,导出xsa

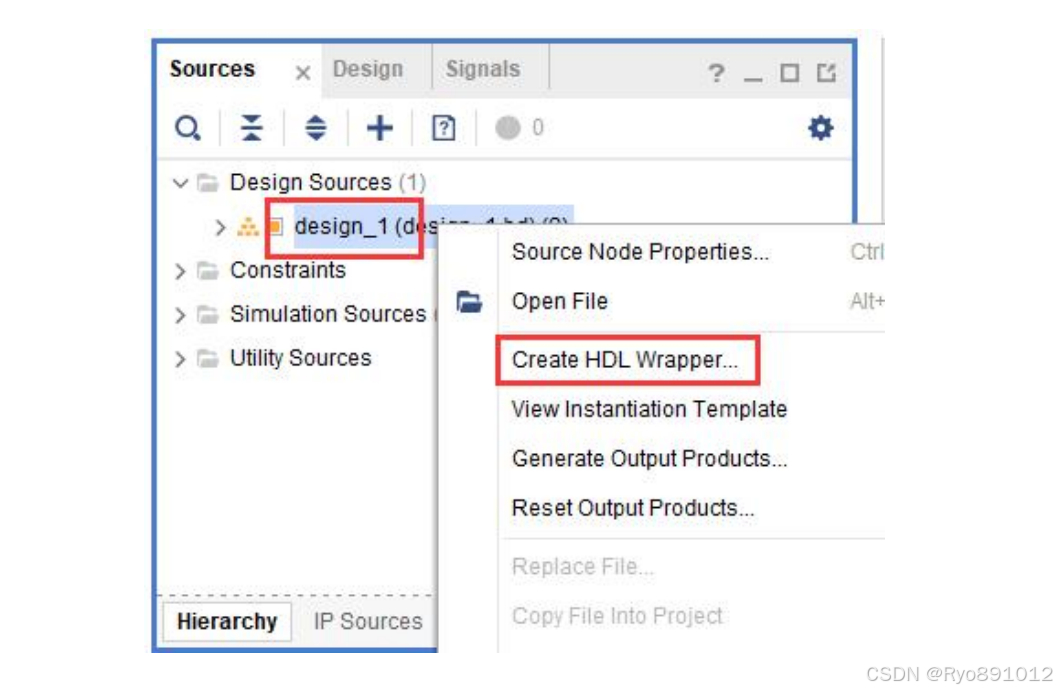

BD设置好以后,先给BD建一个Wrapper文件:

然后就是点击Generate Bitstream,跑完整个工程;

这里有个知识点!!!!

其实我们PL上没有任何功能,bit生成出来也不会用,我们刚刚在BD中对MPSOC的设置,其实都是为了导入到Vitis里面用的,所以只需要在BD上点右键,Generate Output就行了,但是奈何强迫症犯了,不跑完整个工程就像少点啥。。。

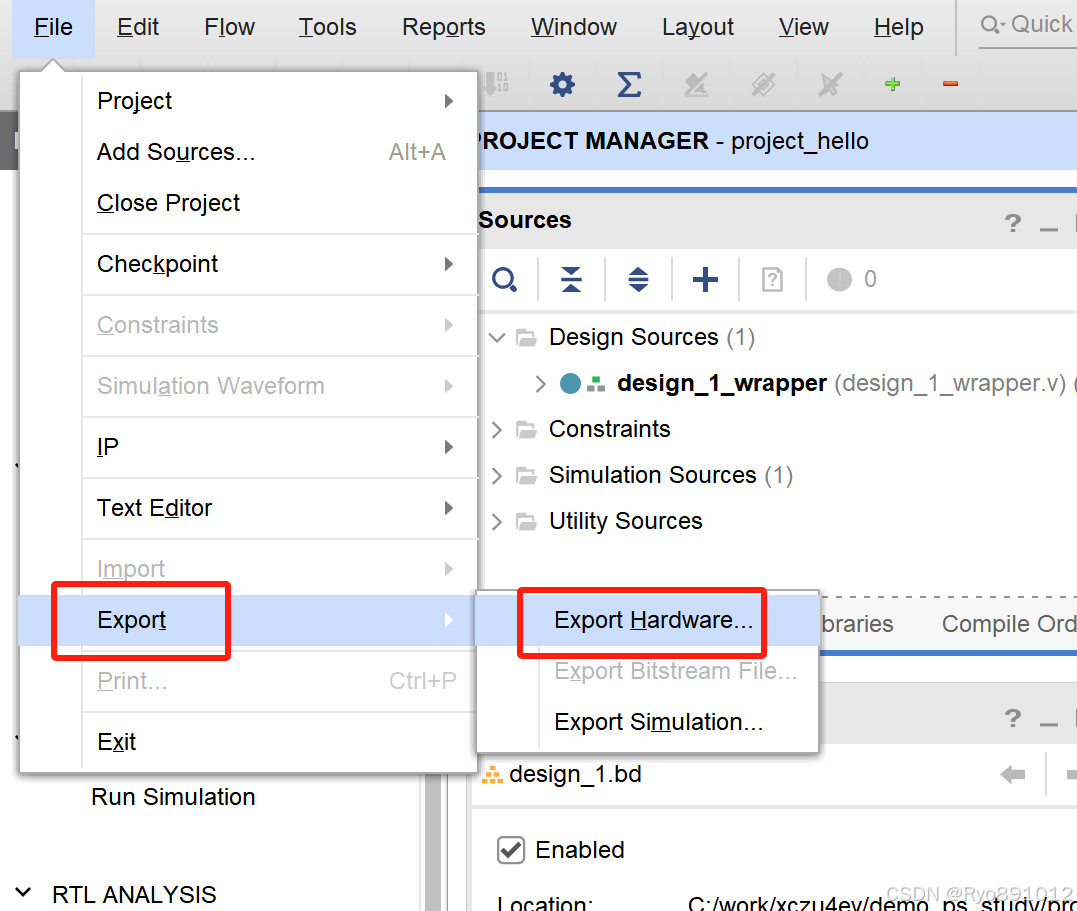

等工程跑完,导出硬件:

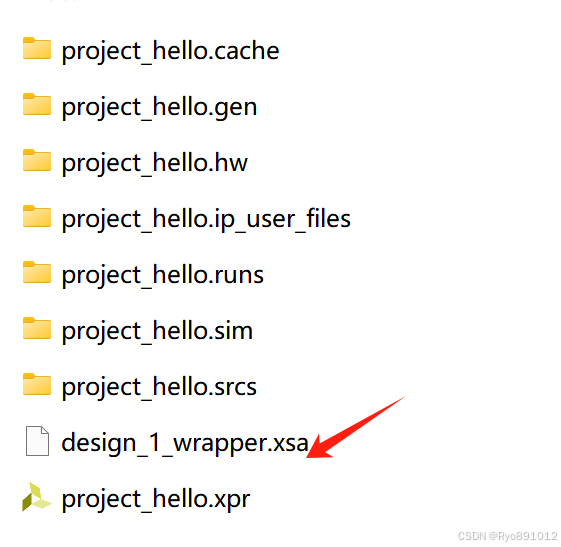

一直默认即可,然后就会在工程目录中生成xsa文件,这个在旧版vivado中叫hdf文件。当然,你想导出到其他文件夹也行。

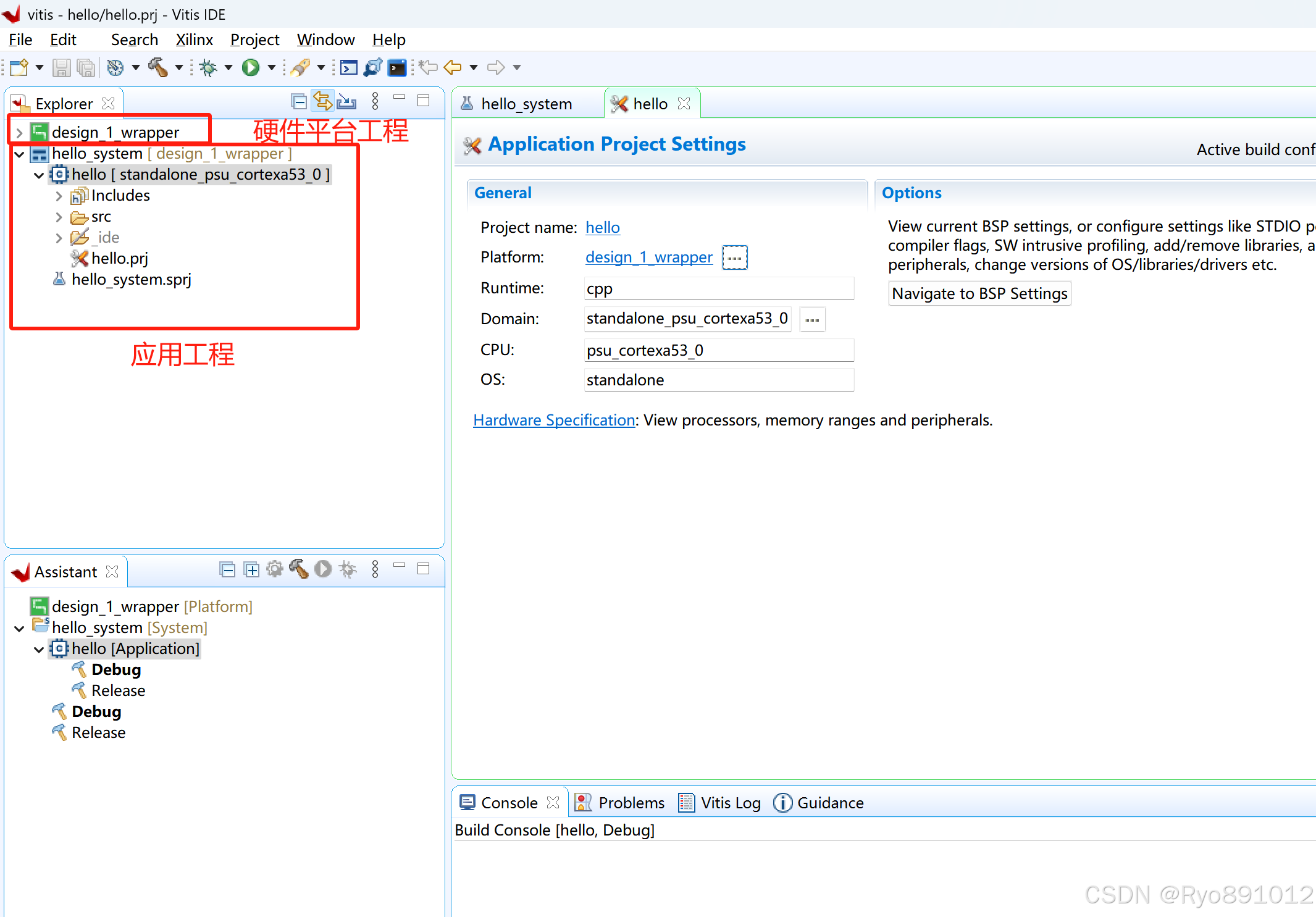

5、建立vitis工程

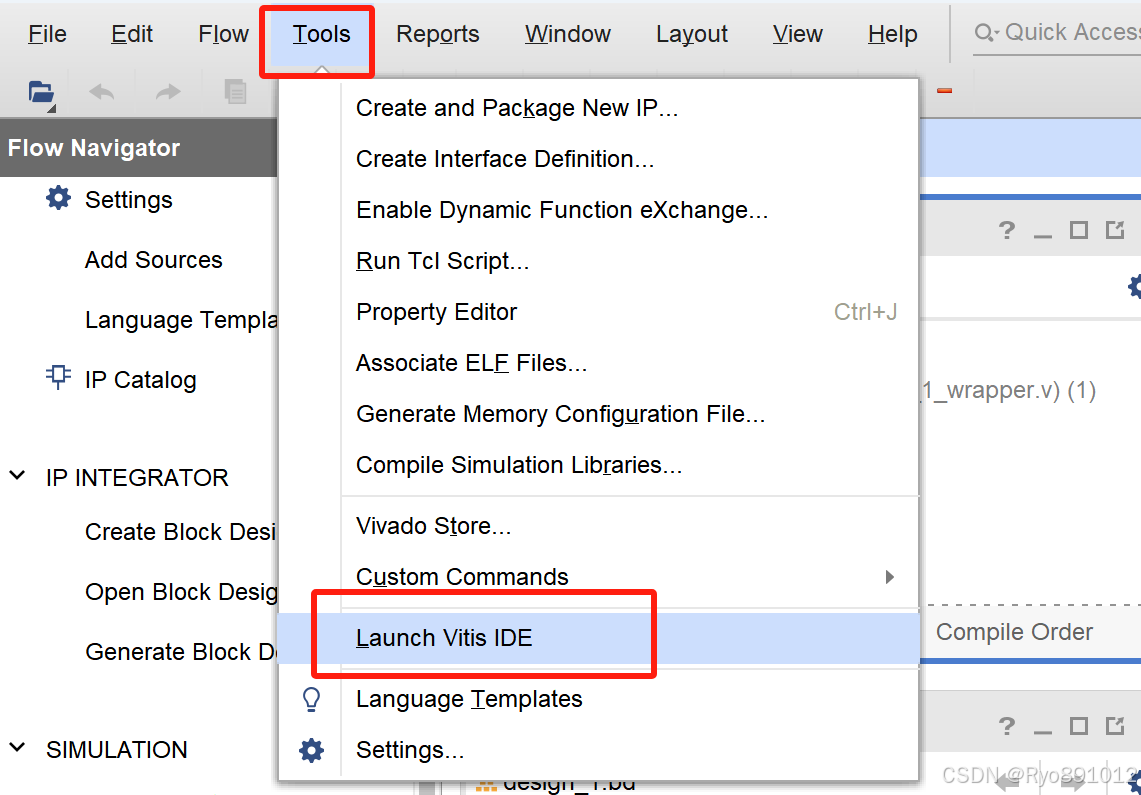

上面步骤就导出的xsa,然后我们开始建vitis工程,先新建一个vitis文件夹,我这里就直接在工程路径下建了,然后打开vitis,可以vivado菜单里打开,也可以从操作系统的应用列表里面打开。

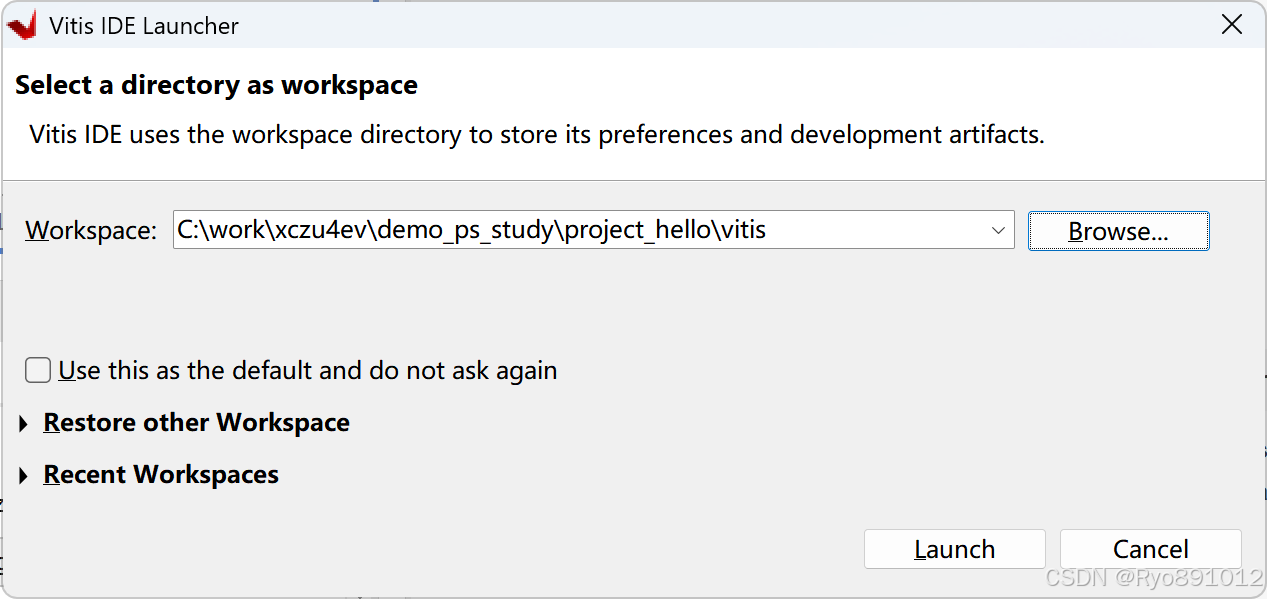

打开vitis后,需要选择一个vitis工程的路径:

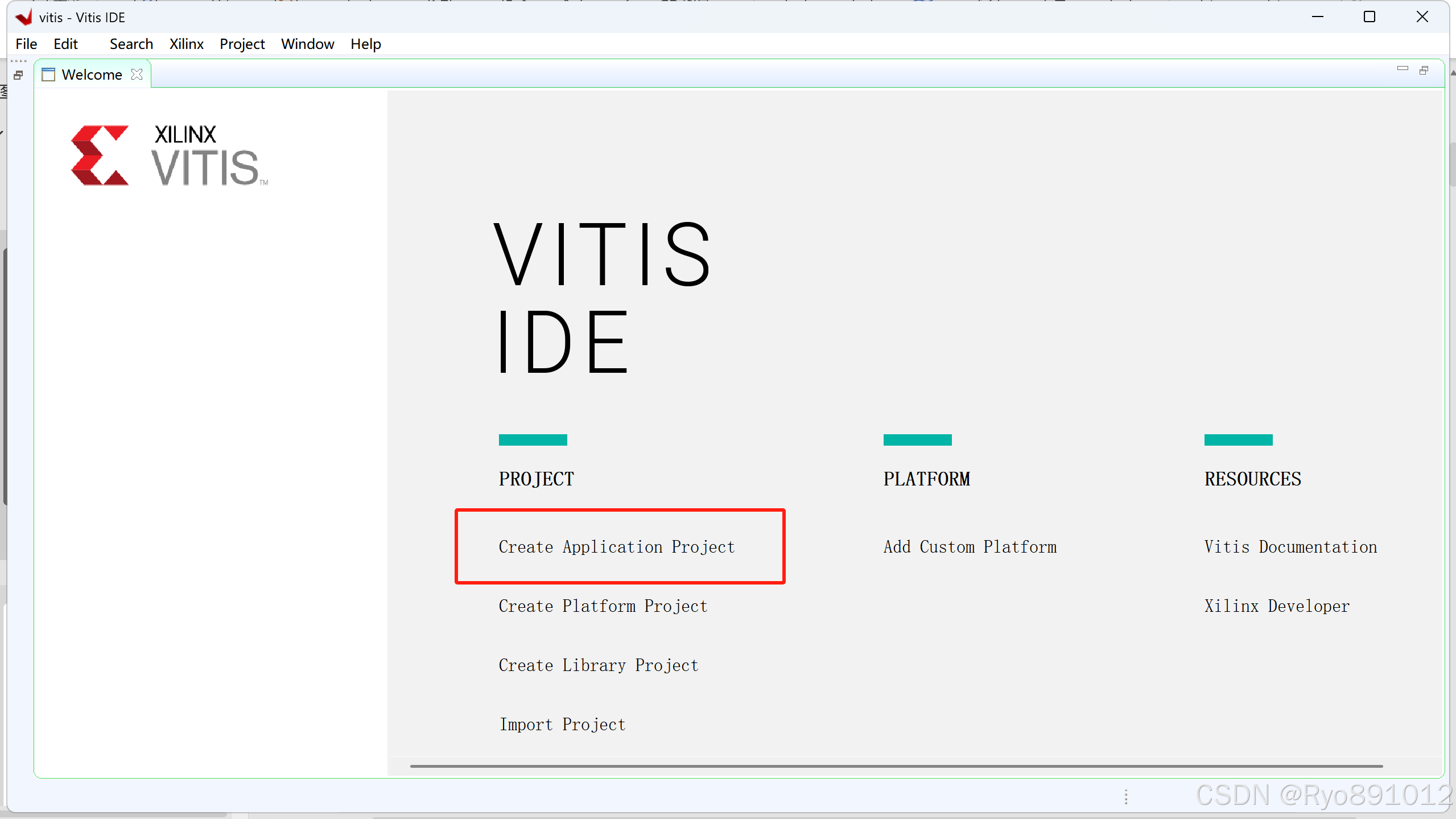

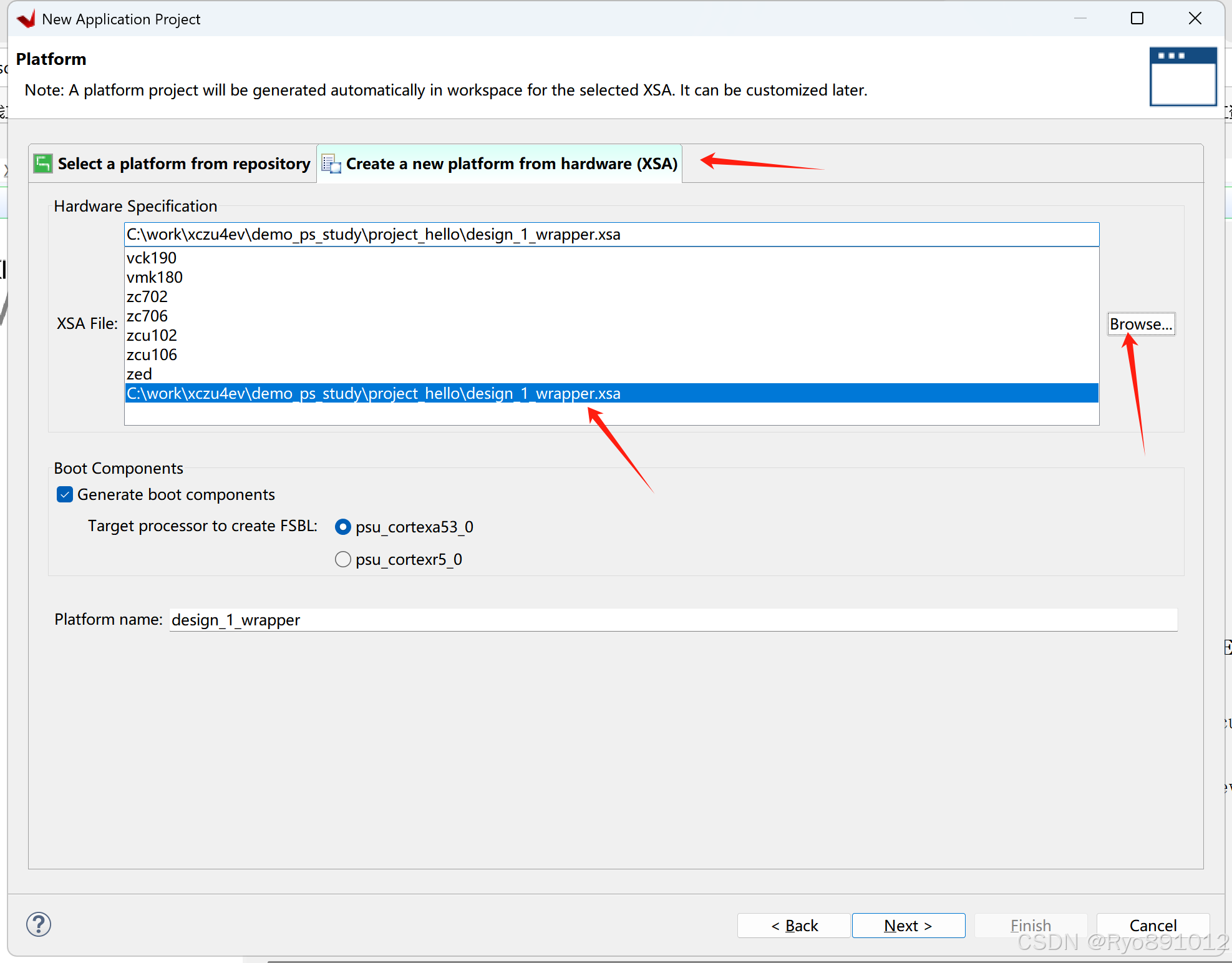

然后新建App工程,选择从xsa文件新建:

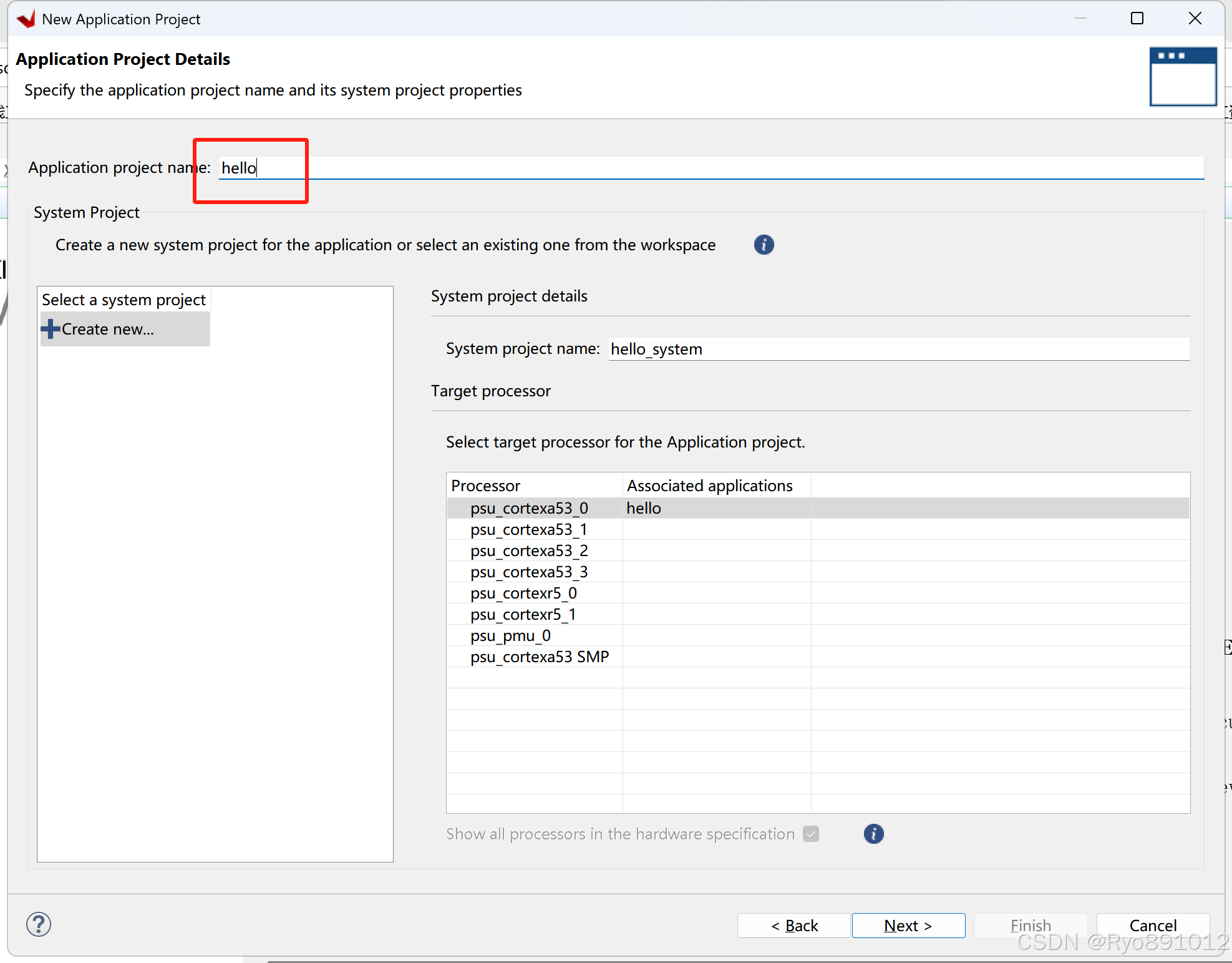

应用名字输入hello

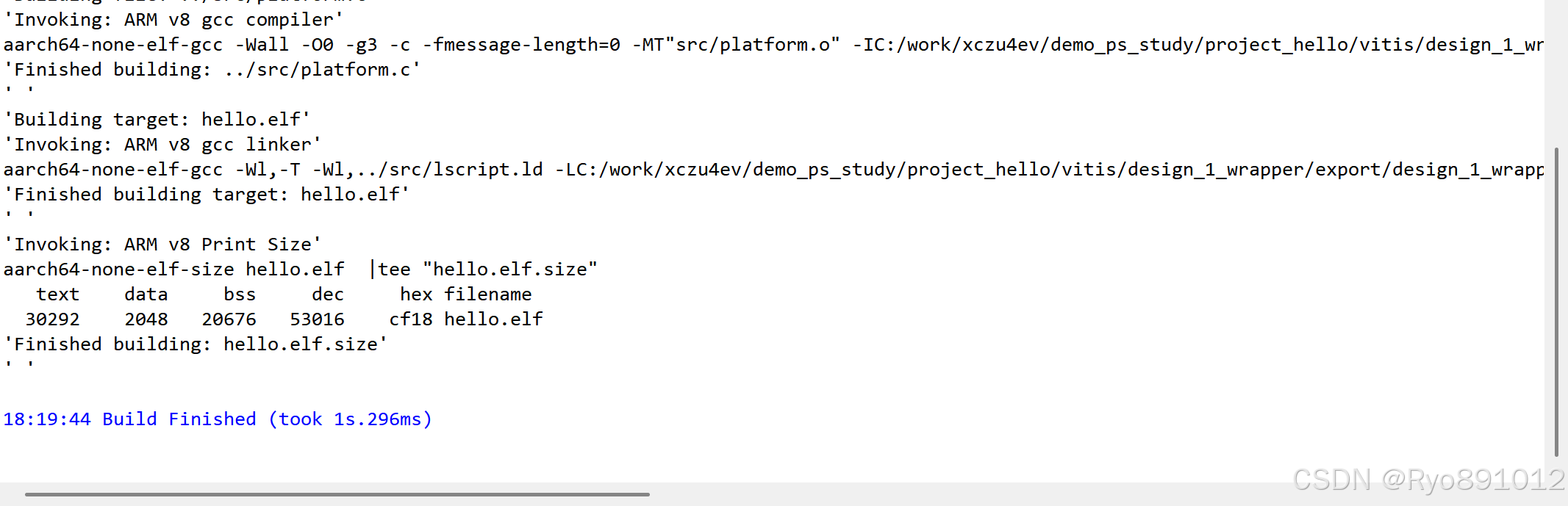

其他设置都默认,然后就建好了,直接点击锤子

运行工程:

等待一会儿,就编译好了:

下载调试

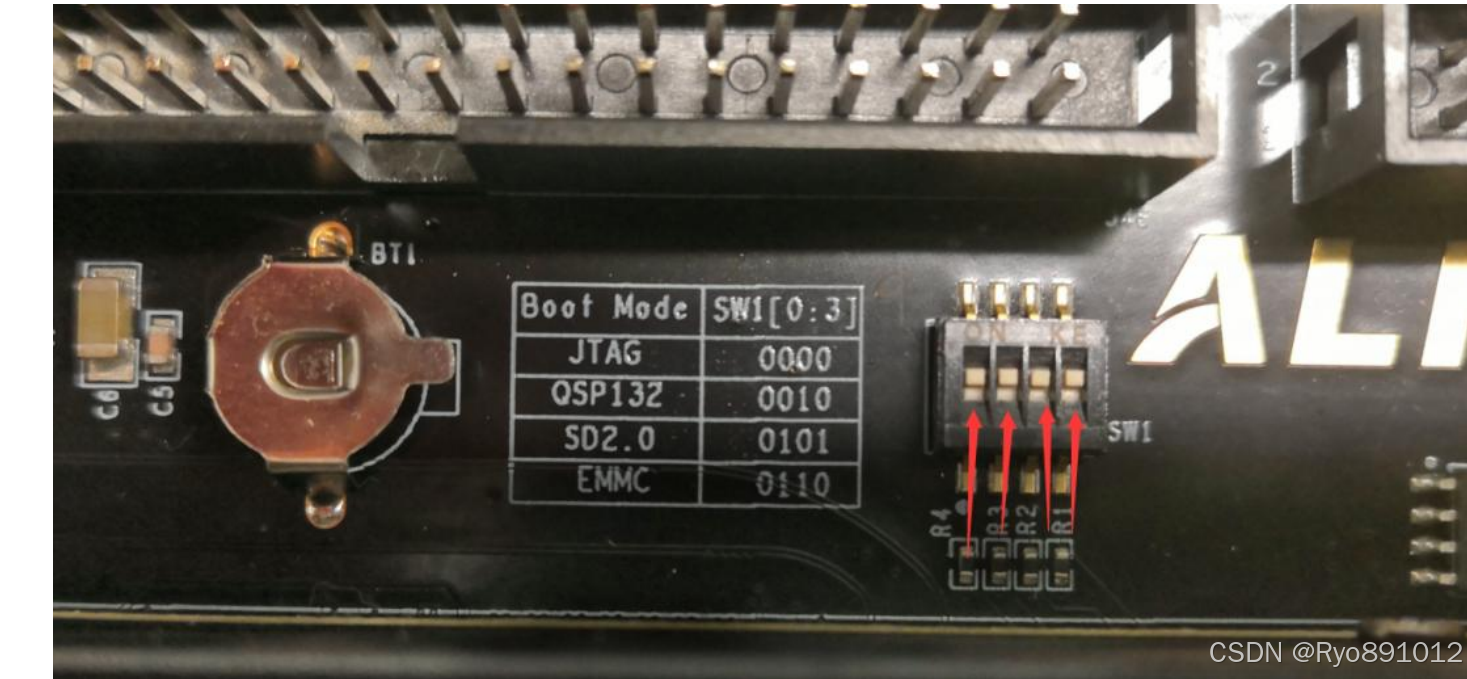

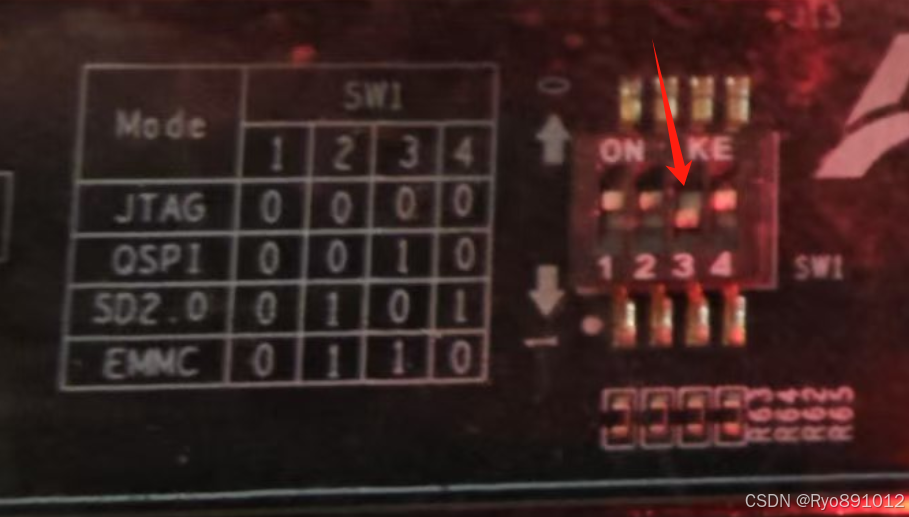

接着就是硬件连接,下载器、串口线,都接好,然后把启动模式改成jtag,这样开发板通电就不会主动运行程序。

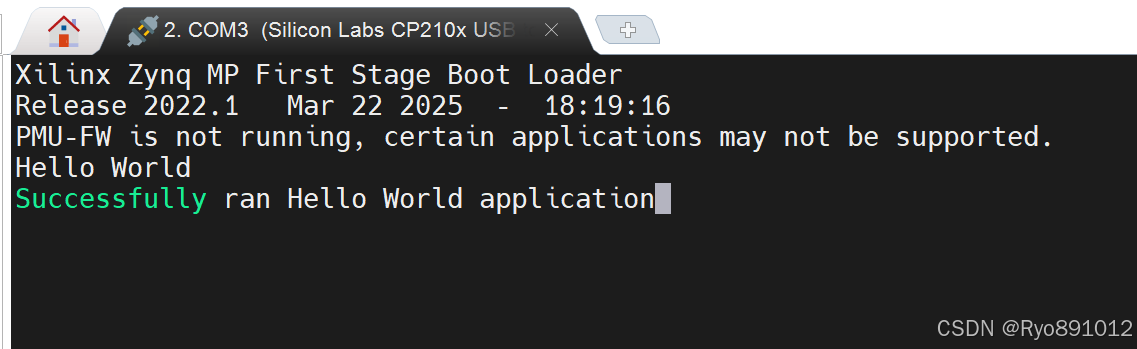

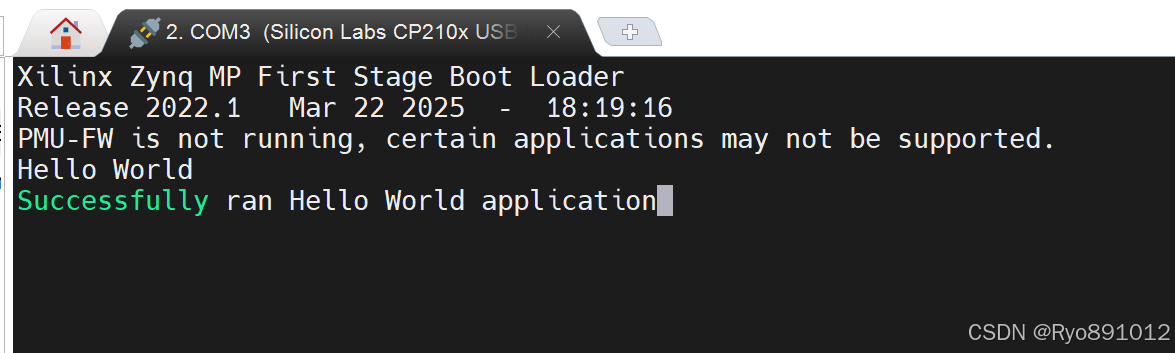

然后在hello工程上点右键,Run As,直接就用下载器连接板子,然后就会加载hello程序到ARM运行了。

串口终端上可以看到输出了:

固化启动

前面一个步骤是通过jtag下载器在线调试的,程序并没有存在flash中,断电就没有了,现在我们想把这个hello程序下载到芯片附带的flash中去,应该怎么操作呢?

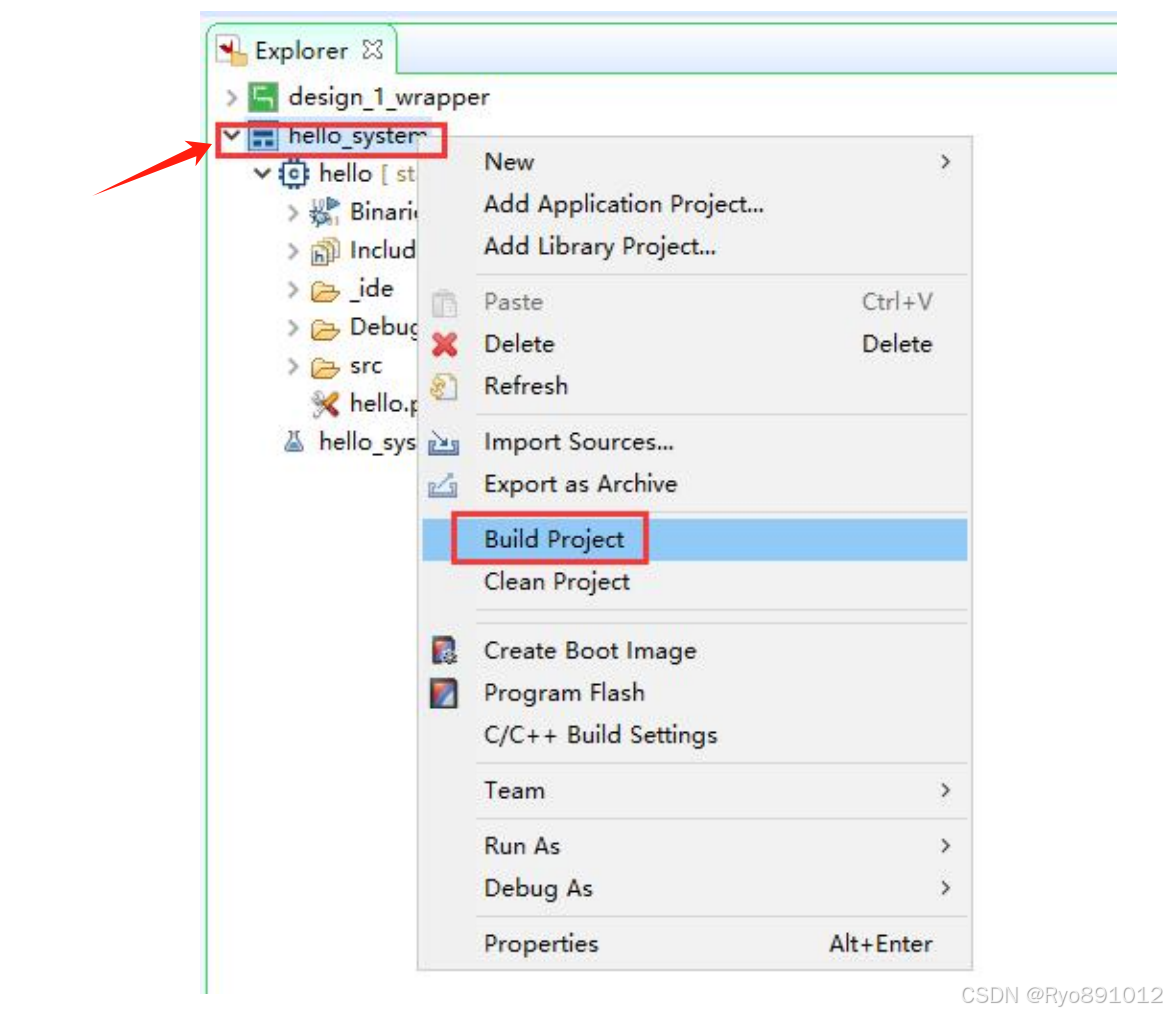

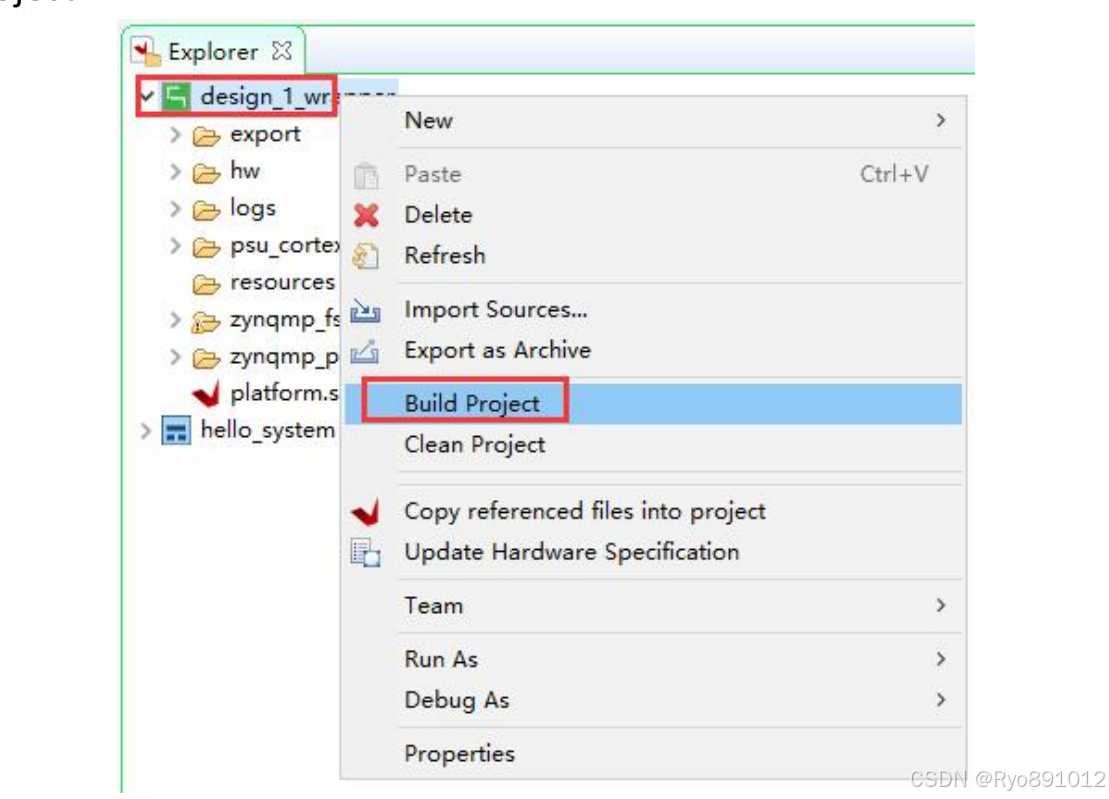

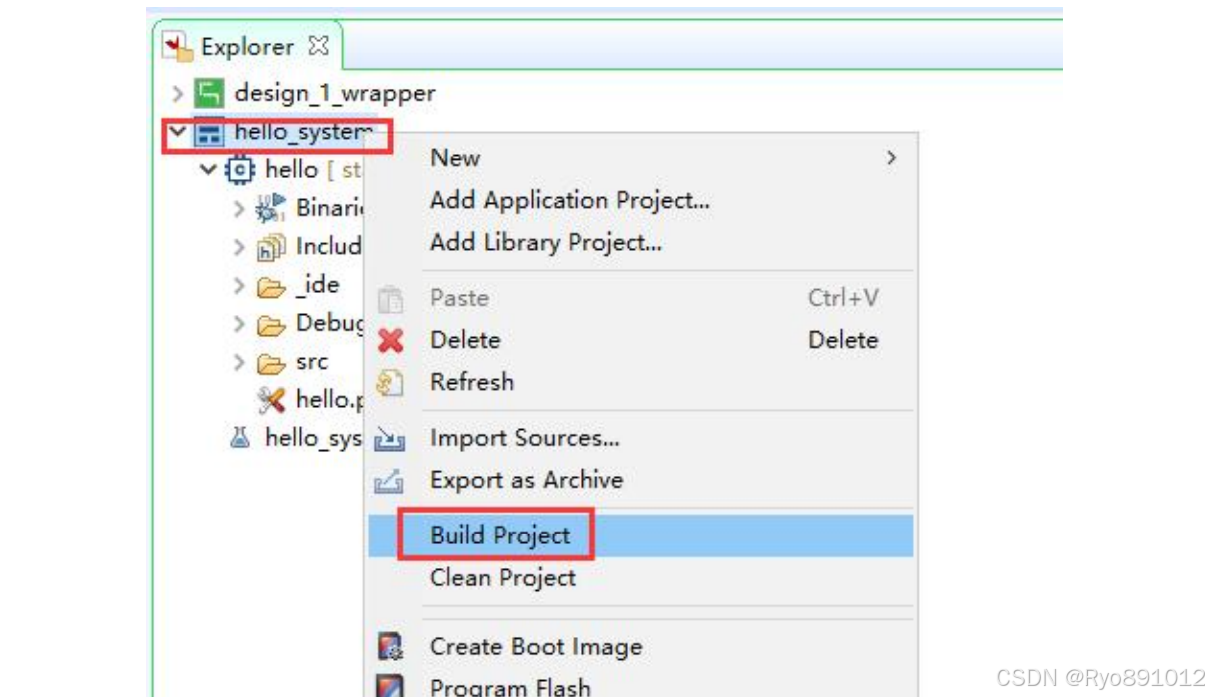

在hello_system上点右键,直接build工程(之前点击锤子是只build了hello)

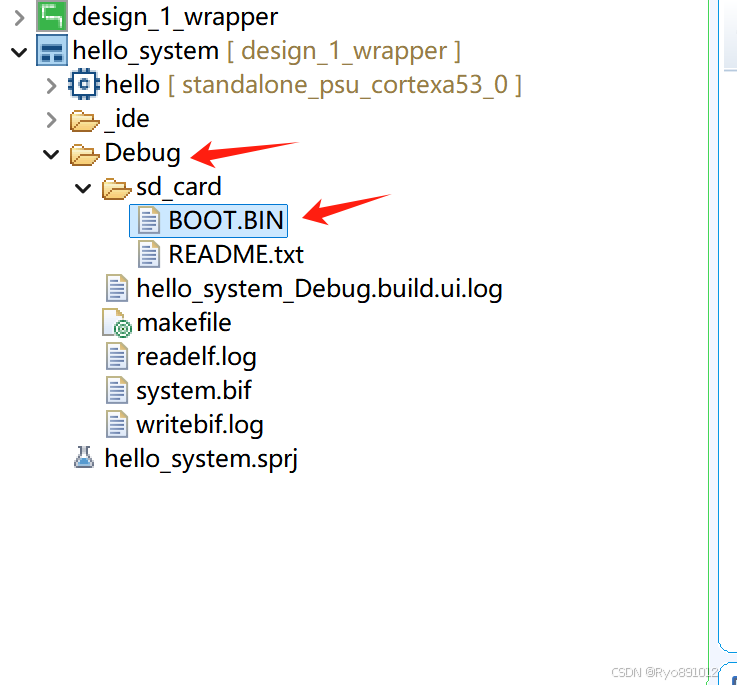

然后,就可以看到一个新的文件夹生成出来。

这个BOOT.BIN就是烧写文件,里面含有了fsbl和hello.elf文件,直接可以烧写到qspi flash中去。

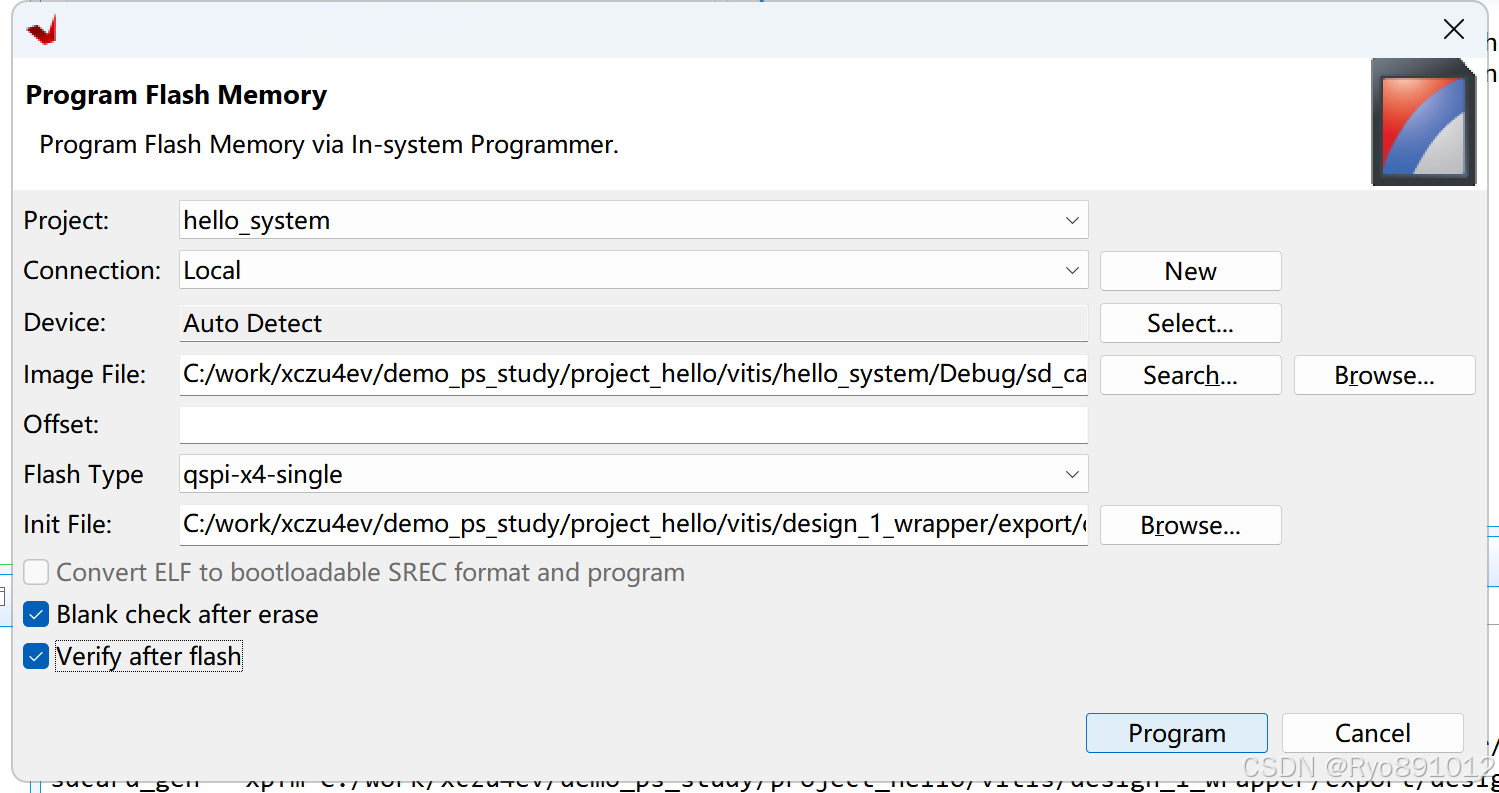

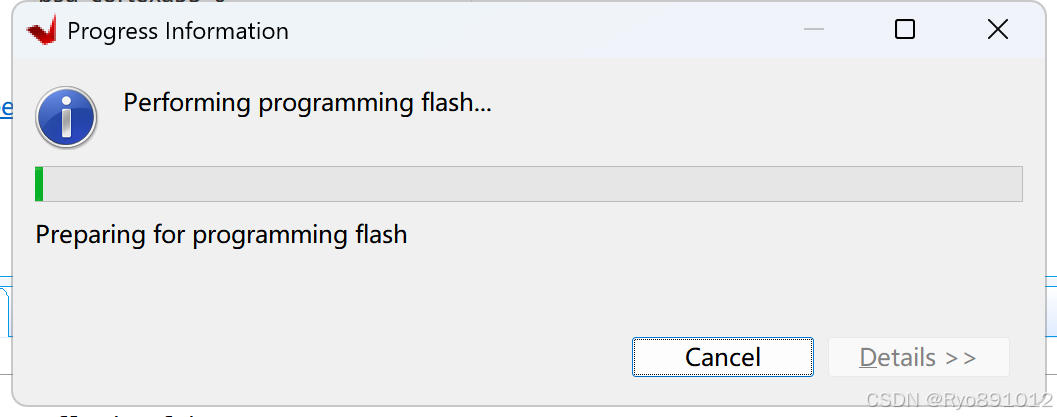

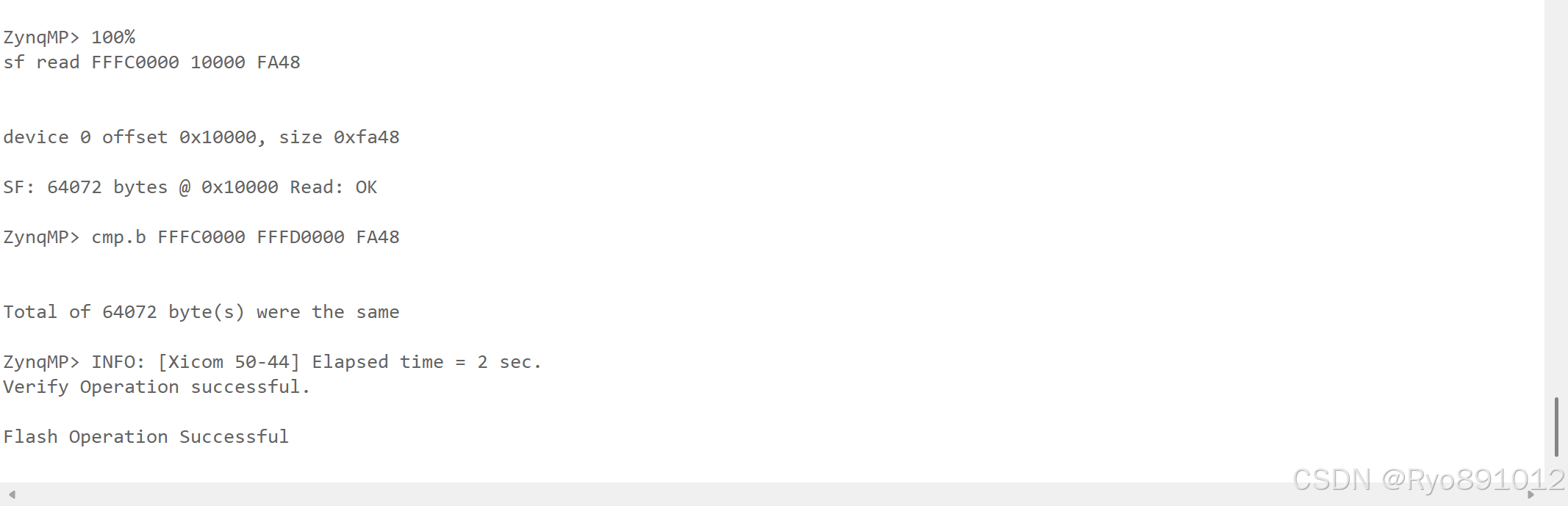

在菜单中选择Xilinx->Program flash,然后选择BOOT.bin

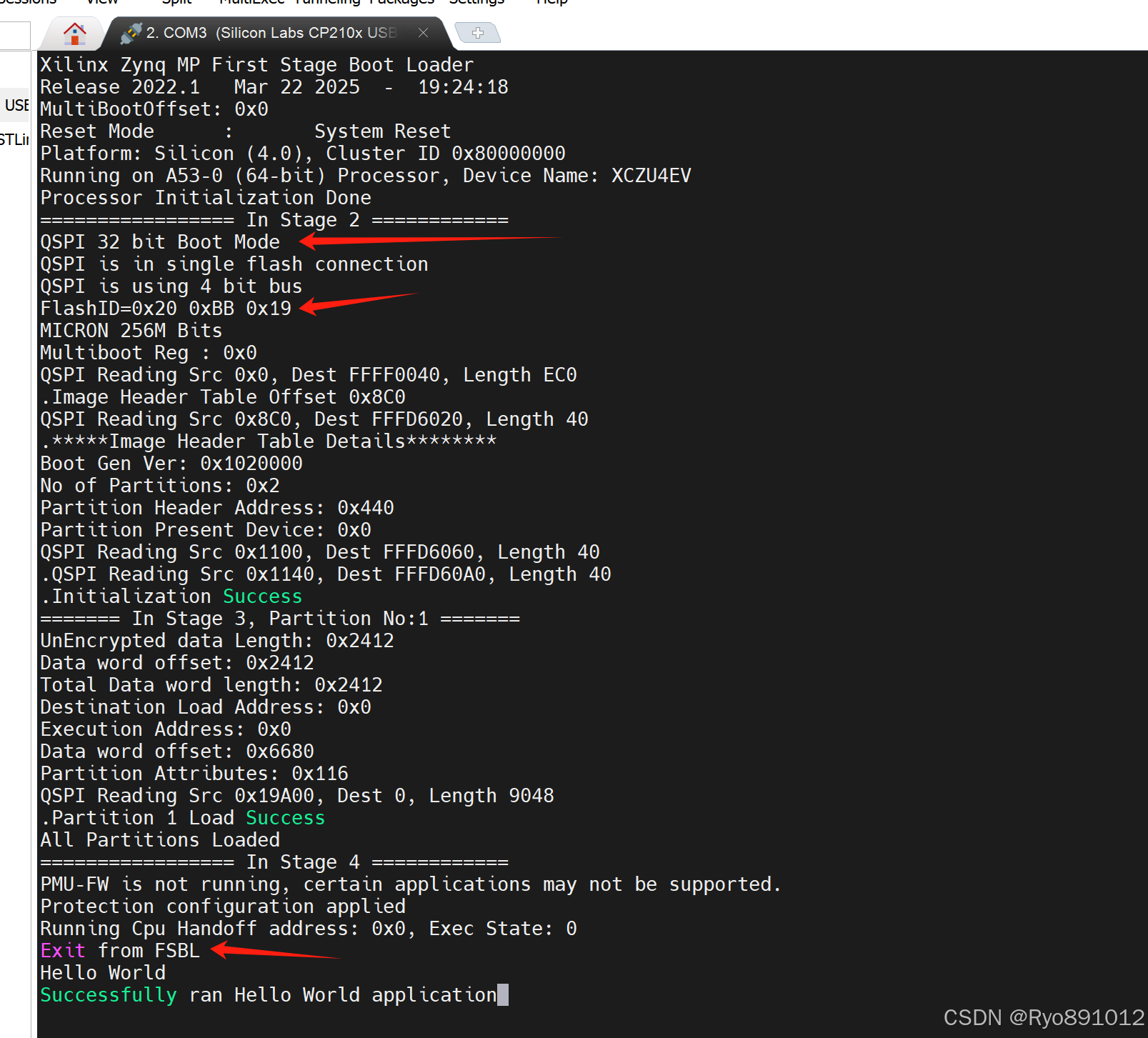

然后把启动模式改成qspi启动,断电重启,从串口终端中就可以看到启动打印了:

增加debug打印信息

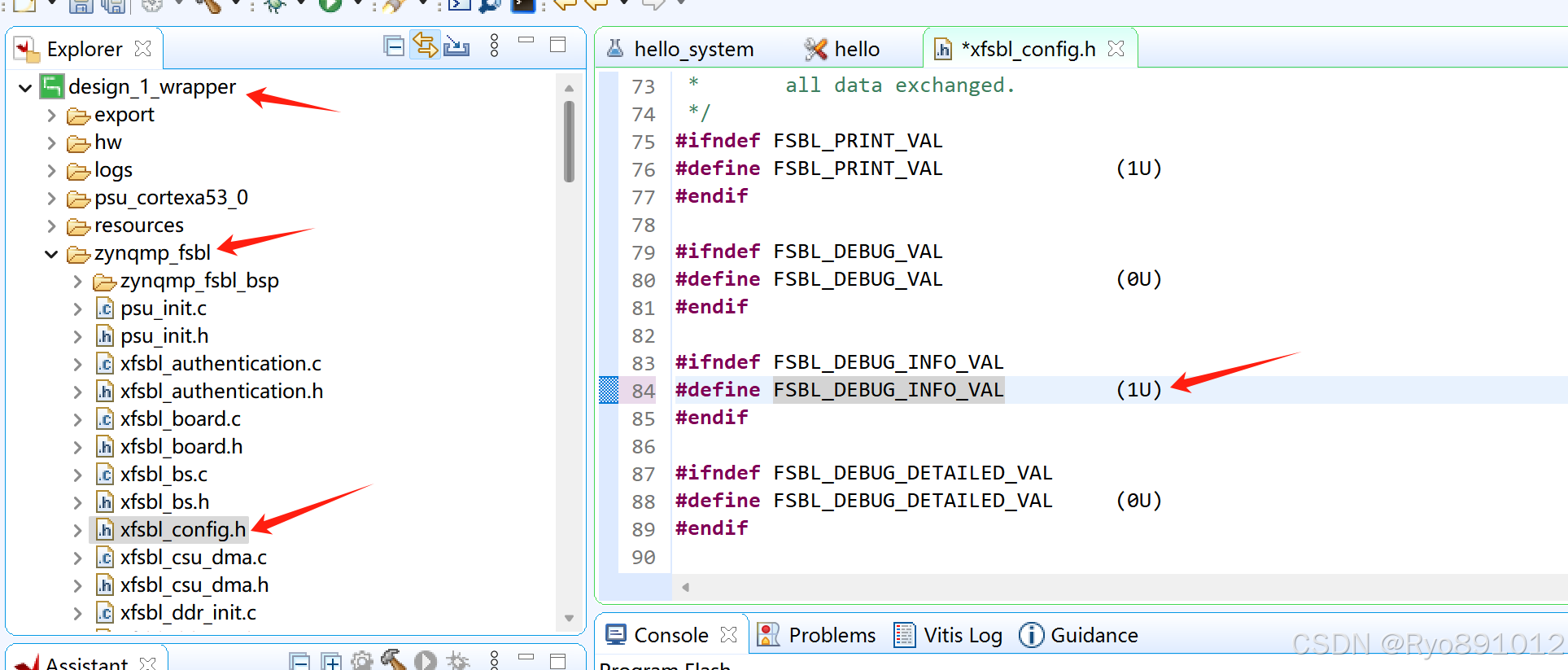

zynq启动过程中,是先启动fsbl,再加载app,这个过程经历了很多步骤,xilinx提供了一个debug选项,可以把启动过程打印出来,这样就能看到更详细的启动过程了。

把fsbl工程的FSBL_DEBUG_INFO_VAL改成1,重新build 硬件工程:

再build hello工程:

再重新烧写新的BOOT.BIN文件,烧写后断电重启,可以看到串口打印更加丰富了:

工程可以在这里下载:

https://download.csdn.net/download/cdutcl/90522076

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?