计算机组成原理系列

声明:此为个人笔记,代码一部分来自王道408课程,仅供个人学习使用,如有侵权请联系;如有转载使用,一切后果自行负责与本人无关

三、存储系统

3.1存储系统概念

3.2.1存储器芯片的基本原理

-

3.2存储器芯片的基本原理

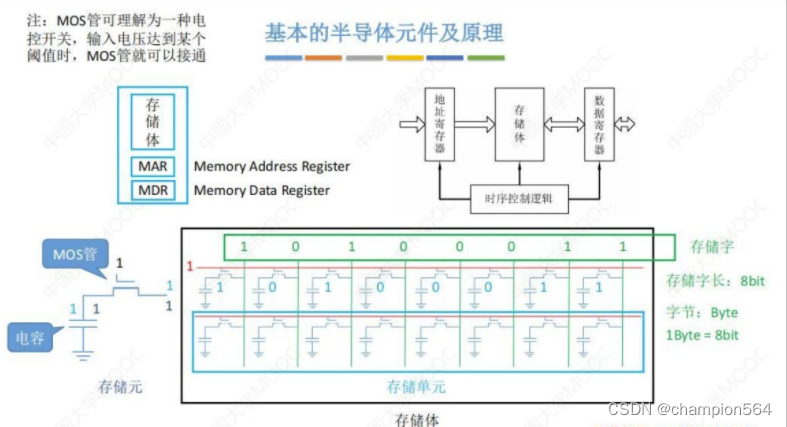

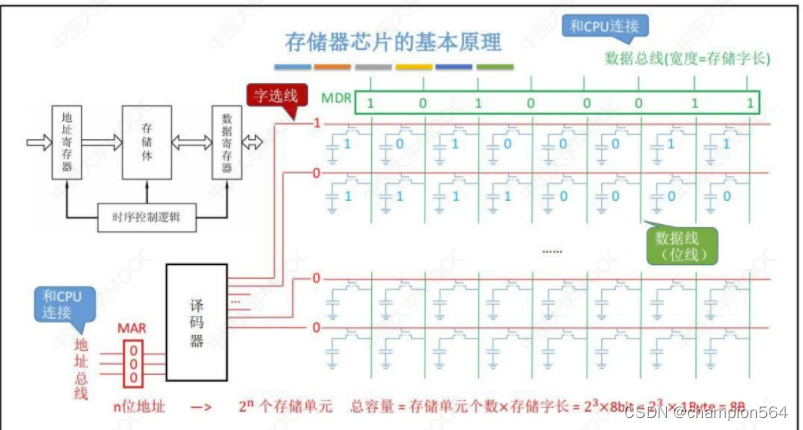

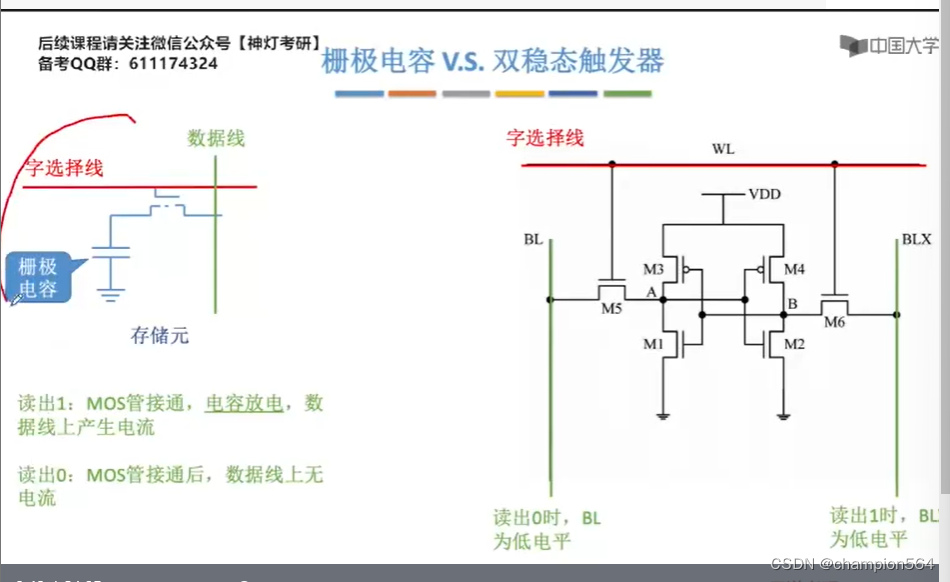

mos管接通是有电荷,电容存储电荷,存储元表示1,反之无电荷表示0。多个存储元单位组成一个存储单元,如下10100011;多个存储单元组成一个存储体。一个存储单元也成为存储字长,如10100011也叫做8bit(8位)。因此n位地址,就有2的n次方个地址,总容量等于存储单元个数*存储字长。

译码器通过多个自选线读多个存储单元,

一个内存条包含多个存储器芯片

如果要读取其中一个芯片的数据,就需要通过片选线给芯片高频电信号,其他芯片低频电信号,以区别;

地址线一般是CPU通过数据总线结构控制的;

存储芯片对外暴露的迎角每一条都对应一条线(读写线、片选线、数据线等)

对于整个存储体而已就可以这样表示容量

8k\*8 就是2的13次方\*8比特

1k=1024B=2的十次方

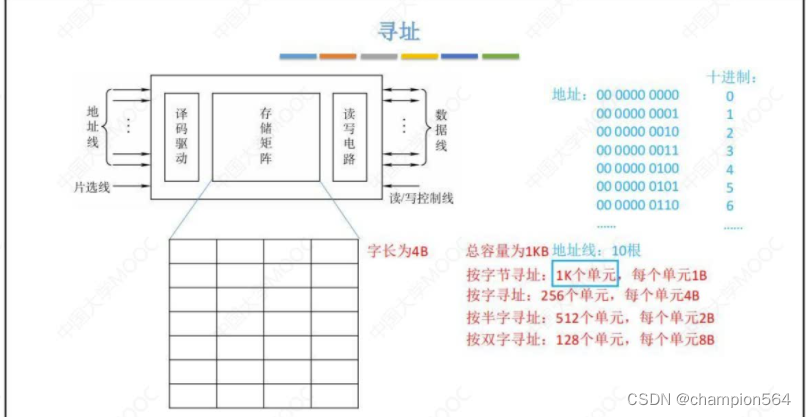

现代计算机都是按字节寻址(1B=8bit)

总量为1KB,地址线为10根的情况下:

按字节寻址 1k个单元,每单元1B;按字寻址256个单元,每单元4B

按半字寻址,512单元,每单元2B;按双字寻址,128单元,每单元8B

3.2.2SRAM和DRAM

-

3.2.2 SRAM和DRAM

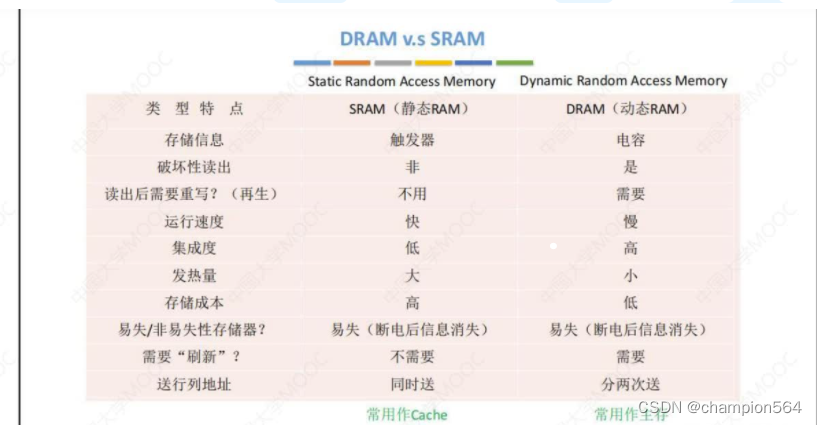

静态RAM(sram)用于cache

动态RAM(dram)用于主存,有地址复用技术和特有的刷新方法

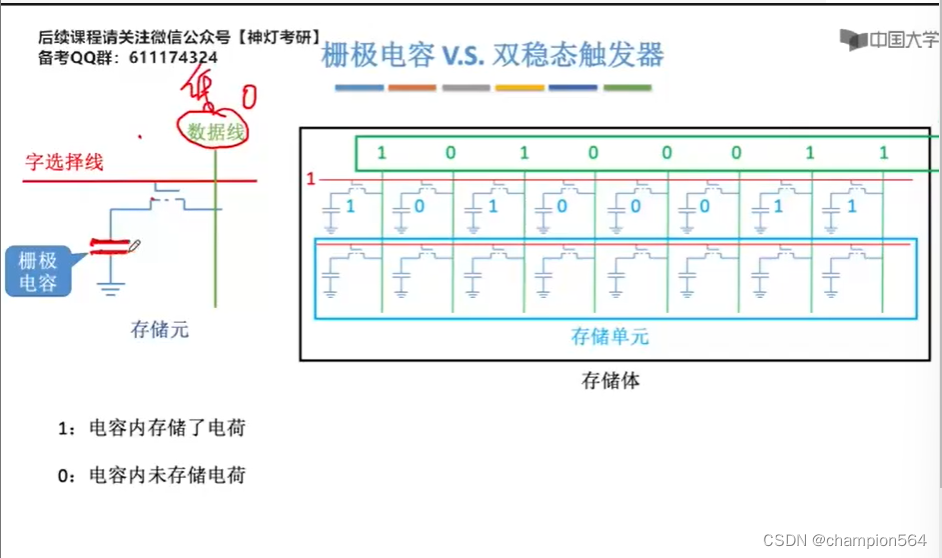

电容和稳态触发器的内容可以去查询电路器件的内容,此处不予深究

SRAM用触发器存储信息,非破坏性读出,读出后不需要重写,运行速度快,集成度低,成本高,易失存储器,不需要刷新,同时送行列地址,常做cache。

DRAM用电容存储信息,是破坏性读出,读出后需要重写,运行速度慢,集成度高,成本低,易失存储器(断电后信息消失),需要刷新,分两次送行列地址,常做主存。

DRAM的刷新

刷新周期:一般为2ms

刷新单位:行

刷新方法

一、集中刷新

刷新时间固定,存在死区;读写不受刷新影响,存储速度快;死区不能访问存储器(死区是指刷新时停止对存储器的读写操作的这段时间)

二、分散刷新

把每行刷新分散到每个工作周期中,没有死区;但是存储周期长,减低速度

三、异步刷新

结合上两种方法,缩短死时间又提高速度,具体方法是用刷新周期除行数得到刷新时间间隔T,用逻辑电路每隔T刷新一次。

3.2.3 ROM

-

3.2.3 ROM

ROM特点:随机存取,非易失性存储器,结构简单,位密度比可读写存储器高。

ROM类型:

MROM(掩模式只读存储器)

PROM(一次性可编程只读存储器)

EPROM(可擦除可编程只读存储器)可以对内容多次改写

闪存存储器(flash memory)可长期保存信息,可重

本文深入探讨了计算机存储系统,包括存储器芯片的基本原理,SRAM和DRAM的区别,ROM类型,主存与CPU的连接方式,以及Cache的工作原理和映射方式。内容涵盖存储系统的各个关键组成部分,解析了各种存储技术的特性,如DRAM的刷新机制,Cache的替换算法和写策略。

本文深入探讨了计算机存储系统,包括存储器芯片的基本原理,SRAM和DRAM的区别,ROM类型,主存与CPU的连接方式,以及Cache的工作原理和映射方式。内容涵盖存储系统的各个关键组成部分,解析了各种存储技术的特性,如DRAM的刷新机制,Cache的替换算法和写策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

423

423

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?