根据《pcie体系结构导读》一书的描述:

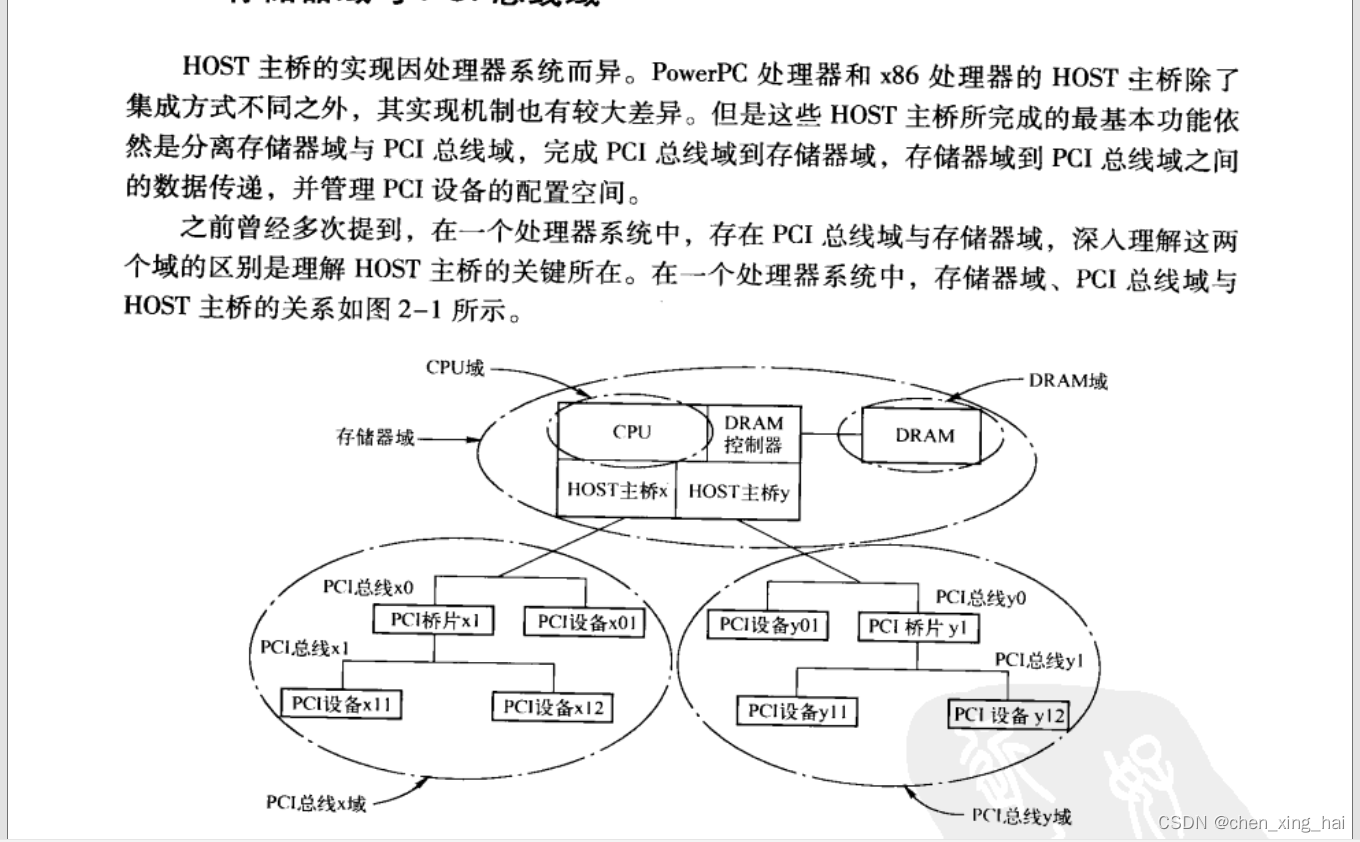

CPU域地址空间指CPU的core能直接访问到的地址空间集合;DRAM域地址空间指DRAM控制器所能访问的地址空间集合,DRAM一般指DDR-SDRAM。有些处理器系统中DRAM控制器能访问的地址空间并不能被CPU core访问,因此在此类处理器系统中,CPU域与DRAM域地址空间并不相等。

CPU core访问DRAM时,DRAM控制器会将CPU域地址转换为DRAM域地址;

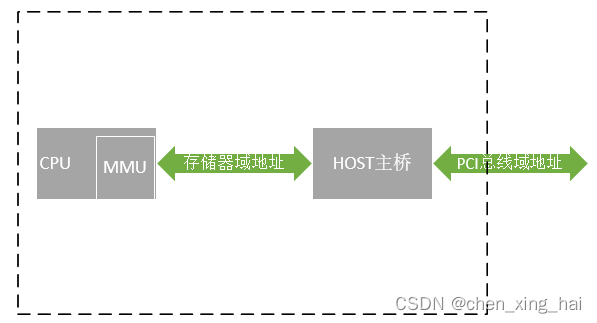

CPU core访问PCI设备时,HOST主桥会将CPU域地址转换为PCIE域地址;

CPU域包含了DRAM域,但不一定包含了DRAM域的所有空间,对于这类CPU系统,CPU并不能访问到DRAM域中的某些区域。但多数CPU系统中DRAM域是CPU域的一部分,CPU能够访问到DRAM域的所有区域。

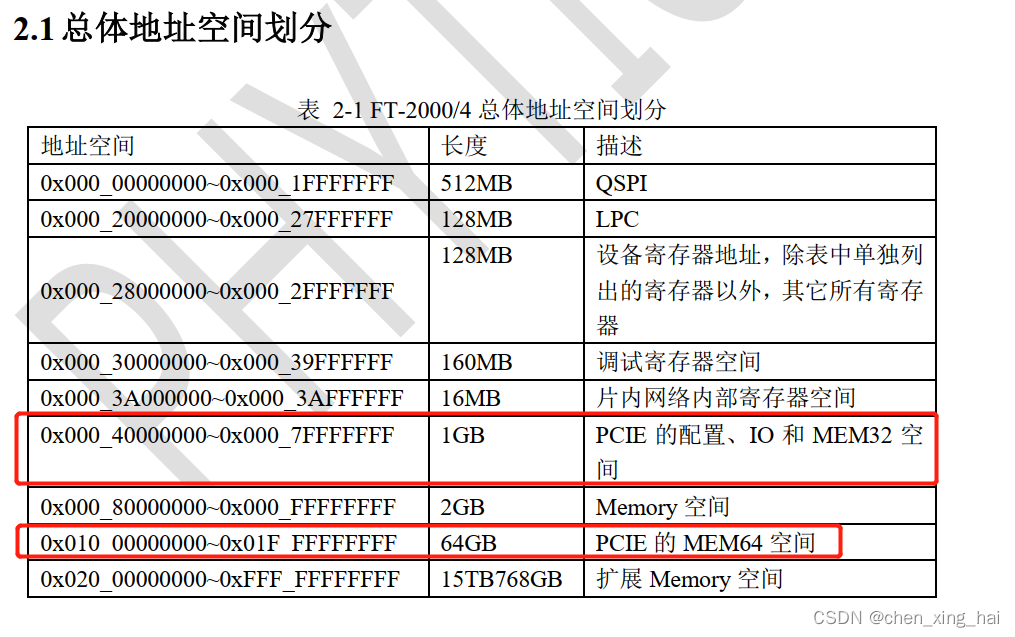

存储器域地址空间指CPU core能访问的所有地址空间,如下图所示的FT2000/4地址分配。

PCI总线域:个人理解应该是PCI事务报文中的地址地段,不一定正确,学习中。

存储器域与PCI总线域彼此独立,通过HOST主桥进行数据交换。HOST主桥是联系存储器域与PCI总线域的桥梁,是PCI总线域实际的管理者。

CPU所能访问的PCI总线地址一定在存储器域中具有地址映射;而PCI设备能访问的存储器域的地址也一定在PCI总线域中具有地址映射。存储器域与PCI总线域的转换关系由HOST主桥统一管理。

有些处理器提供了寄存器进行这种地址映射,如PowerPC的inbound和outbound寄存器组,(PowerPC的RapidIO总线域地址映射也是通过inbound和outbound寄存器组来管理)。有些处理器没有提供类似寄存器,但存储器域与PCI总线域的转换始终存在。

(1)CPU -> PCI设备:处理器,PCI设备所使用的地址空间保存在各自的PCI配置寄存器中,及BAR寄存器中。这些PCI总线地址空间需要在初始化时映射成存储器域的存储器地址空间,之后处理器才能访问这些地址。在PowerPC中此映射关系保存在outbound寄存器组中;在x86及arm中如何保存该映射关系待学习确认(TUDO)。

(2)PCI设备 -> CPU:PCI设备只能访问进行了存储器域与PCI总线域映射的空间。在PowerPC中此映射关系保存在inbound寄存器组中;在x86及arm中如何保存该映射关系待学习确认(TUDO)。

(3)PCI设备 -> PCI设备:如果HOST主桥不支持peer-to-peer传送方式,那么在不同PCI总线域中的PCI设备间不能直接进行数据交换。不同PCI总线域的相同地址映射的存储器域地址可能不相同。

参考文档:《PCI+EXPRESS体系结构导读.pdf》

1592

1592

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?