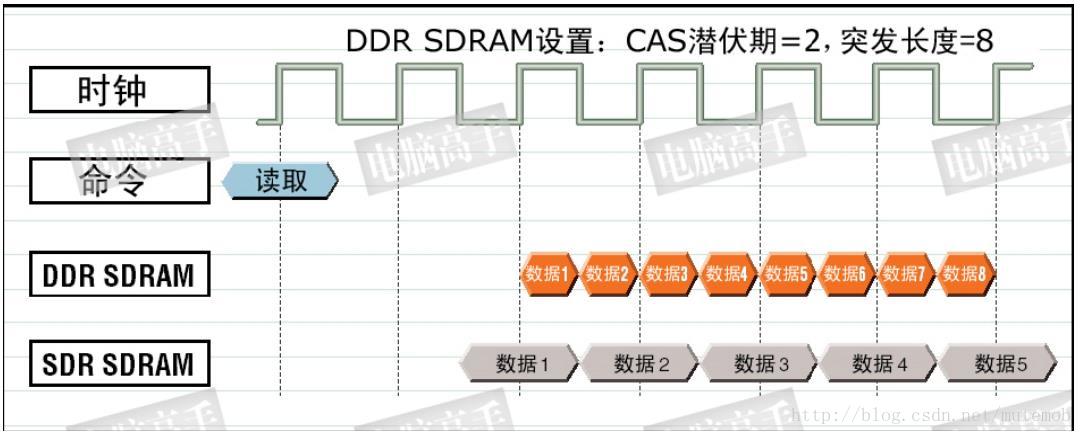

DDR SDRAM 全称为 Double Data Rate SDRAM,中文名为“双倍数据流 SDRAM”。DDR SDRAM 在原 有的 SDRAM的基础上改进而来。下图是DDR和SDRAM的数据传输对比图

图上可以清楚的看到,DDR SDRAM可在一个时钟周期内传送两次数据,上升沿传一次,下降沿传一次。

1.DDR的基本原理

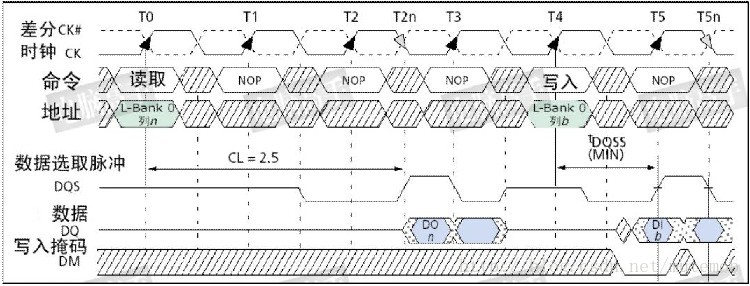

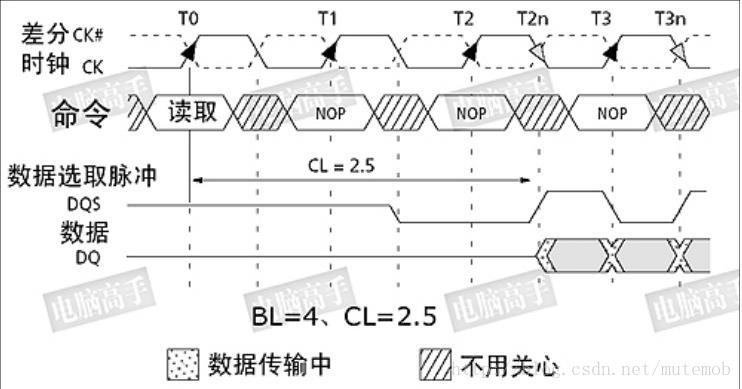

先来看一张DDR读操作时序图

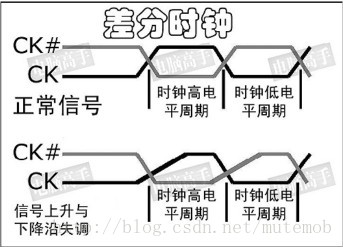

从中可以发现它多了两个信号:CLK#与DQS,CLK#与正常 CLK 时钟相位相反,形成差分时钟信号。而数据的传输在 CLK 与 CLK#的交叉点进行,可见在 CLK 的上升与下降沿(此时正好是 CLK#的上升沿)都有数据被触发,从而实现双倍数据传输,也就是DDR。下面来看DDR的内部结构图的SDRAM有什么不同。

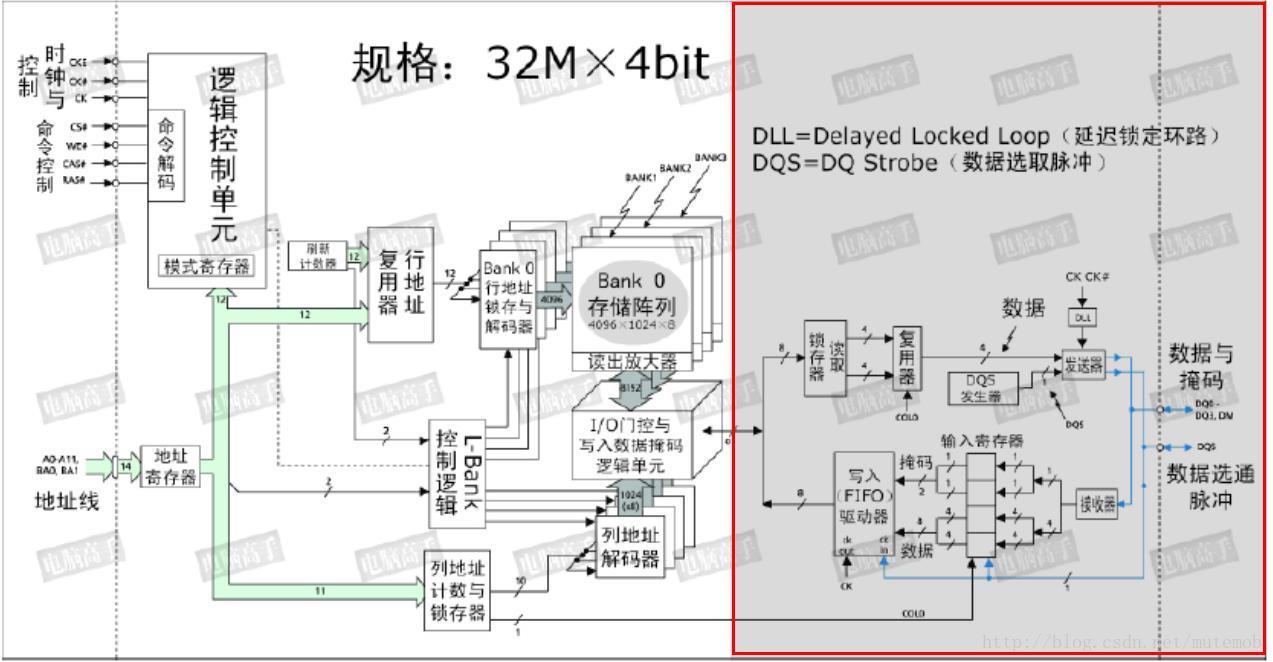

这也是一颗 128Mbit 的内存芯片,标称规格为 32×4bit,右边红框区域就是DDR不同的地方:首先就是内部的L-Bank 规格。SDRAM 中L-Bank 存储单元的容量与芯片位宽相同,但在DDR SDRAM 中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解 SDRAM时“芯片位宽=存储单元容量”的公式了。也因此,真正的行、列地址数量也与同规格 SDRAM 不一样了。

以本芯片为例,在读取时,L-Bank 在内部时钟信号的触发下一次传送 8bit 的数据给读取锁存器,再分成两路 4bit 数据传给复用器,由后者将它们合并为一路 4bit 数据流,然后由发送器在 DQS 的控制下在外部时钟上升与下降沿分两次传输 4bit 的数据给北桥的内存控制器(在ARM和现在的CPU中,内存控制器是集成在CPU中的,现在的PC机中北桥已无内存控制器)。这样,如果时钟频率为 100MHz,那么在 I/O 端口处,由于是上下沿触发,那么就是传输频率就是 200MHz。

现在大家基本明白 DDR SDRAM 的工作原理了吧,这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片 I/O 总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch)。

2.DDR与SDRAM的异同

DDR SDRAM 与 SDRAM 一样,在开机时也要进行 MRS(ModeRegister Set,模式寄存器的设置),不过由于操作功能的增多,DDR SDRAM 在 MRS 之前还多了一 EMRS 阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着 DLL 的有效/禁止、输出驱动强度、QFC 有效/无效等。

CK#的作用, 并不能理解为第二个触发时钟,而是起到触发时钟校准 的作用。

DQS 在读取时与数据同步传输,那么接收时也是以 DQS 的上下沿为准吗?不,如果以 DQS 的上下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各 I/O 端口的出现时间可能有快有慢,会与 DQS 有一定的间隔,这也就是为什么要有一个 tAC 规定的原因(DDR中的tAC是在DQS触发和数据真正出现在I/O总线上的间隔时间)。而在接收方,一切必须保证同步接收,不能有 tAC 之类的偏差。这样在写入时,芯片不再自己生成 DQS,而以发送方传来的 DQS 为基准,并相应延后一定的时间,在 DQS 的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在 DQS 上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

在写入时,以 DQS 的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的接收触发仍为 DQS 的上/下沿。

另外,DDR 内存的数据真正写入由于要经过更多步骤的处理,所以写回时间(tWR)也明显延长,一般在3个时钟周期左右,而在 DDR-Ⅱ规范中更是将 tWR 列为模式寄存器的一项,可见它的重要性。

6.突发长度

在 DDR SDRAM 中,突发长度只有 2、4、8 三种选择,没有了随机存取的操作(突发长度为 1)和全页式突发。这是为什么呢?因为 L-Bank一次就存取两倍于芯片位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据怎么处理?但是,突发长度的定义也与 SDRAM 的不一样了,它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数据。

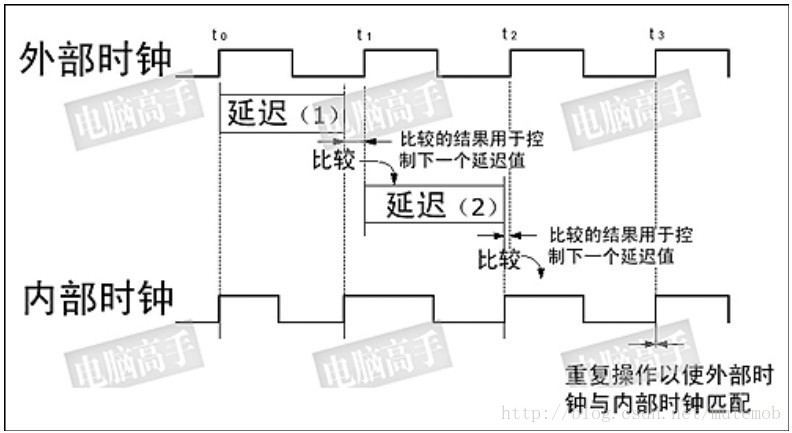

DDR SDRAM 对时钟的精确性有着很高的要求,而 DDR SDRAM 有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上 DDR SDRAM 这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM 也有内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。

CC的方法则是比较内外部时钟的长短,如果内部时钟周期短了,就将所少的延迟加到下一个内部时钟周期里,然后再与外部时钟做比较,若是内部时钟周期长了,就将多出的延迟从下一个内部时钟中刨除,如此往复,最终使内外时钟同步。

CFM 式 DLL 工作示意图

CC 式 DLL 工作示意图

CFM 与 CC 各有优缺点,CFM 的校正速度快,仅用两个时钟周期,但容易受到噪音干扰,并且如果测量失误,则内部的延迟就永远错下去了。CC 的优点则是更稳定可靠,如果比较失败,延迟受影响的只是一个数据(而且不会太严重),不会涉及到后面的延迟修正,但它的修正时间要比 CFM 长。DLL 功能在 DDR SDRAM 中可以被禁止,但仅限于除错与评估操作,正常工作状态是自动有效的。

1246

1246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?