【温故而知新】【3】时钟分频-半整数分频N.5

本次实现是半整数分频,或者叫做N.5分频。实现的方式是通过移位寄存器。这种方式的思路来源于文献“Clock dividers made easy”, writed by Mohit Arora from ST mircoelectronics, LTD。 Mohit Arora 也写过一本书,叫做“The art of hardware architecture”, 由Springer出版,这本书的第四章的内容跟上述论文的内容一致。

实现步骤和方式(N=1)

- 定义移位寄存器的初值,将移位初值定义为3’b001;

- 定义移位寄存器,每个周期将末位的‘1’向左移位1位,移位产生的中间数据跟初值位宽一致,设为tmp。

- 采用将tmp[1]寄存一拍,注意此处采用的时钟信号边沿与移位寄存器时钟边沿相反。设移位之后的信号分别位tmp_1_

- 将tmp[0]、tmp_1_进行 或操作

以下是实现1.5分频的Verilog代码

//===========================================================

// Author: seuchenrui@126.com

//

// Description:

// This is a simple verilog code for clock frequency division

// this code can be used to get

// 1. divided by 1.5

//===========================================================

module iCLK_div_shift_register_15

(

input iCLK,

input iRESET,

output oCLK

);

wire [2:0] tmp_shift;

reg tmp_0_;

reg tmp_1_;

reg [2:0] tmp;

assign tmp_shift = 3'b001;

always@(posedge iCLK or negedge iRESET)

begin

if(!iRESET)

tmp<=tmp_shift;

else

tmp<={tmp[1:0], tmp[2]};

end

always@(negedge iCLK or negedge iRESET)

begin

if(!iRESET)

tmp_1_<=1'b0;

else

tmp_1_<=tmp[1];

end

assign oCLK = tmp[0]|tmp_1_;

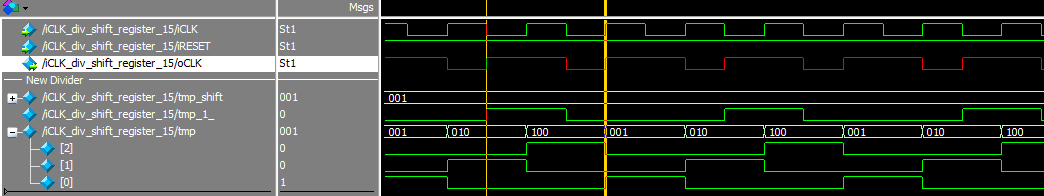

endmodule1.5分频的仿真波形

实现步骤和方式(N>2):

- 定义移位寄存器的初值,比如4.5分频时,将移位初值定义为9’b0_0000_0001,3.5分频时,将移位器初值定义为7’b000_0001,以此类推。

- 定义移位寄存器,每个周期将末位的‘1’向左移位1位,移位产生的中间数据跟初值位宽一致,设为tmp。

- 采用将tmp[0]、tmp[1]、tmp[N]和tmp[N+1]寄存一拍,注意此处采用的时钟信号边沿与移位寄存器时钟边沿相反。设移位之后的信号分别位tmp_0_, tmp_1_, tmp_N_, tmp_N+1_

- 将tmp[0]、tmp[1]、tmp_0_、tmp_N_, tmp_N+1_、tmp[N+1]进行 或操作

以下是实现2.5、3.5、4.5和13.5分频的Verilog代码

//===========================================================

// Author: seuchenrui@126.com

//

// Description:

// This is a simple verilog code for clock frequency division

// this code can be used to get

// 1. divided by 2.5

//===========================================================

module iCLK_div_shift_register_25

(

input iCLK,

input iRESET,

output oCLK

);

wire [4:0] tmp_shift;

reg tmp_0_;

reg tmp_2_;

reg tmp_3_;

reg [4:0] tmp;

assign tmp_shift =

本文介绍了如何使用移位寄存器实现半整数分频,如1.5、2.5、3.5和13.5分频。详细讲解了实现步骤,包括设置移位寄存器初值、移位操作和调整占空比。通过Verilog代码展示了不同分频的仿真波形,并探讨了如何通过增加或操作的信号数来调整分频信号的占空比。

本文介绍了如何使用移位寄存器实现半整数分频,如1.5、2.5、3.5和13.5分频。详细讲解了实现步骤,包括设置移位寄存器初值、移位操作和调整占空比。通过Verilog代码展示了不同分频的仿真波形,并探讨了如何通过增加或操作的信号数来调整分频信号的占空比。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1321

1321

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?