S3C6410的作为ARM11处理器的一种常见型号,与ARM公司和三星公司对MCU的贡献分不开。闲话少说,现在我们来揭开该处理器的时钟控制。

对于一个MCU来说,系统时钟的重要性不言而喻。在该处理器的数据手册中我们可以看到这样的介绍:ARM1176JZF-S core clock rate maximum is 533MHz@1.1 V, 667MHz@1.2V (VDDarm),说明该处理器最高可以达到667MHz。还有更振奋人心的消息:The clock generator consists of three PLLs (Phase Locked Loop) which generate high frequency clock signals up to 1.6GHz,在如此高的时钟频率工作下,处理器的工作能力得到了大大提高。

我们来看下友善板子的原理图:

在该原理图中我们看到提供给S3C6410的时钟为12MHz。这不禁让我们感到迷惑,为什么在如此低的时钟频率下可以实现达到500MHz-600MHz的时钟频率呢?这就是ARM处理器的一个魅力也是让人不容易理解的地方。其实这是由于该处理器拥有一个相位锁存器PLL(phase locked loop)。在S3C6410中有三个PLL,一个用于设置ARMCLK,一个用于HCLK和 PCLK,一个用于外围设备的时钟设置。ARMCLK用于给ARM核提供时钟, HCLK用于AXI/AHB总线, PCLK用于 APB 总线。

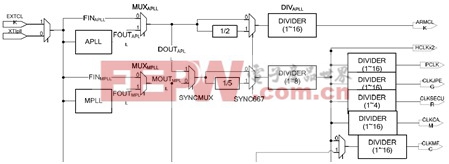

S3C6410的时钟控制器可以产生系统需要的各种时钟信号,如下图所示:

在上图的时钟描述图中,0通道表示系统默认打开,1通道表示系统默认关闭 。当设定相应寄存器后,打开1通道,同时关闭0通道。从上图中可以看出,假如使能XTIpll ,时钟通过0通道经过FINapll利用MUXapll后到达DIVapll后,经过分频,将12MHz的时钟频率提供给ARMCLK,使ARM核工作在12MHz的时钟频率下。如果我们通过配置APLL可以使系统工作在更高的频率。我这个板子是1.1v的核心电压,所以时钟频率只能达到533MHz,若过高,就像电脑的超频一样,会产生让人后悔的结果。我们来分析下APLL如何配置,时系统时钟达到我们需要的523频率。

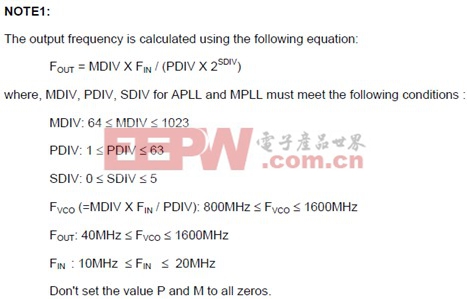

CLK_DIV0寄存器主要用于系统时钟的设置,寄存器意义如下:

APLL、MPLL通过ARM_RATIO 和MPLL_RATIO寄存器来设置。通过设置CLK_DIV0可以实现各种时钟在需要的时钟下。

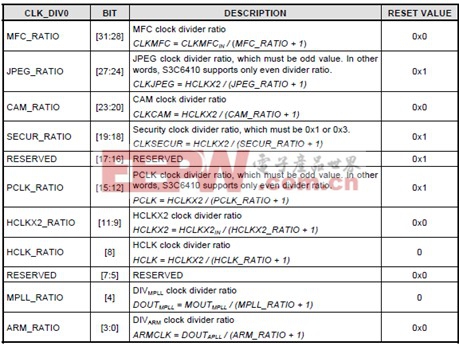

具体设置如下:

我们确定MDIV为266,PDIV为3,SDIV为1,则FOUT=266*12/(3*21)=532MHz, 这样就可以完成我们的高频率工作了。APLL_CON寄存器各位意义如下:

我们确定MDIV为266,PDIV为3,SDIV为1,则FOUT=266*12/(3*21)=532MHz,

这样就可以完成我们的高频率工作了。具体设置如下:

![]()

下面来看下系统如何达到你想需要的时钟频率:

当系统供电后,复位开关为低时,XTIpll开始起振在12MHz,当复位开关为高时,系统时钟开始开始工作在12MHz,这时通过设置PLL LOCK时间,在这段时间内,VCO可以使系统的时钟达到我们需要的532MHz,通过设置时钟源选择控制器低三位为1来使用532MHz的时钟,这时,系统就达到了532MHz了。其余的时钟设置也如此。

2140

2140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?