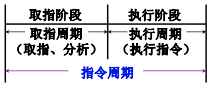

1. 指令周期

指令周期是指_

CPU从主存取出一条指令, 分析指令,加上执行这条指令的时间。

1.1指令周期

指令周期: 是指cpu,从内存中取出指令,并且执行一条指令所需要的全部时间。

比如 从内存单元中,取出操作数,使用操作码add, 与acc寄存器中的值相加,结果保存在acc寄存器中。

取指周期:要访问一次内存, 将指令从内存中取出,送入到cpu。

执行周期: 也访问一次内存,将操作数从内存中取出,送入到cpu中, 执行加法操作。

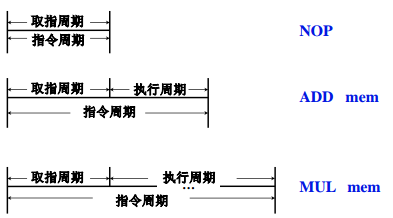

1.2 每条指令的指令周期不同

取指周期,要访问一次内存, 将指令从内存中取出,送入到cpu。

执行周期: 也访问一次内存,将操作数从内存中取出,执行对应的运算,将结果保存在寄存器中。

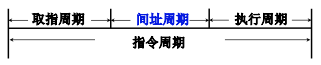

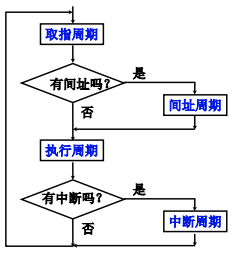

1.3 具有间接寻址的指令周期

取指周期,要访问一次内存, 将指令从内存中取出,送入到cpu。

间址周期:访问一次内存,将操作数的地址从内存中取出。

执行周期: 也访问一次内存,将操作数从内存中取出,执行对应的运算,将结果保存在寄存器中。

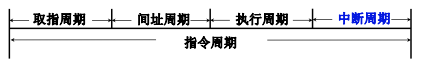

1.4 带有中断周期的指令周期

中断周期:保护断点, 形成中断服务程序的入口地址, 关中断。

1.5 指令周期流程

根据CPU访存的性质不同,可将CPU的工作周期分为取指周期、间址周期、执行周期和中断周期。

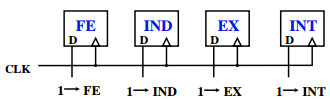

1.6 CPU 工作周期的标志

控制器在指令周期的阶段,

要发出不同的控制命令,

控制器也需要知道当前处于指令周期的何种阶段。

CPU 访存有四种性质

| 具体操作 | 周期阶段 |

|---|---|

| 取指令 | 取指周期 |

| 取地址 | 间址周期 |

| 存取操作数或结果 | 执行周期 |

| 存程序断点 | 中断周期 |

使用D触发器,对指令周期中不同的阶段进行标识

2. 指令周期的数据流

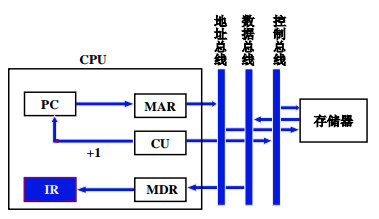

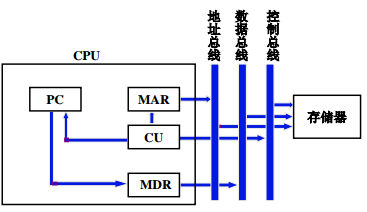

2.1取指周期数据流

MAR: 要访问存储器的地址,保存在MAR中。

MDR: 从存储器中取出的数据(或者指令),放在MDR当中。

IR:取值周期中,取回的是指令,保存在IR当中,IR寄存器专门用于保存指令。

CU:所有部件的运行通过CU控制;

具体来讲,

CU向存储器发出读信号。

cu 控制,准备下一条指令的地址, 将pc+1 的值保存在pc总;

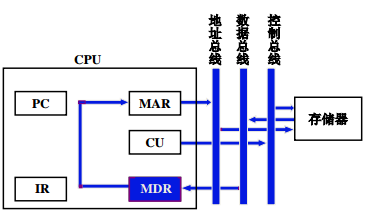

2.2 间址周期数据流

一旦取指周期结束,CU便检查IR中的内容,以确定其是否有间址操作。

要取出的操作数,所在存储器当中的地址保存在MDR 当中;

将MDR中存储的地址输入到MAR当中。

2.3 执行周期数据流

不同指令的执行周期数据流不同

2.4 中断周期数据流

1. 保存断点;CU控制,将程序断点保存在内存单元中的哪个地址当中,将cu中的地址存放在MAR当中, MAR将数据存放在地址总线当中, 这里要保存的断点,是中断之后,需要返回程序的位置,代表了中断恢复之后,需要执行下一条指令的地址,该地址保存在pc当中,pc将该值保存在MDR当中。

2.形成中断服务程序的入口地址, 该地址同样也是由cu给出,并且写入到pc当中。

3.硬件,关中断;

3. 指令流水

3.1如何提高机器速度

-

- 提高访存速度

高速芯片, Cache, 多体并行

- 提高访存速度

多体并行:cpu在一个主存周期当中,对多个存储器进行交叉访问, 多个存储体对cpu提供数据。

-

- 提高 I/O 和主机之间的传送速度

中断, DMA, 通道, I/O 处理机, 多总线

- 提高 I/O 和主机之间的传送速度

-

- 提高运算器速度

高速芯片 改进算法 快速进位链

- 提高运算器速度

为了提高运算速度,可以采用高速芯片和快速进位链,以及改进算法等措施

• 提高整机处理能力

高速器件 改进系统结构 ,开发系统的并行性

3.2 系统的并行性

- 并行包含同时性和并发性两个方面:

同时:是指两个或多个事件在同一时刻发生,

并发: 是指两个或多个事件在同一时间段发生。

- 并行性的等级

过程级(程序、进程), 粗粒度, 软件实现

指令级(指令之间), 指令内部, 细粒度, 硬件实现

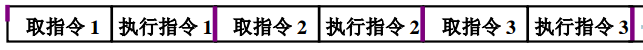

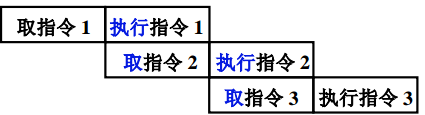

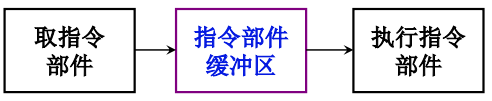

3.3指令流水原理

- 指令的串行执行

取指令 取指令部件 完成 总有一个部件 空闲

执行指令 执行指令部件 完成

- 指令的二级流水

若 取指 和 执行 阶段时间上 完全重叠

指令周期 减半 速度提高 1 倍

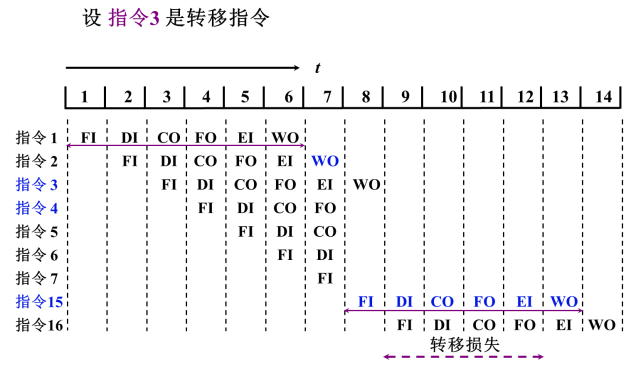

3.4 影响指令流水效率加倍的因素

- 执行时间 > 取指时间:

条件转移指令:

是影响指令流水效率加倍的一个因素,当遇到条件转移指令时,下一条指令是不可知的,因为必须等到执行阶段结束后,才能获知条件是否成立,从而决定下条指令的地址,造成时间损失。

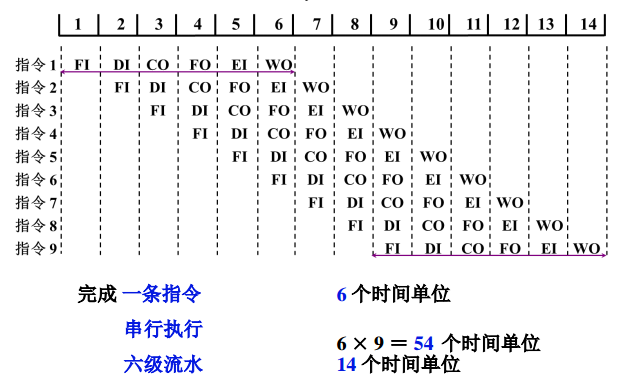

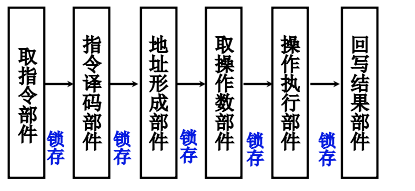

3.5 指令的六级流水

| 指令 | 作用 |

|---|---|

| FI | 取指令 |

| DI | 指令译码 |

| CO | 形成操作数地址 |

| FO | 取操作数 |

| EI | 执行操作 |

| WO | 结果写回 |

结果写回, 是指将运行结果写回到给定寄存器当中, 或者写回到给定的内存单元当中。

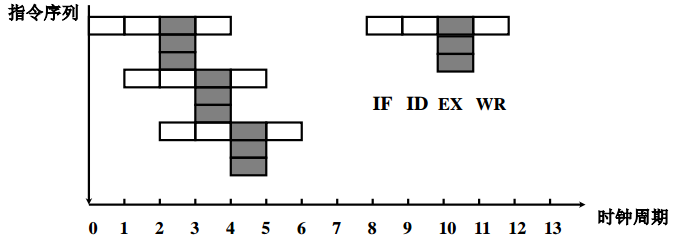

4. 影响指令流水线性能的因素

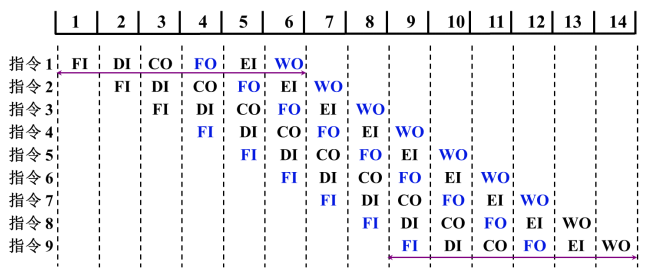

4.1结构相关

不同指令争用同一功能部件产生资源冲突.

如图中,第四时间段, FO,FI这两条指令同时访问内存;

解决访存冲突的一种办法是设置两个独立的存储器分别存放操作数和指令,以免取指令和取操作数同时进行时互相冲突,使取某条指令和取另一条指令的操作数实现时间上的重叠。

解决办法:

• 停顿, 将冲突的指令,其中一个停顿到下一个时间段运行。

• 指令存储器和数据存储器分开, 指令cache, 数据cache 分开;

• 指令预取技术 (适用于访存周期短的情况),访问内存快,取指部件,利用空闲时间,将多条指令从内存单元中取出,放到cpu中的指令缓冲队列, 减少对内存访问时发生的冲突。

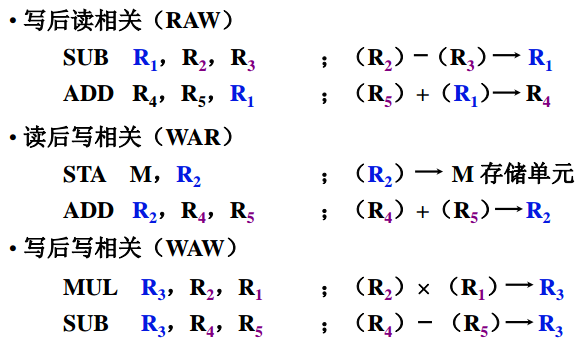

4.2数据相关

不同指令因重叠操作,可能改变操作数的 读/写 访问顺序.

- 写后读相关:

对某一个存储单元,或者是寄存器,需要先完成写操作,在完成读操作。

如图中的减法,加法操作; 由于加法操作使用到R1寄存器中的内容,所以必须先对R1寄存器进行写操作,然后对R1进行读操作。

- 读后写:

STA, 将R2中的内容存储到M内存单元中,需要先读;

然后,将加法的结果使用写操作,存放到R2中。

解决办法:

-

后推法,必须等前一条指令结束,然后才执行后续指令。

-

采用 旁路技术;

相当于使用了一种短路连接的方式,即在加法操作后,得到的结果,在还没写入到R1寄存器中时候,先使用一个短路连接到结果,将运算结果取出。

4.3控制相关

控制相关主要是由转移指令引起的。

条件判断相关的指令,必须等到判断的结果,才能知道执行下一条何种指令。

由转移指令引起;

5. 流水线性能

5.1 吞吐率

吞吐率:

单位时间内 流水线所完成指令 或 输出结果 的 数量;

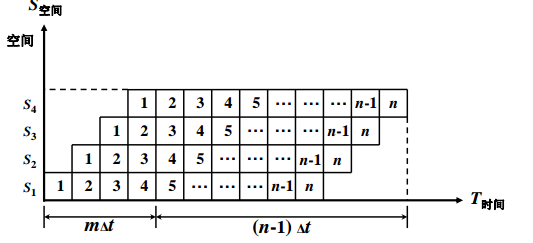

设 m 段的流水线各段时间为Δt

• 最大吞吐率:

指流水线满负荷运转,没有发生资源冲突。

T p m a x = 1 Δ t T_{pmax} = \frac{1}{Δt} Tpmax=Δt1

• 实际吞吐率

连续处理 n 条指令的吞吐率为

一条指令需要的运转时间为:m Δt;

(n-1)条指令所需要的时间为 (n-1) ·Δ t。

T p = n m ⋅ Δ t + ( n − 1 ) ⋅ Δ t T_{p}= \frac{n} {m ·Δt + (n-1) ·Δ t} Tp=m⋅Δt+(n−1)⋅Δtn

5.2 加速比

流水线的加速比是指m段流水线的速度与等功能的非流水线的速度之比。

m 段的 流水线的速度 与等功能的 非流水线的速度 之比;

设流水线各段时间为 Δ t: ;

-

完成 n 条指令在 m 段流水线上共需:

T = m ⋅ Δ t + ( n − 1 ) ⋅ Δ t T= {m ·Δt + (n-1) ·Δ t} T=m⋅Δt+(n−1)⋅Δt -

完成 n 条指令在等效的非流水线上共需:

T p = n m ⋅ Δ t T_{p}= {nm ·Δt } Tp=nm⋅Δt

加速比: 没有采用流水线消耗的时间/ 采用流水线所使用的时间。

S p = n m ⋅ Δ t m ⋅ Δ t + ( n − 1 ) ⋅ Δ t S_{p}= \frac{nm ·Δt } {m ·Δt + (n-1) ·Δ t} Sp=m⋅Δt+(n−1)⋅Δtnm⋅Δt

= n m m + n − 1 = \frac{nm}{ m+ n-1} =m+n−1nm

5.3 效率

流水线中,硬件的使用率。

流水线中各功能段的 利用率

由于流水线有 建立时间 和 排空时间

因此各功能段的 设备不可能 一直 处于 工作 状态

流水线中各功能段的 利用率:

效率=

流水线各段处于工作时间的时空区

流水线中各段总的时空区

\frac{流水线各段处于工作时间的时空区}{流水线中各段总的时空区}

流水线中各段总的时空区流水线各段处于工作时间的时空区

S p = n m ⋅ Δ t m ⋅ ( m + n − 1 ) ⋅ Δ t S_{p}= \frac{nm ·Δt } {m · (m+ n-1) ·Δ t} Sp=m⋅(m+n−1)⋅Δtnm⋅Δt

6. 流水线的多发技术

同时使用多条流水线,

有几条指令同时进入到不同的流水线当中进行解释。

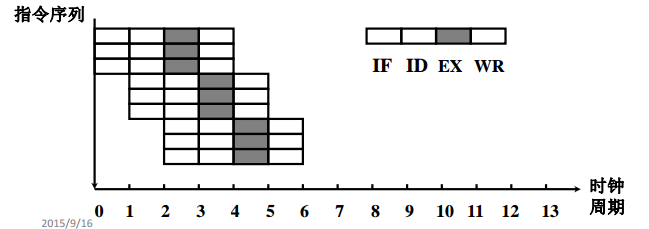

6.1 超标量技术

每个时钟周期内可 并发多条独立指令

配置多个功能部件

不能调整 指令的 执行顺序

通过编译优化技术,把可并行执行的指令搭配起来

IF: 取指令

ID: 指令译码

EX: 执行指令

WR: 写回指令;

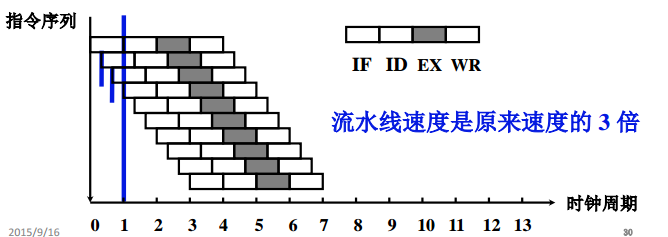

6.2 超流水线技术

在 一个时钟周期 内 再分段 ( 3 段)

在一个时钟周期内 一个功能部件使用多次( 3 次)

不能调整 指令的 执行顺序

靠编译程序解决优化问题

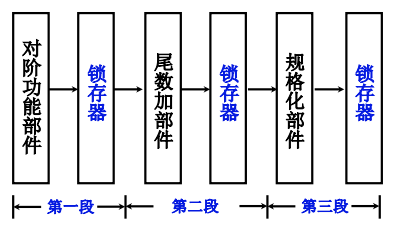

在流水线的设计过程中,流水段之间需要加入锁存器的。

把每一个流水段的执行结果在锁存器当中,进行锁存。作为下一个流水段,执行的时候,控制信号或者操作信号的

6.3超长指令字技术

由编译程序 挖掘 出指令间 潜在 的 并行性,

将 多条 能 并行操作 的指令组合成 一条

- 具有 多个操作码字段 的 超长指令字(可达几百位)

- 采用 多个处理部件

超长指令技术利用在程序编译时指令间潜在的并发性,把多条能并行操作的指令结合成一条具有多个操作码字段的超长指令,需要多个功能部件同时工作。

7. 流水线结构

7.1 指令流水线

完成一条指令分 6 段, 每段需一个时钟周期

- 若 流水线不出现断流 1 个时钟周期出 1 结果

- 不采用流水技术 6 个时钟周期出 1 结果

理想情况下, 6 级流水 的速度是不采用流水技术的6 倍

7.2 运算流水线

完成 浮点加减 运算 可分

对阶、尾数求和、规格化 三段

分段原则 每段 操作时间 尽量 一致

760

760

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?