2.1微处理器概述

1)微处理器的功能

- 能够进行算术和逻辑运算

- 能对指令进行译码、寄存并执行指令所规定的操作

- 具有与存储器和I/O接口进行数据通信的能力

- 少量数据的暂存

- 提供系统所需的定时和控制信号

- 能够响应输入输出设备发出的中断请求

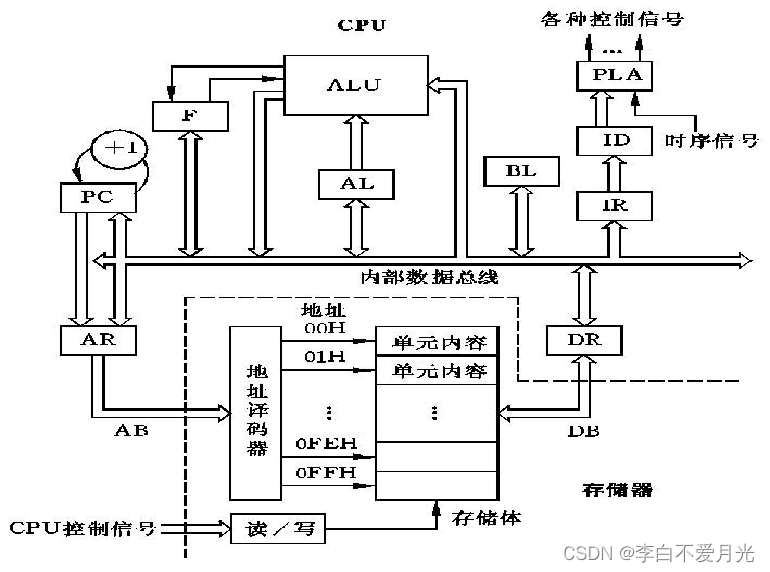

2)运算器

1.组成:运算器由算术逻辑单元、通用或专用寄存器组及内部总线三个部分组成

2.说明:

- ALU的内部包括负责加、减、乘、除运算的加法器以及实现与、或、非、异或等逻辑运算的逻辑运算功能部件。

- CPU内部总线:CPU内部用于传送数据和指令的传送通道

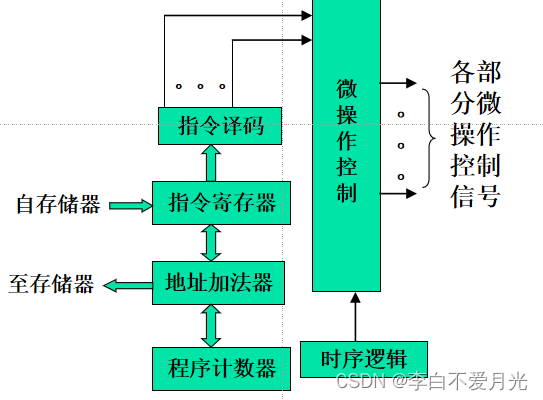

3)控制器

1.功能:

- 指令控制:控制器要能根据指令所在的地址,按顺序或在遇到转移指令时按照转移地址取出指令,分析指令,传送必要的操作数,并在指令执行结束后存放运算结果

- 时序控制:指令的执行是在时钟信号的严格控制下进行的。

- 操作控制:根据指令流程,确定在指令周期的各个节拍中要产生的微操作控制信号,有效地完成各条指令的操作过程。

2.内部组成:

- 程序计数器PC

- 指令寄存器IR

- 指令译码器ID

- 时序控制部件

- 微操作控制部件

2.2 8088/8086 微处理器

1)8088/8086 CPU的特点和构造

1.8086 CPU有16根数据线和20根地址线(可寻址的地址空间是220=1MB);8086的指令暂存队列为6个字节;

2.8088 CPU它的内部寄存器、内部运算部件以及内部操作都是按16位设计的,但对外的数据总线只有8位。(准16位处理器);指令暂存队列为4个字节;

3.8088/8086的功能特征:

- 指令采用并行流水线处理方式

执行单元EU:负责分析指令和执行指令

总线接口单元BIU:负责取指令、取操作数和写结果。

- 对内存空间实行分段管理

将内存分为4个段并设置地址段寄存器,以实现对1MB空间的寻址

- 每段64KB,用段基地址和段内偏移实现对1MB内存空间的寻址

- 支持多处理器系统

具有最小和最大两种工作模式以及内置的多任务处理能力,可通过模式选择引脚进行选择

- 片内无浮点运算部件,浮点运算由数学协处理器8087支持(或用软件模拟)

2)8088 CPU的外部引脚及其功能

1.8088和8086都是具有40条引出线的集成电路芯片,采用双列直插式封装

2.8088/8086的最大和最小两种工作模式可以通过MN/#MX引脚来选择

- 当MN/#MX=1时,工作在最小模式。此时,构成的系统中只允许有一个处理器,所有控制信号直接由8088/8086提供。

- 当MN/#MX=0时,工作在最大模式。此时,构成的系统中除了有8088/8086之外,还可以接另外的处理器(如8087数学协处理器)。在最大模式下,CPU并不直接向外界提供全部控制信号,而由S0、S1、S2通过8288总线控制器提供。引脚图中括号内的信号用于最大模式。

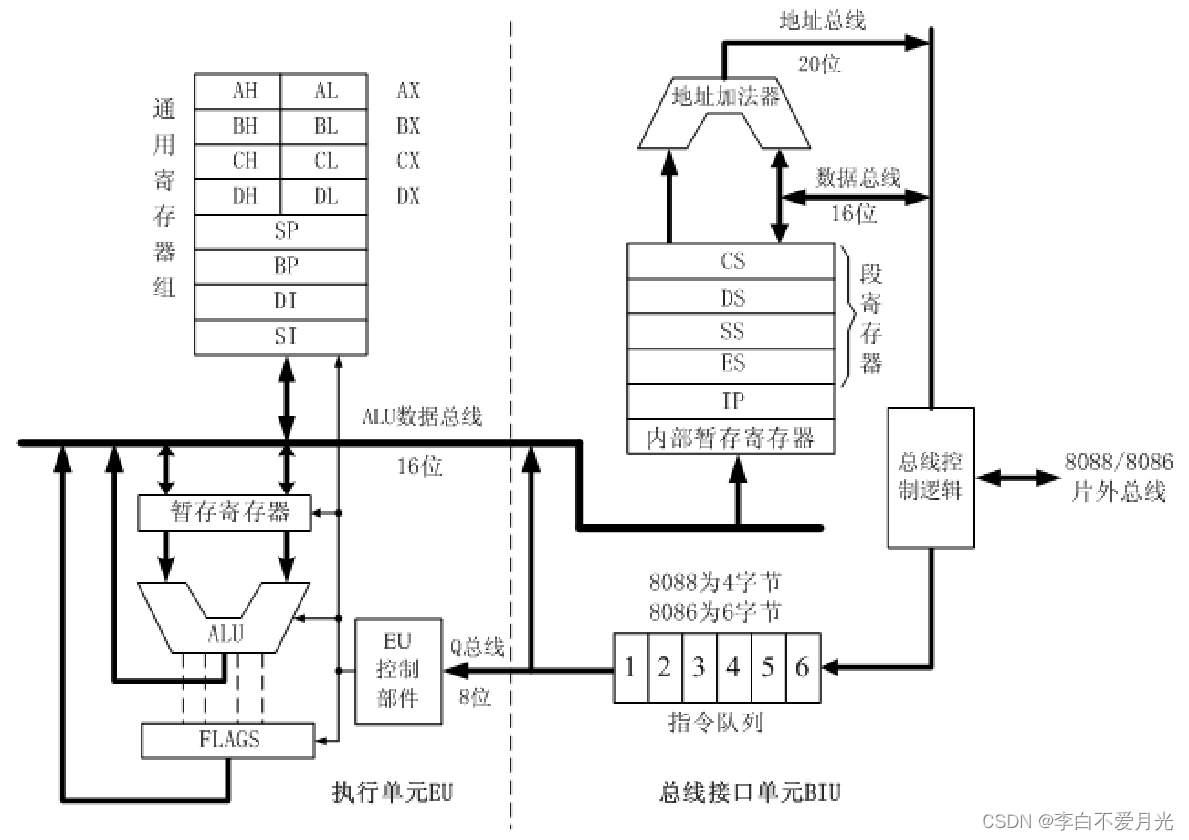

3)8088/8086的功能结构

1.8088/8086的内部结构从功能上分成两个单元/并行执行

- 总线接口单元BIU:管理8088与系统总线的接口;负责CPU对存储器和外设进行访问

- 指令队列缓冲器:暂时存放BIU从存储器中预取的指令

- 总线控制逻辑:以控制逻辑方法实现分时传送信息

- 地址加法器:物理地址=段地址×16d+偏移地址

- 段寄存器:CS、DS、SS、ES

- 指令指针寄存器

- 执行单元EU:负责指令的译码、执行和数据的运算

- 算术逻辑单元:处理各种数据

- 数据暂存寄存器:暂存数据

- 标志寄存器:存放运算结果的状态特征和设置控制标志

- EU控制器:程序计数器:下一条要取出的指令;指令译码器:译码和分析;从队列中取指令、译码、产生控制信号等

- 通用数据寄存器组:存放数据(数据、中间结果、地址)

- 地址指针和变址寄存器:存放地址信息(偏移地址)

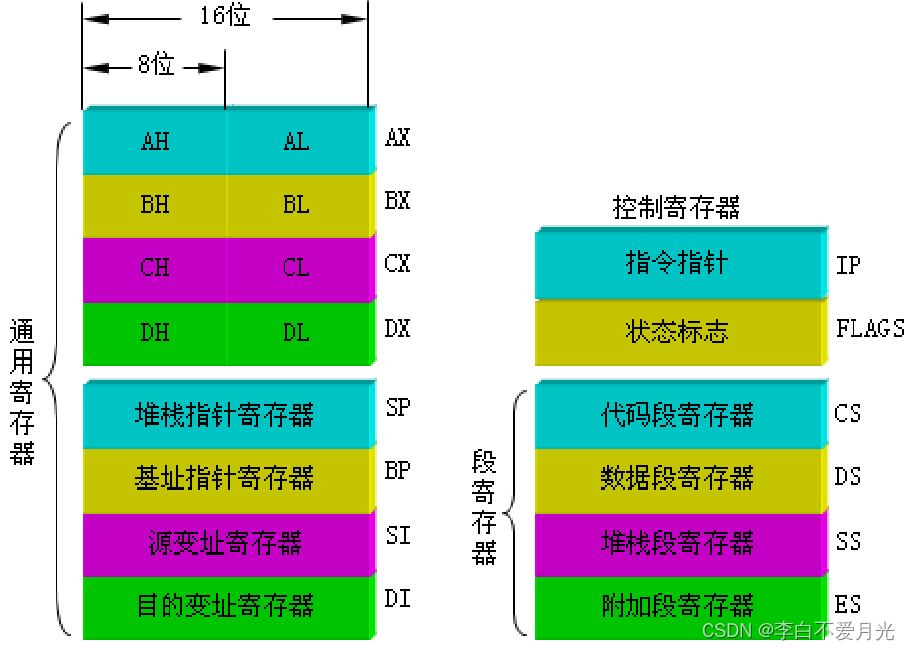

2.8088/8086的寄存器结构(均为16位)

- 8个通用寄存器

(1)数据寄存器: AX累加器 BX基址寄存器 CX计数器 DX数据寄存器

(2)变址寄存器: SI源地址寄存器 DI目的地址寄存器

(3)指针寄存器: BP基址指针寄存器 SP堆栈指针寄存器

- 4个段寄存器

CS:代码段寄存器 存放指令代码

DS:数据段寄存器 存放操作数

ES:附加段寄存器 存放操作数

SS:堆栈段寄存器 指示堆栈区域的位置

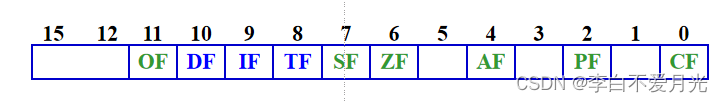

- 1个标志寄存器

标志(Flag)用于反映指令执行结果或控制指令执行形式

8088处理器的各种标志形成了一个16位的标志寄存器FLAGS(程序状态字PSW寄存器)

进位标志CF:有进位:CF = 1

奇偶标志PF:当运算结果最低字节中“1”的个数为零或偶数时,PF=1

辅助进位标志AF:运算时D3位(低半字节)有进位或借位时,AF=1

零标志ZF:若运算结果为0,则ZF=1

符号标志SF:运算结果最高位为1,则SF=1

溢出标志OF:若算术运算的结果有溢出,则OF=1

陷阱标志TF:设置TF=1,处理器单步执行指令

中断允许标志IF:设置IF=1,则允许中断

方向标志DF:设置DF=1,存储器地址自动减少

- 1个指令指针寄存器

IP(Instruction Pointer)为指令指针寄存器,指示主存储器指令的位置。

4)8088/8086的存储器结构

1. 数据的存储格式

- 计算机中信息的单位

二进制位Bit:存储一位二进制数:0或1

字节Byte:8个二进制位,D7~D0

字Word:16位,2个字节,D15~D0

双字DWord:32位,4个字节,D31~D0

- 存储单元及其存储内容

每个存储单元都有一个编号,被称为存储器地址;每个存储单元存放一个字节的内容

2.存储器的分段管理

- 8088CPU有20条地址线

- 8088CPU将1MB空间分成许多逻辑段

- 一个存储单元除具有一个唯一的物理地址外,还具有多个逻辑地址

3.物理地址和逻辑地址

物理地址

- 8088CPU存储系统中,对应每个物理存储单元都有一个唯一的20位编号,就是物理地址,从00000H ~ FFFFFH

- 分段后在用户编程时,采用逻辑地址,形式为 段基地址 : 段内偏移地址

如:物理地址 14700H 逻辑地址 1460H:100H

逻辑地址

- 段地址说明逻辑段在主存中的起始位置

- 8088规定段地址必须是模16地址:xxxx0H

- 偏移地址说明主存单元距离段起始位置的偏移量

物理地址和逻辑地址的转换

- 将逻辑地址中的段地址左移4位,加上偏移地址就得到20位物理地址

4.段寄存器的使用

8088有4个16位段寄存器

- CS(代码段)指明代码段的起始地址

- SS(堆栈段)指明堆栈段的起始地址

- DS(数据段)指明数据段的起始地址

- ES(附加段)指明附加段的起始地址

每个段寄存器用来确定一个逻辑段的起始地址,每种逻辑段均有各自的用途

逻辑段的分配

- 程序的指令序列必须安排在代码段

- 程序使用的堆栈一定在堆栈段

- 程序中的数据默认是安排在数据段,也经常安排在附加段,尤其是串操作的目的区必须是附加段

- 数据的存放比较灵活,实际上可以存放在任何一种逻辑段中

8088/8086的工作时序

2.3 系统总线

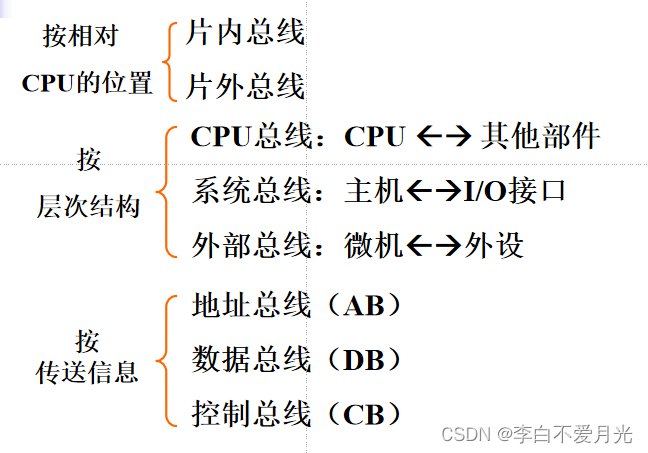

1)总线的基本概念和分类

1.概念:是一组导线和相关的控制、驱动电路的集合。是计算机系统各部件之间传输地址、数据和控制信息的公共通道

2.分类:

2)总线技术

传输同步——协调通信双方的传输操作

总线仲裁——消除多个设备同时使用总线造成的冲突现象

出错处理

信号驱动

3)常用系统总线标准

- ISA(Industry Standard Architecture)是工业标准体系结构总线的简称

- PCI(Peripheral Component Interconnect)是外设互连总线的简称

- PCI Express,简称PCIe或PCI-E,是微机系统中一种用来代替PCI、AGP接口规范的新型系统总线标准。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?