大家都知道,面试的表现会对于个人职业发展的重要性,不仅能决定是否录用,还会影响到后期的谈薪,所以面试前一定要做好充分的准备。

今天IC修真院为大家带来了数字IC后端的面试题目,希望大家能够用得上。

面试题目(文末可全领)

1.route 之前的连线和后面最终的连线有什么区别?

Route 之前,实验布线,把线连起来就行,只看最基本的 drc rule,速度很快。 最终布线,关心所有的 drc 规则,速度较慢。

2.请说一下标准单元的延迟与哪些因素有关?

此题经常容易被作为笔试题,考察学生的时序基础理解能力 本质上,standard cell delay 由 cell 的 input transition 和 output load 决定 PVT作为外部条件,也会影响到 cell 的 delay。应该理解到 PVT 与 delay 的关 系是怎么样?

建议: 比较全面的回答是在同一种 PVT 条件下,cell delay 由 inputtransition 和 output load 决定

3.请列举几个你知道的sdc命令,并说出它的用途?

回顾常见的sdc命令:描述芯片的工作速度,即时钟的频率,包括 create_clock,create_generated_clock 等 2 描述芯片的边界约束,包括 set_input_delay,set_output_delay 等描述芯片的一些设计违反 rule(DRV),包括 set_max_fanout,set_max_capacitance, set_max_transition 等 描述设计中一些特殊的路径,包括 set_false_path, set_multicycle_path 等 。

4.描述设计中一些需要禁止的timing arc,例如 set_disable_timing5.请说一下 drv 的概念,主要包含哪些内容?

Max transition, max capacitance, max fanout 为什么优先修复,需要记牢 可以特意和面试官指出:max fanout 不需要修复。

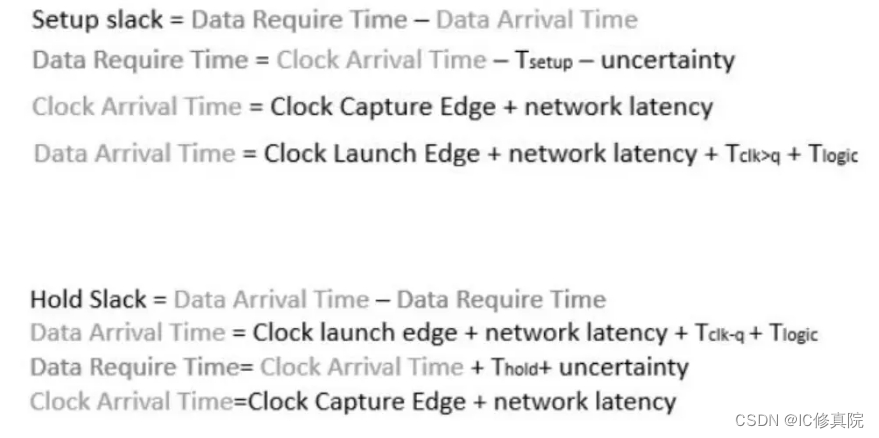

5.请写一下 setup, hold slack 的计算公式

6. 列举你知道的几种修复 setup timingviolation 的方法,该优先使用哪一 种?

1 减小 data path 的 delay Vt Swap, HVT>RVT, RVT>LVT 插入 BUF (线太长,fanout 过大) Size up cell(增强驱动) 走高层线。

2.增加 capture clock path delay 需要注意:加 buf 在 capture clockendpoint 前面 并且检查: 下一级 path 是不是有 setup slack margin 该级register 的 input pin 上的有没有 hold margin。

7.列举一下你知道的修复 hold timing violation 的方法?

经典必问题 增加 data path 上的 delay Endpoint 上插 buffer/delay cell讲师建议:面试官一般会引申出去,接着问你 buffer 插在什么位置 优先采用delay cell 还是 buffer, 这两者的优缺点。

8.在修复 hold violation 时,delay cell 和 buffer 该优先使用哪一种,各有什么优缺点?

Violation 较大时,优先使用 delay cell;较小时,优先使用 buffer。Delaycell 面积上占优势,但是驱动能力较弱。

9. 在生成 clock tree 时,我们应该使用 invertor 还是 buffer,为什么?

优先采用 invertor,clock invertor 具有整流作用,可以有效避免 min pulsewidth 的问题。

10. sdc 文件里,主要包含哪些内容,我们该如何约束一个设计

描述芯片的工作速度,即时钟的频率,包括 create_clock,create_generated_clock 等 描述芯片的边界约束,包括 set_input_delay,set_output_delay 等描述芯片的一些设计违反 rule(DRV),包括 set_max_fanout,set_max_capacitance, set_max_transition 等 描述设计中一些特殊的路径,包括 set_false_path, set_multicycle_path 等 描述设计中一些需要禁止的timing arc,例如 set_disable_timing。

11. create_clock 和 create_generate_clock 有什么区别

主要区别在于 CTS 过程中 generate clock 会继承 source clock 的 latency。

12.请说一下 OCV 的概念,为什么需要用到 OCV,什么阶段需要 OCV,如何 实现?

回顾课程上关于 OCV 的介绍。 OCV,较为悲观的时序计算模式。Cell PVT在实际芯片上不可能落在一个点 上,有可能是一个范围,利用 crpr 消除悲观量。

13.请说一下 memory 的摆放规则?

大的 Macro 尽量贴边摆放 同一个模块里面的 Macro 经可能放在一起 Macro与 Macro 之间要留有一定空隙,给予布线资源。

14.为什么 memory 需要靠边摆放?

给 core 区域留出一个规整的区域摆放标准单元17. 如何判断 floorplan 摆放质量的好坏?两个要素,congestion 和 timing。

15.如何判断 floorplan 摆放质量的好坏?

两个要素,congestion 和 timing。

需要上述面试题目的同学可按需领取,点击下方链接可以直接分享给大家~

这里放个口:数字IC后端面试题目

975

975

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?