产品设计中的静电(ESD)防护

本文介绍了静电放电(ESD)的定义、测试目的、实质和特点、危害、ESD指标以及如何提高产品的ESD指标,可供产品硬件设计或测试过程中参考。

1、静电放电的定义

静电放电(Electrostatic discharge,ESD):具有不同静电电位的物体相互靠近或直接接触引起的电荷转移。

2、静电放电测试目的

测试单个设备或系统的抗静电放电干扰的能力。用于模拟操作人员或者物体在接触设备时的放电。

3、静电放电的实质和特点

静电放电的实质是一个带电物体接近一个电位不相等的导体或者接地导体时,带电导体上的电荷会通过另一个导体或者接地导体释放;

静电放电的特点是干扰信号会就近泄放到电位相对较低的导体上;

4、静电放电干扰途径及危害

静电放电是一种高能量、款频谱的电磁骚扰,它主要通过两种途径来干扰被测设备:

(1)直接能量,主要是瞬间接触的大电流造成内部电路的误动作或损坏;

(2)空间耦合,由于ESD的前沿时间很短,约0.7ns,其频谱范围可以达到数百兆赫,稍微长一点的导线都可能形成有效的耦合。

静电放电干扰对设备的危害有:

(1)损坏半导体器件;

(2)造成设备误动作;

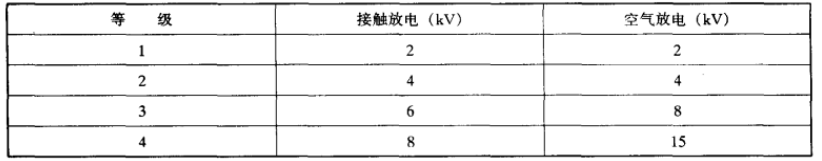

5、静电放电(ESD)指标

6、如何提高产品ESD性能指标

考虑到静电干扰产生的途径,主要从提供泄放路径和屏蔽静电泄放过程产生的电磁场两个方面解决静电放电的干扰:

(1)提高接地导体的电连续性,让静电放电能量从良好的接地路径放走,而使设备内部的任何电路、器件和信号不受静电能量的直接干扰;

(2)金属外壳的设备,对外接口采用金属接口,360°搭接,使它与金属外壳具有良好的接地特性。对于设备的信号接口,连接器件的选择及结构的设计要避免静电放电干扰信号直接耦合到信号线中;

(3)内部线路板地平面的完整性,提供低阻抗的泄放路径。

(4)易受静电放电干扰的电路有必要增加瞬态抑制电路或者滤波电路。

(5)复位等敏感信号线不能布在PCB板的边缘,应远离PCB板边缘1cm以上。同时,对于比较敏感的电路或芯片,在PCB设计、布局时要尽量远离ESD放电点。

(6)增大产品内部电路与外壳之间的间隙(接触点周围空气击穿距离:空气放电8kV至少需要6mm,15kV至少12mm以上-这个经验值待验证);

备注:实践证明,具有长宽比小于5的没有任何缝隙、通孔的单一金属导体具有良好的电连续性;

这里只是记录整理个人开发中的经验,如有不足,还望在评论中不吝指教。

1843

1843

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?