Fpga的vga显示设计

1.VGA原理

Vga端口一个有15根线,可以百度查看一下VGA端口的定义,这里就不多说了,现在能用到只有5根线,分别是行同步信号输入(h_sync),场同步信号输入(v_sync),红色信号输入(R)、绿色信号输入(G)、蓝色信号输入(B) 。本次实验主要用640x480的分辨率在友晶开发板de2-115上进行开发,所以需要了解VGA有关的时序。

一般VGA扫描的顺序是从左到右,从上到下的方式,理论上一帧要扫640*480的像素点,但实际上还需要考虑同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四部分。另外VGA工业标准显示模式要求:行同步,场同步都为负极性,即同步脉冲要求是负脉冲。

行扫描图

场扫描图

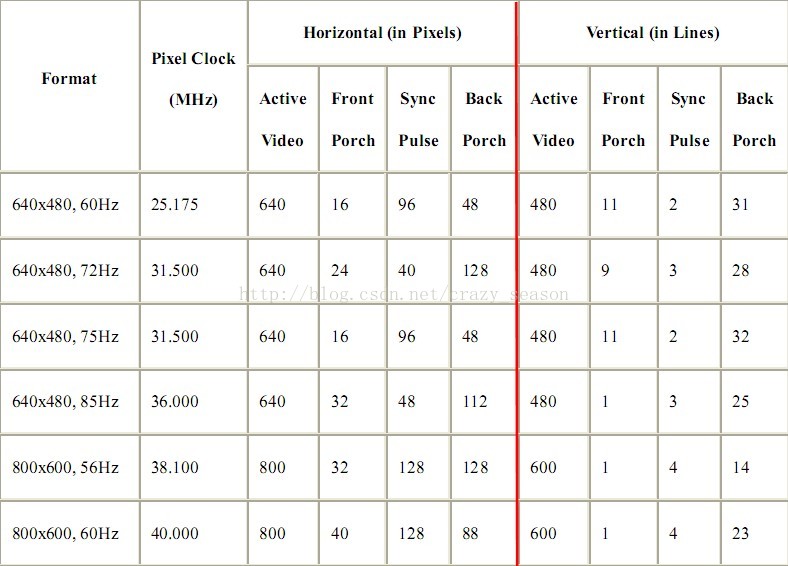

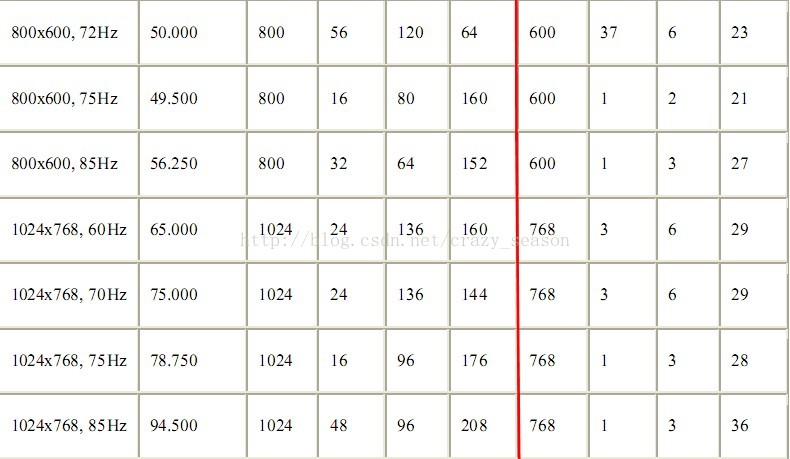

各个值的对照表。

这次实验采用的是640x480@60hz,计算其他像素就是800x524,需要的频率为800*524*60大约为25M,开发板提供的只有50M,所以可以利用分频为25M。如果设置其他分辨率可以用FPGA内部的PLL来获得所需频率。

由于采用DE2-115开发板作为vga输出实验,接口是需要进行DA转换的,芯片为ADV7123,需要注意的是VGA_CLK,VGA_BLANK_N和VGA_SYNC_N;VGA_CLK为上面分频时钟输送给DA转换芯片,而VGA_BLANK_N为无效时间,(低电平有效),VGA_SYNC_N暂时用不到sopc所以设置为低电平也是(低电平有效)。

2.程序代如下(彩条显示):

module vga(

clk,rst_n,

vga_r,vga_g,vga_b,clk_vga,

hsync

本文介绍了如何使用FPGA设计实现640x480分辨率的VGA显示,包括VGA的时序原理、DE2-115开发板上的接口配置,以及通过ADV7123芯片进行DA转换。程序代码展示了如何生成彩条显示,并详细解释了同步信号的生成和像素颜色的设定。

本文介绍了如何使用FPGA设计实现640x480分辨率的VGA显示,包括VGA的时序原理、DE2-115开发板上的接口配置,以及通过ADV7123芯片进行DA转换。程序代码展示了如何生成彩条显示,并详细解释了同步信号的生成和像素颜色的设定。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9391

9391

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?