使用一个拨码开关控制LED灯的亮灭

本部分代码已经上传到github上:linxunxr/VerilogStudy (github.com),文件夹为001,仅上传了工程文件、设计文件和约束文件

任务前的准备

- 在开始实验之前我们需要完成Vivado软件的安装,此方面可直接去官网下载响应的版本安装即可,个人使用的是2022.2的版本。vivado的官网下载链接:下载 (xilinx.com)

- 在完成软件的安装之后,我们就需要来创建项目。

创建工程

- 打开软件

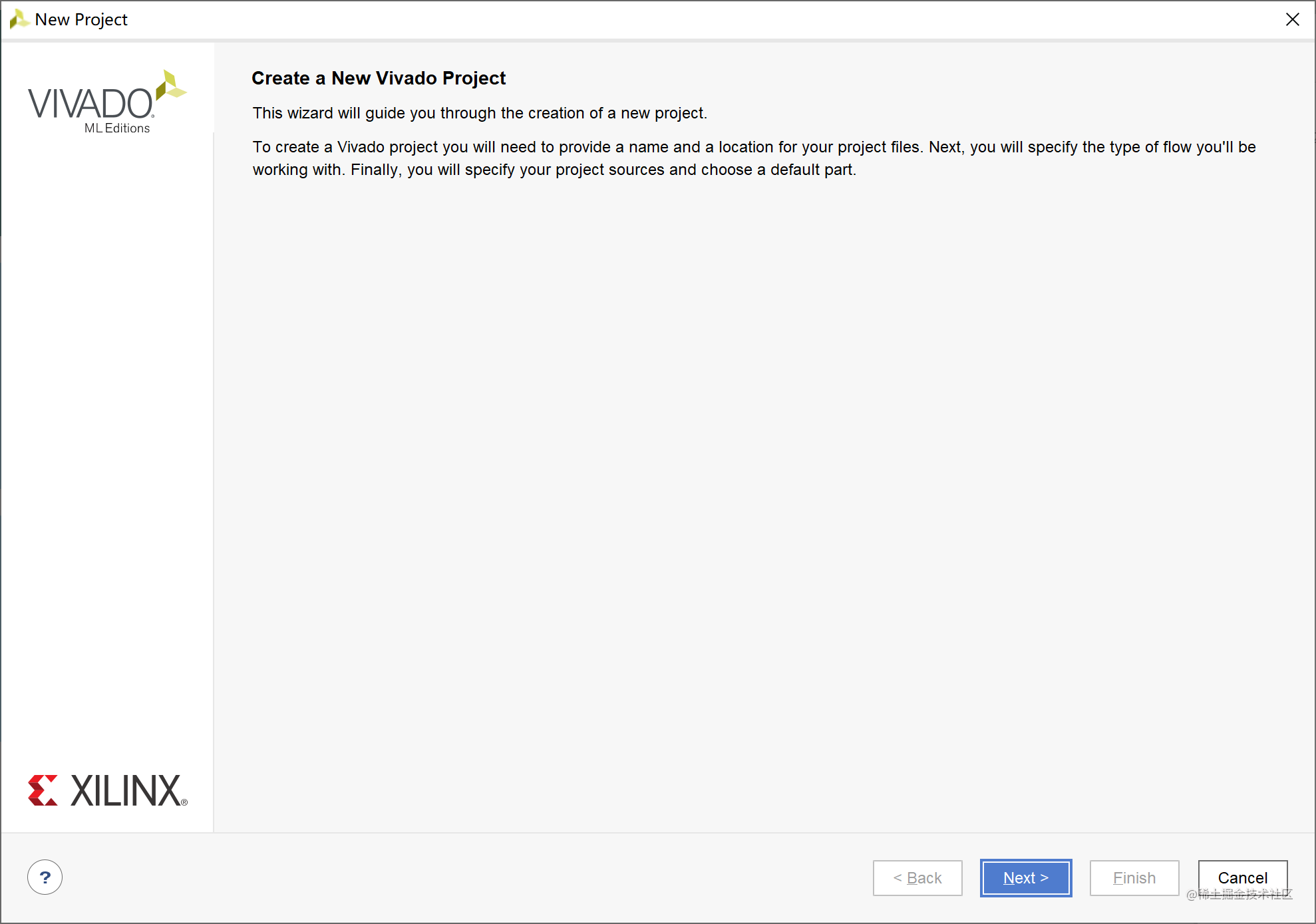

- 点击创建工程

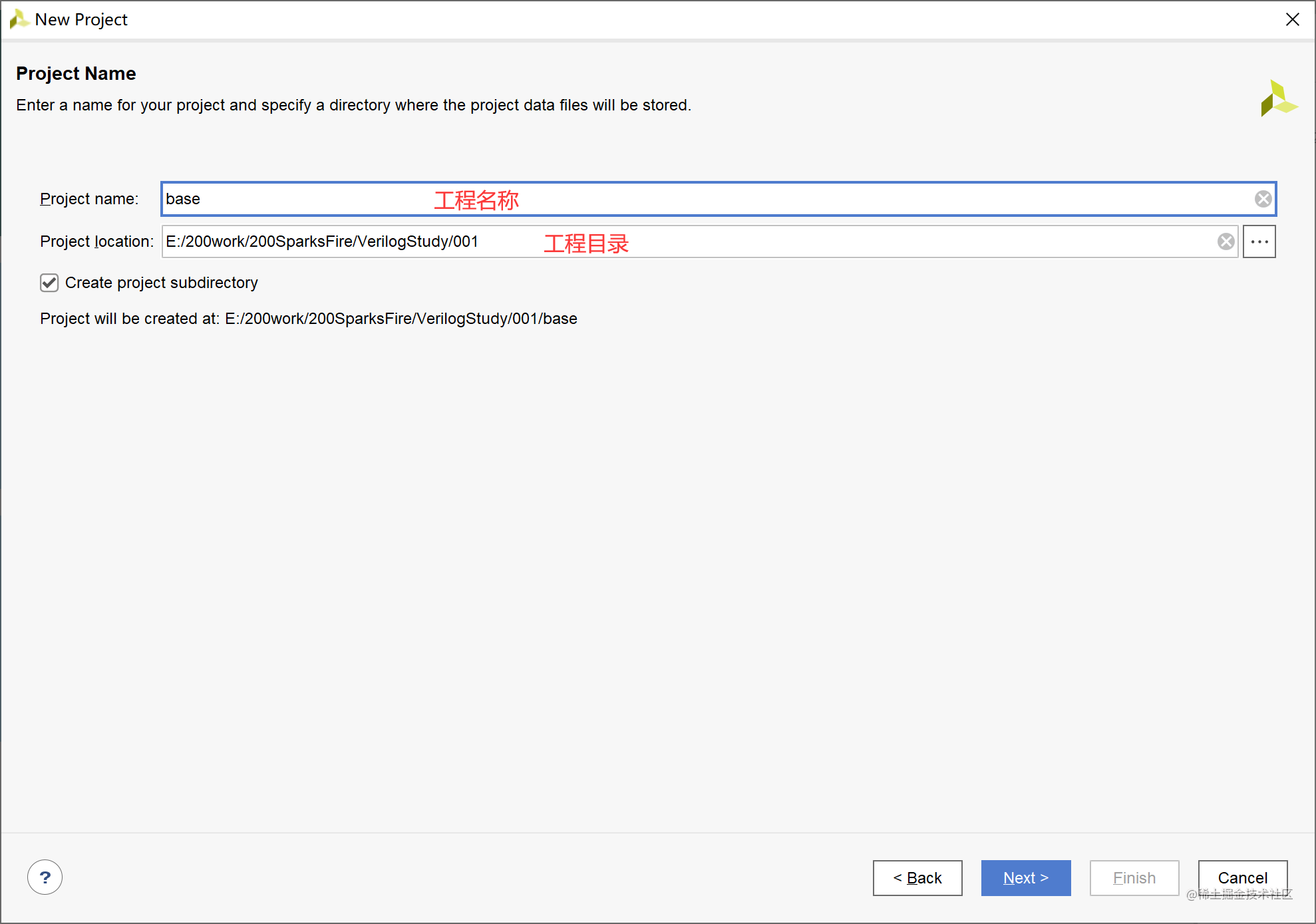

- 点击Next,设置工程名称和工程目录

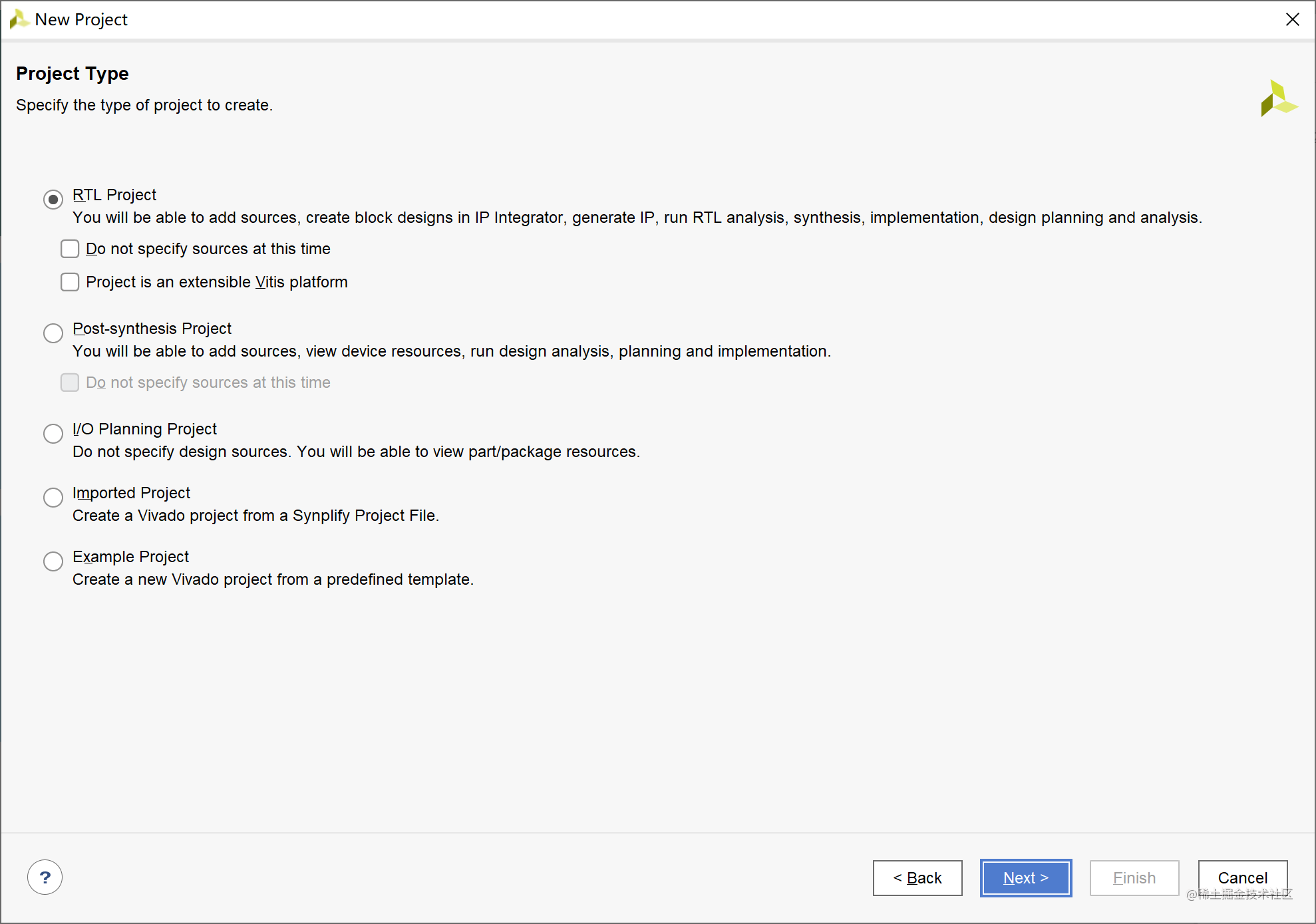

- 点击Next,选择RTL Project

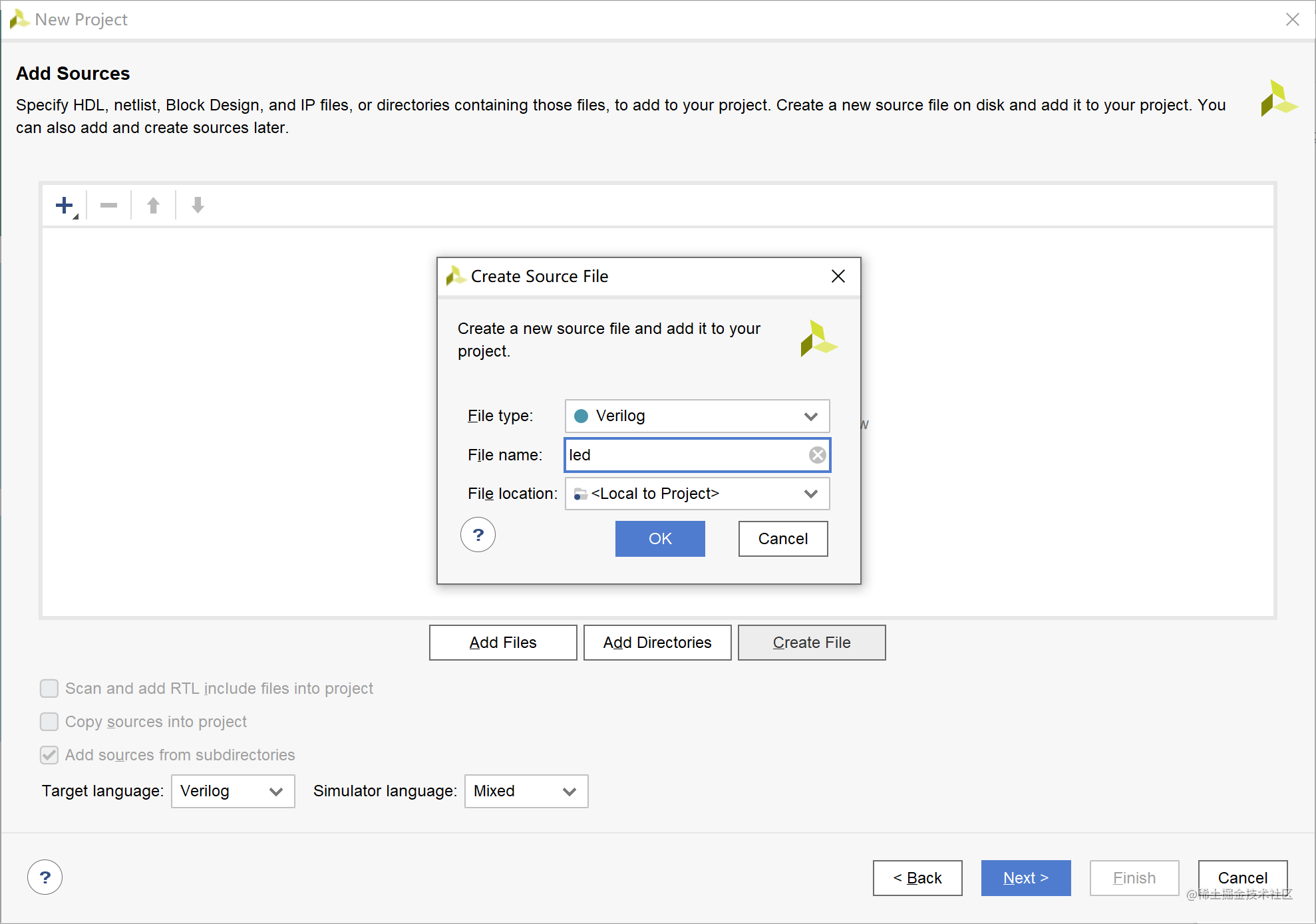

- 添加或创建设计源文件,亦可不创建,在后续进行创建,本次再次点击创建文件

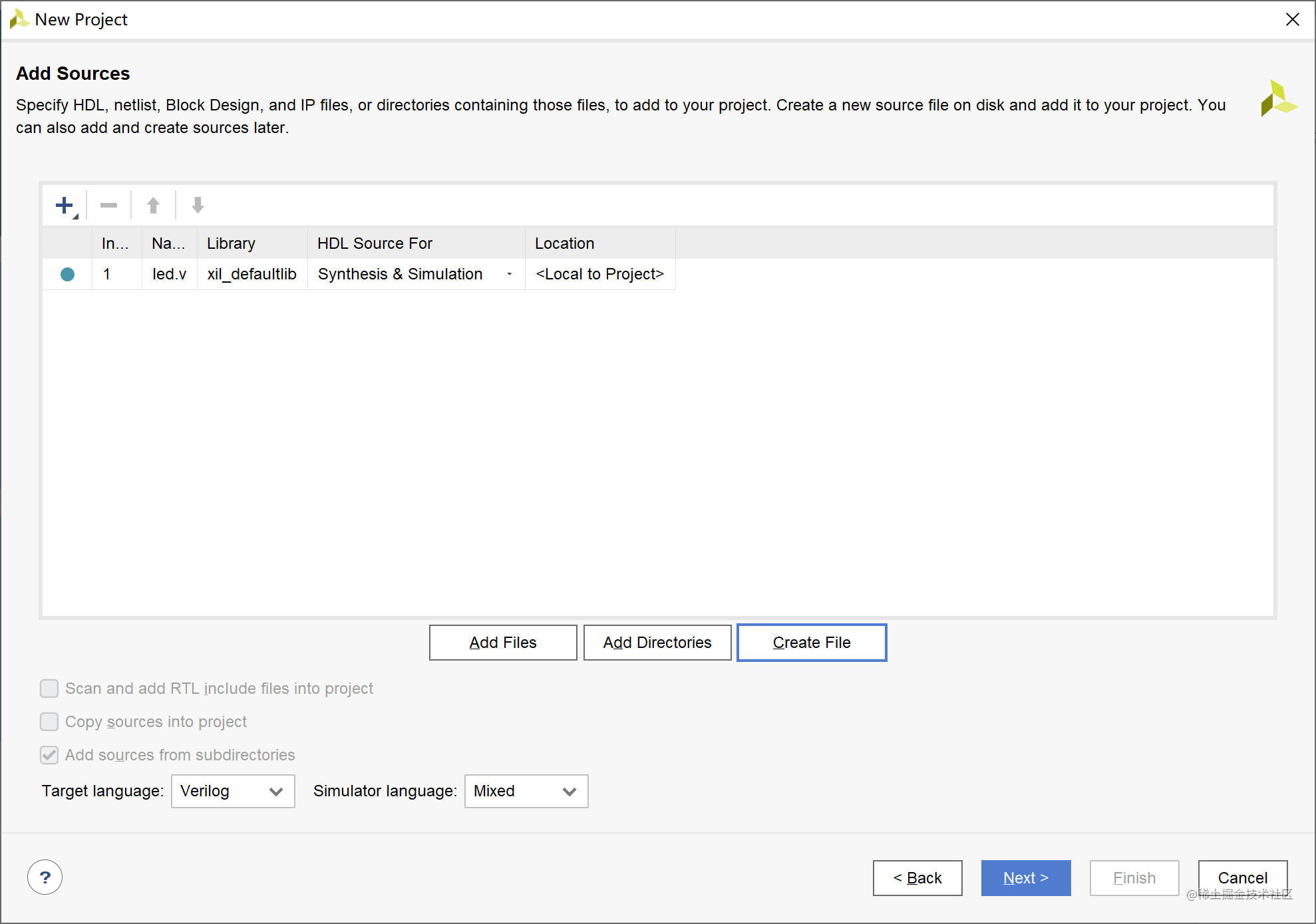

- 创建完成后即可在列表查看到该文件

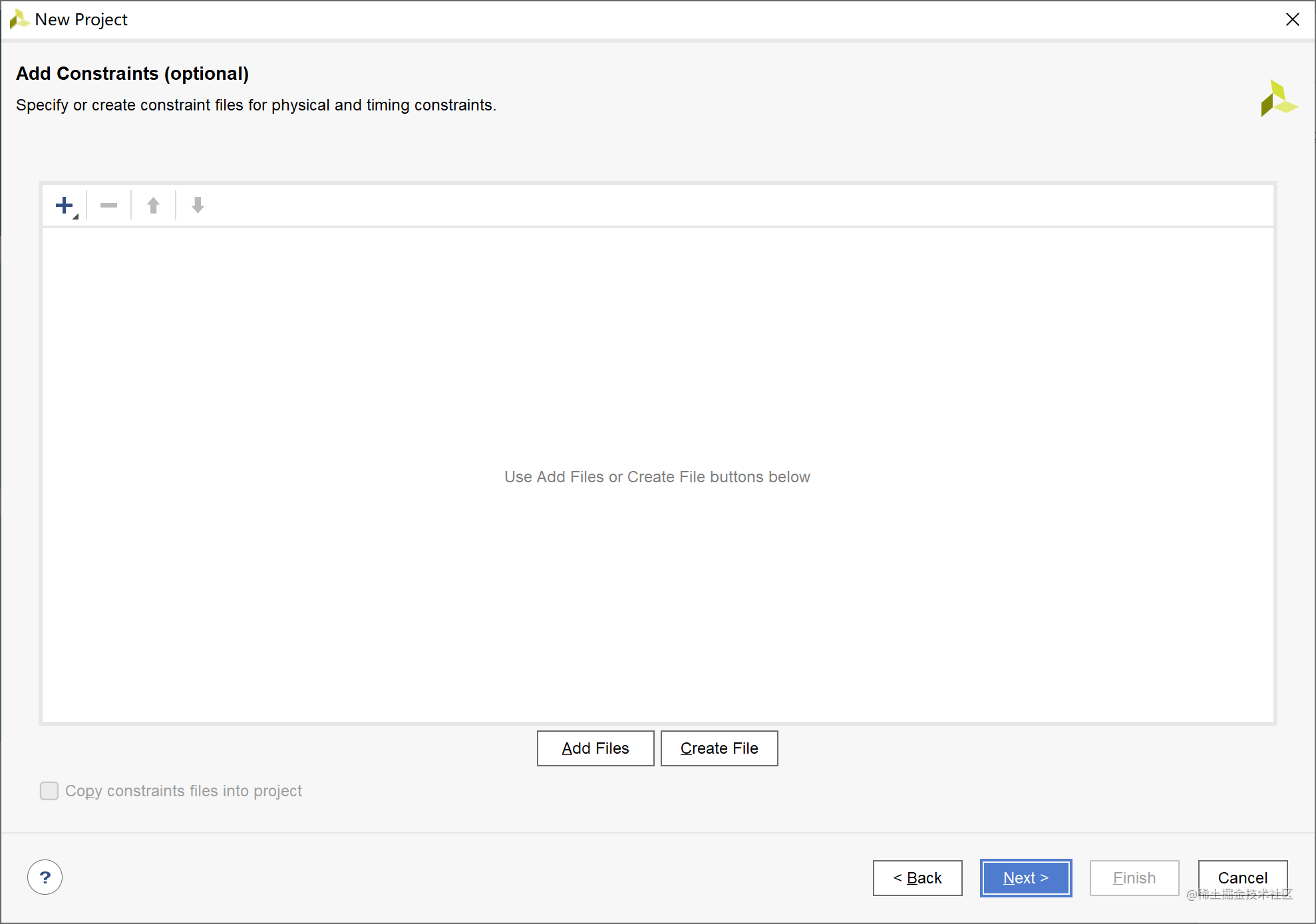

- 点击Next进入约束文件的添加或创建,亦可不创建,一般不在这个界面创建约束文件,因此直接Next

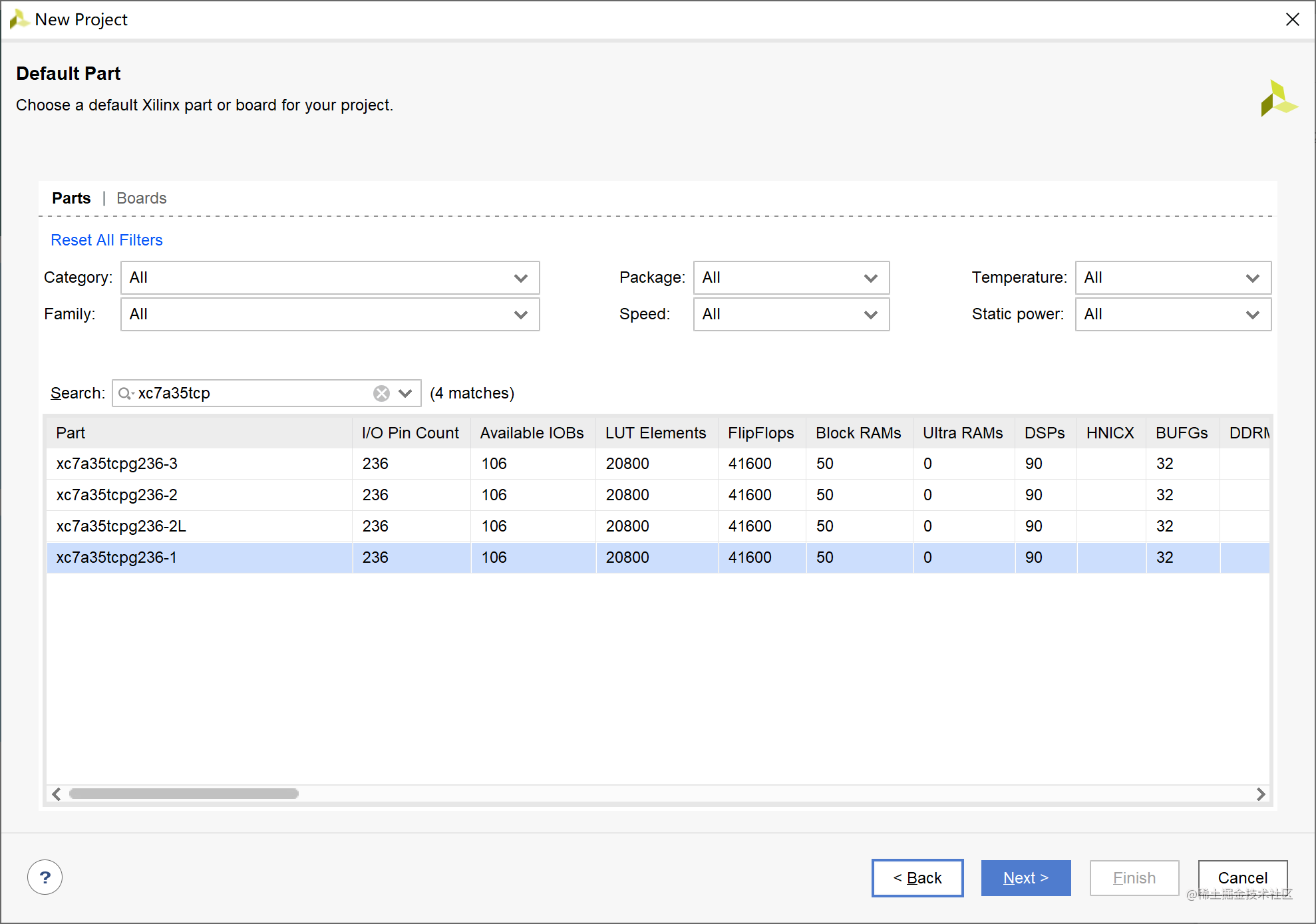

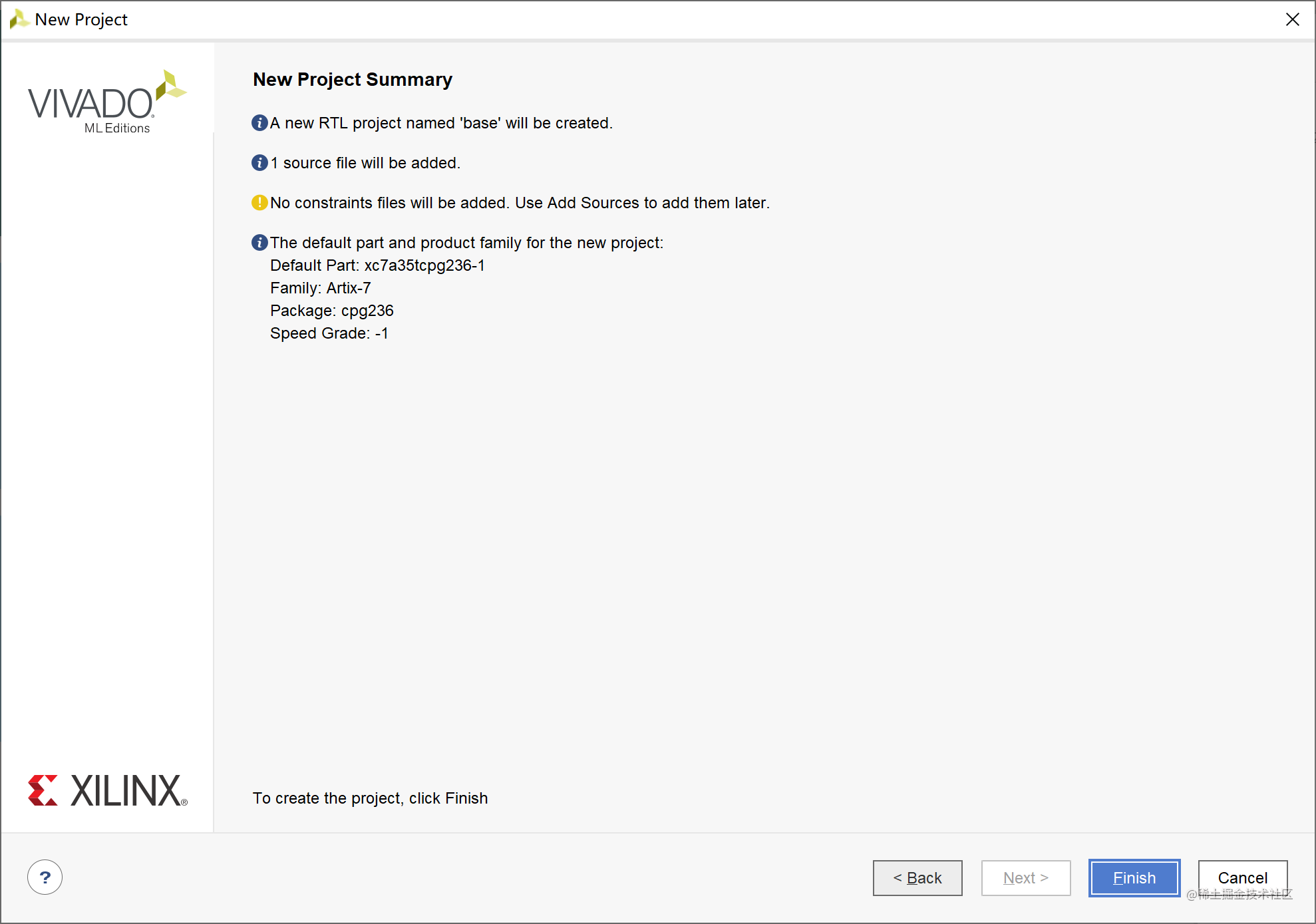

- 接下来进入选芯片的界面,根据Xilinx提供的信息可知,basys3的开发板芯片型号为:xc7a35tcpg236-1,因此在芯片库中搜索到对应芯片并选择

- 点击Next即进入工程创建的最后界面,在此界面可以确认之前的信息

- 点击Finish即进入创建工程,等待创建完成

进入工程界面

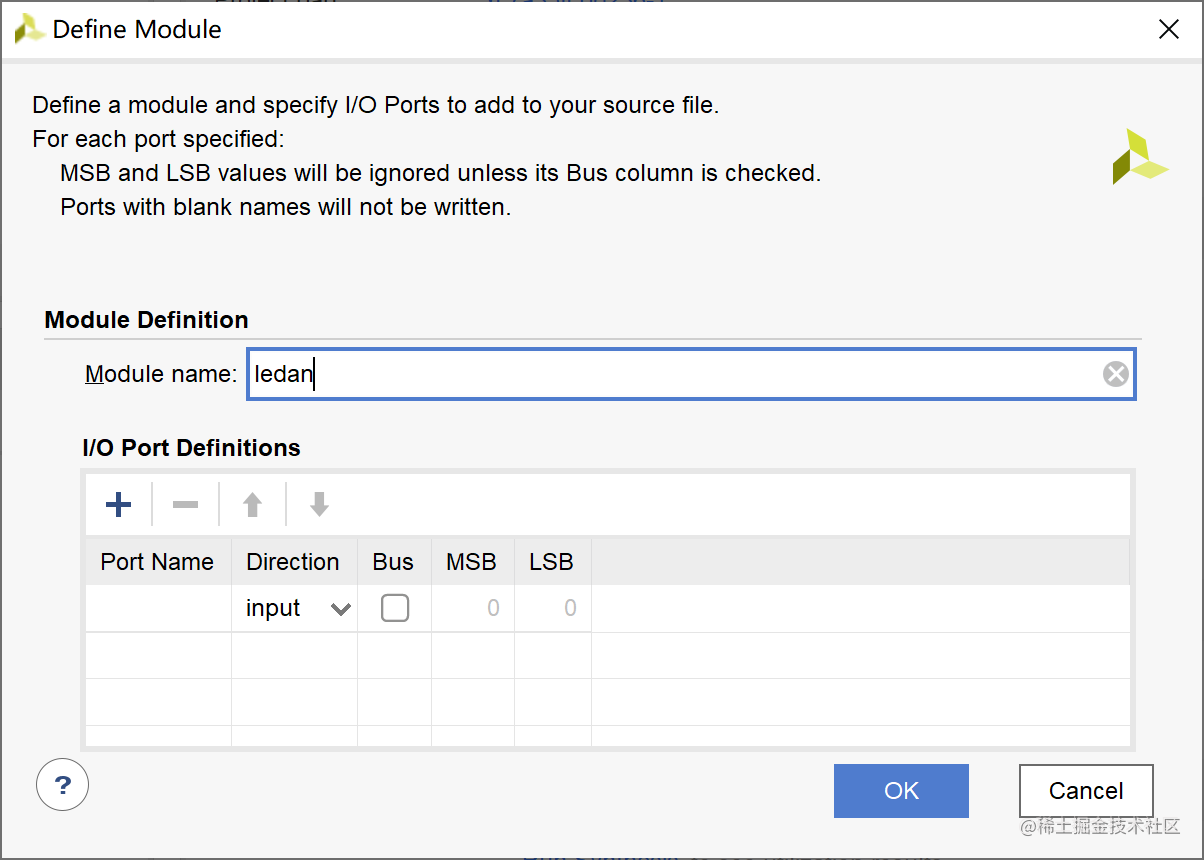

进入工程界面 - 由于我们在工程创建的同时创建了源文件,但是并没有定义模块,因此在进入工程之后会弹出让我们定义模块的界面,此处直接取消就可以

编写代码

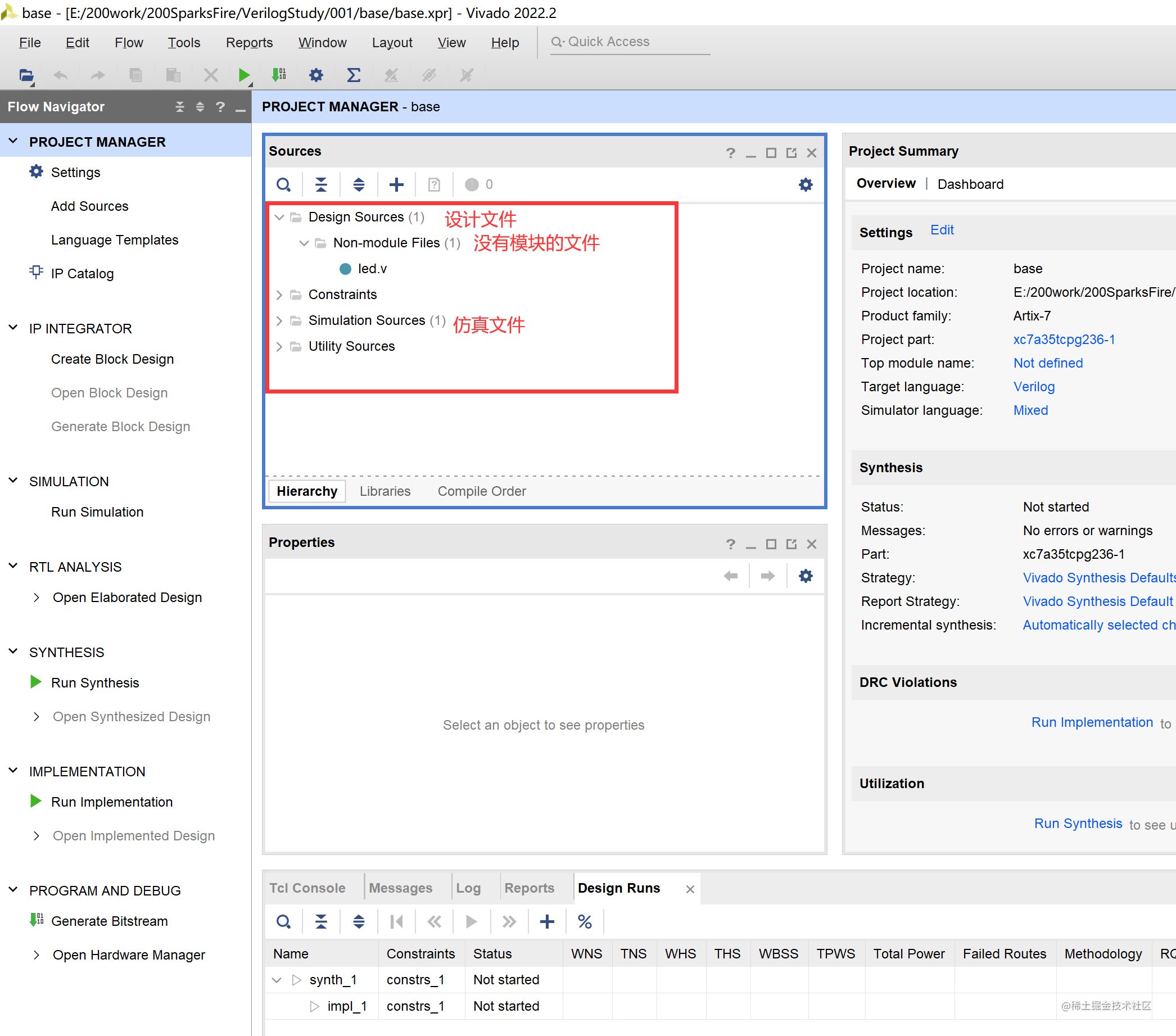

- 我们首先需要了解Vivado的资源界面,Vivado的资源界面分为四个文件夹,目前我们需要了解的就是第一个、第二个和第三个文件夹。第一个是设计文件,相当于C语言中的源文件,在这里我们需要用verilog代码来描述我们需要使用的数字电路和系统;第二个是约束文件,如将我们编写的硬件代码下载到板子上还需要找到板子上的引脚与我们代码里的端口进行对应;第三个是仿真文件,相当于C语言中针对某一功能而写的测试代码,这部分我们下一次会用到。

- 接下来,点开led.v就需要写verilog代码,我们就写出了下面这个最为简单的代码,将输入的拨码开关值赋值给led并输出。

module led(

input sw,

output led

);

assign led = sw;

endmodule

但是在读懂上述代码之前,我们需要先了解一个概念,就是模块。我们知道,verilog的代码编写理念是自顶向下设计,即我们需要将我们拿到的任务进行模块划分,如下图

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1879

1879

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?