一.实验目的

1. 掌握数字电路搭建及万用表的使用方法。

2. 掌握基本门电路逻辑功能的测试方法。

3. 了解TTL和CMOS器件的使用特点

二.实验预习要求

1. 复习基本门电路的逻辑功能及逻辑函数表达式。

2. 复习实验的各芯片结构和管脚图,见下文附图。

3. 复习实验所用的相关原理。

三、实验仪器及器件

面包板、稳压电源及导线若干

万用表 1台

1KΩ电阻 4只

74LS00 二输入端四与非门 1片

74LS86 二输入端四异或门 1片

CD4001 二输入端四或非门 1片

74LS125 三态门 1片

发光二极管 1只

(注意:发光二极管较长引脚为正极,电路中发光二极管必须串联1k或2k的限流电阻,否则电流过大会烧坏。)

DIP拨码开关 1只

(拨码开关作为电平开关为输入信号提供高低电平,其电路接法见后面的图示。)

基本门电路结构图与管脚图如图:

此图中的门逻辑符号是国外流行图形符号,也是Multisim软件中使用的符号。请参见文件“基本逻辑门电路图形符号.pdf”。

1.74LS00 四2输入与非门

2.74LS86 四2输入异或门

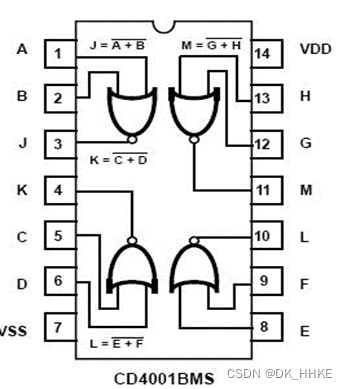

3. CD4001 四2输入端或非门 (CMOS门)

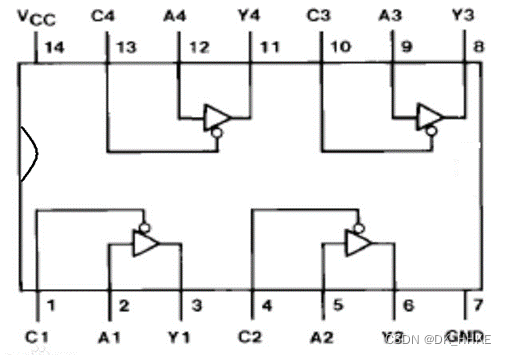

4.74LS125 三态门

注意:A是输入端,C是使能端(),Y是输出端。

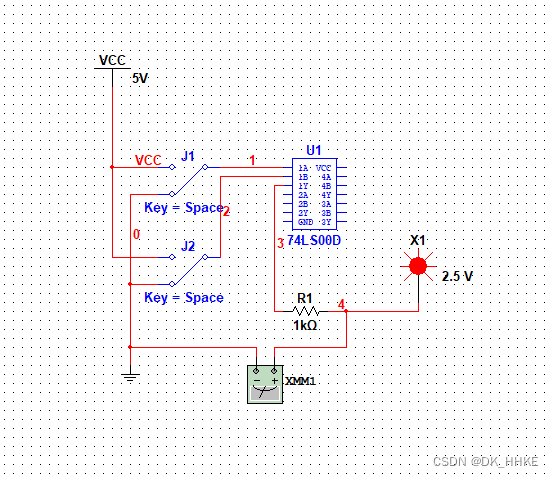

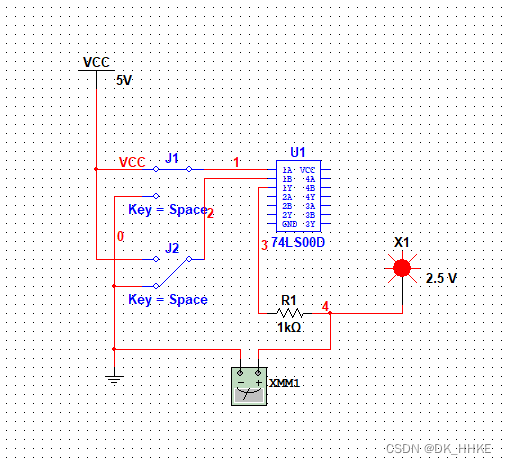

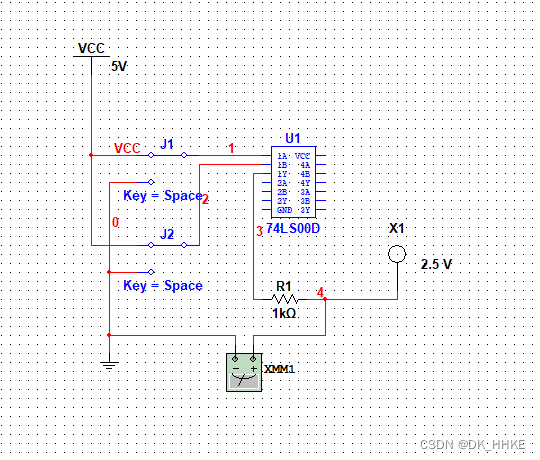

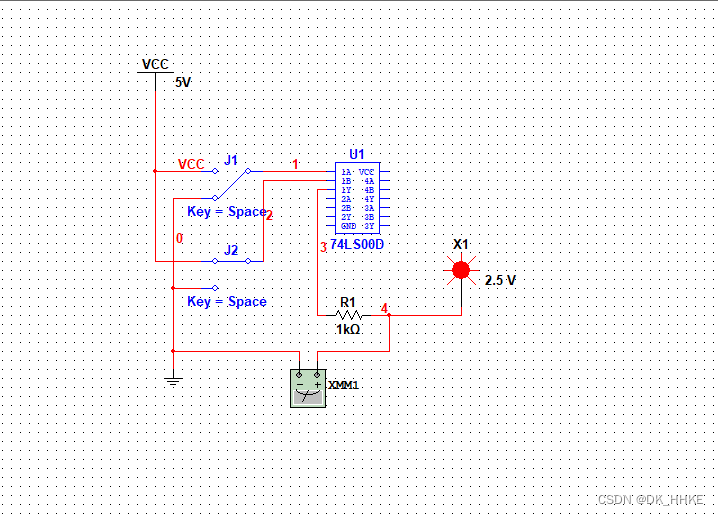

比如已74LS00D为例,注意小灯泡和万用表的变化进行记录(74LS86和CD4001和三态门可以类似于如此,但是要输入端和输出端的位置)

TTL三态输出门是一种特殊的门电路。它的输出端除了通常的 高电平、低电平两种状态外(这两种状态均低阻状态),还有第 三种输出状态——高阻状态。处于高阻状态时,电路与负载之间 相当于开路。三态输出门按逻辑功能及控制方式来分有各种不同 类型。本实验所用三态门的型号是74 LS125,它有一个控制端(又 称禁止端或使能端)Ē,Ē=0为正常工作状态,实现Y=A的逻辑功 能;Ē=1为禁止状态,输出Y呈现高阻状态。三态电路的主要用途 之一是实现总线传输,即用一个传输通道(称总线)以选通方式 传送多路信息

6700

6700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?