仿真工具:Cadence virtuoso6.17

仿真工艺:simc18mmrf

仿真实例:简单放大器

四、噪声仿真

上一节:简单放大器的直流仿真

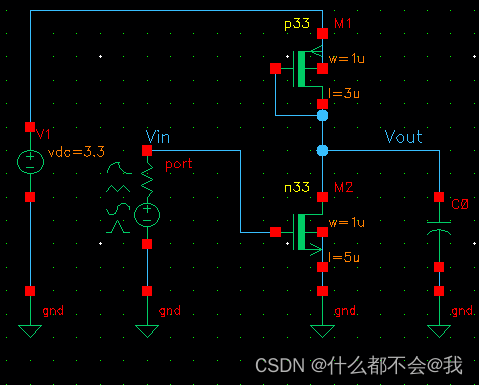

从“simc18mmrf”中调用NMOS n33,按键盘中的Q键,在属性lu/5u;重复上述操作,调用PMOS p33,并分配宽长比为1u/3u。从“analogLib”中调用一个理想电容cap,并设置电容值为1pF 。

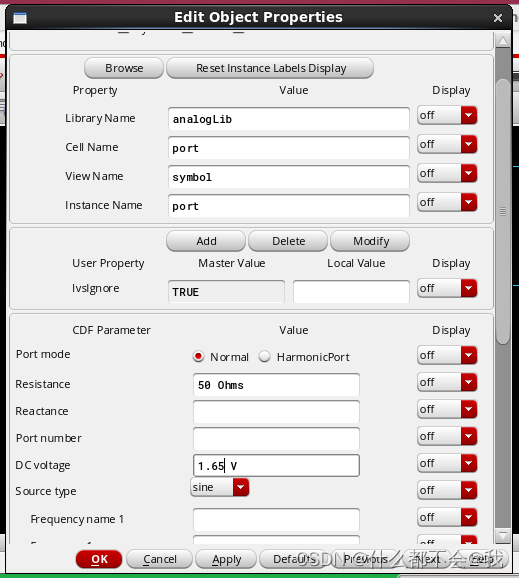

电源电压“vdd”为3.3V,地“gnd”为0V。从“analogLib”中调用“port”,并为“port”设置属性,如图所示,在“DC voltage”中输入直流偏置电压1.65V。

原理图如下

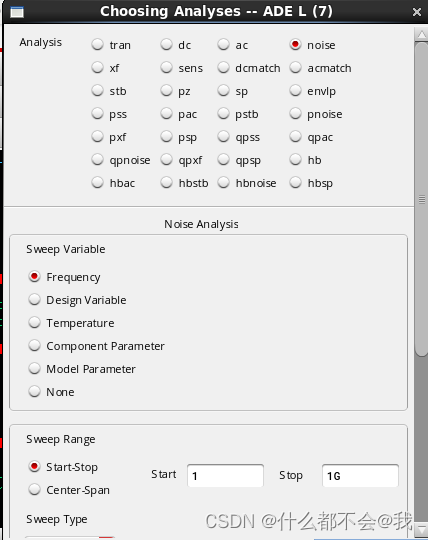

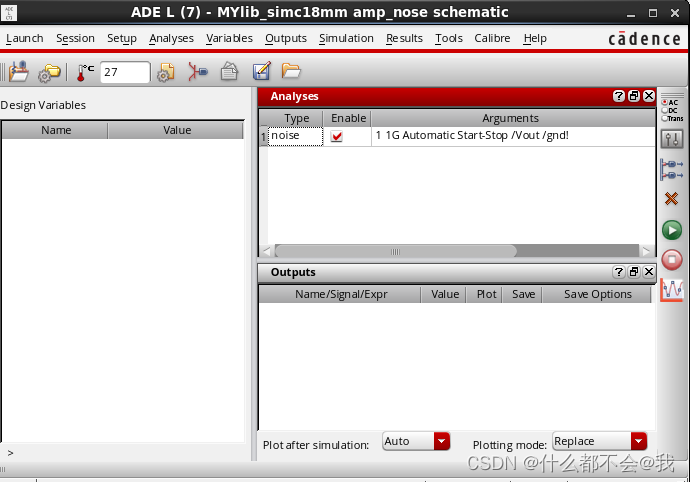

Analyses仿真设置为噪声仿真,

在“Sweep Variable”中选择“Frequency”

在“Sweep Range”栏中输入1 , 1G

在“Sweep Type”中选择“Automatic”形式

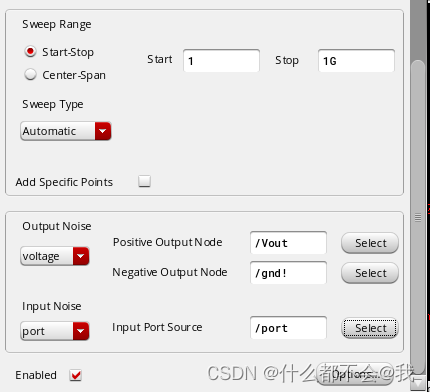

在“Output Noise”中选择采用“voltage”,

在“Positive OutputNode”栏单击“Select”按钮,用箭头在电路图中选择放大器输出“vout”

在“Negative Output Node”栏选择地“gnda”。

在“Input Noise”中选择采用“port",并用箭头在电路图中选择放大器输入“port”

完成设置后如图所示。

点击运行,开始仿真

仿真结束后,点击“Results”“Direct Plot”→“Main Form”命令,

在噪声仿真输出选择对话框中仿真选项选择如图所示,

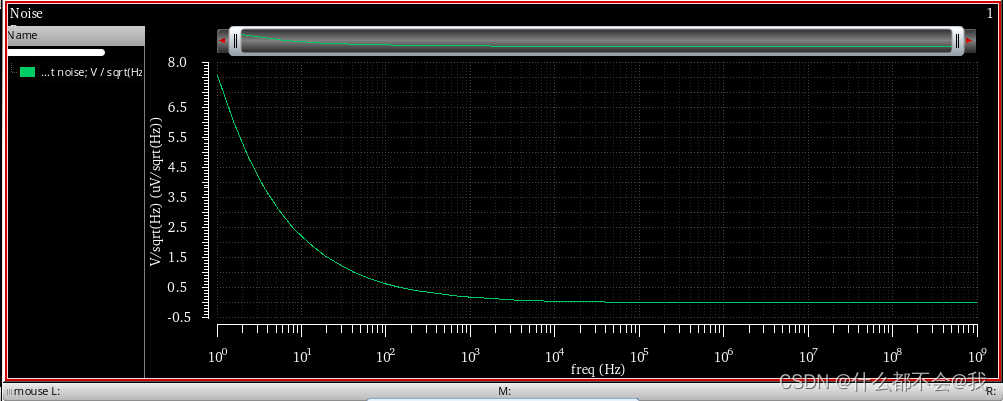

输出噪声波形如图所示,可见放大器噪声随频率上升而下降,在低频段占主导地位的主要是1/f噪声,在高频段占主导地位的主要是晶体管热噪声。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?